Fターム[5F004EB01]の内容

半導体のドライエッチング (64,834) | エッチング対象部の機能 (2,366) | コンタクトホール (584)

Fターム[5F004EB01]に分類される特許

81 - 100 / 584

半導体装置及びその製造方法

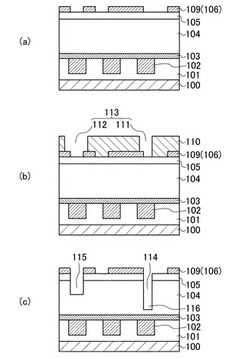

【課題】製造コストの増加および歩留まりを低下させることなく、配線抵抗を下げることのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板100上の絶縁膜104上にマスク材料膜106を形成した後、第1のトレンチ形成用開口と第2のトレンチ形成用開口とを有するマスクパターン109をマスク材料膜106に形成する工程と、マスク材料膜106上に、第1のトレンチ形成用開口を露出する第3のトレンチ形成用開口112を有し、且つ、第2のトレンチ形成用開口部を覆うレジストパターン113を形成する工程と、レジストパターン113及びマスクパターン109を用いて、絶縁膜104内に第1のトレンチ115を形成する工程と、レジストパターン113を除去した後、マスクパターン109を用いて、絶縁膜104内に第2のトレンチを形成する工程とを備えている。

(もっと読む)

半導体装置の製造方法及びプラズマエッチング装置

【課題】微細なパターンを精度良く均一に、かつ、高選択比で形成することのできる半導体装置の製造方法及びプラズマエッチング装置を提供する。

【解決手段】処理チャンバー内に混合ガスからなる処理ガスを供給し、かつ複数種のガスのうち少なくとも1種のガスの流量を第1の時間中第1の流量とする第1工程と、第2の時間中前記第1の流量とは異なる流量の第2流量とする第2工程とからなる1サイクルの工程を、プラズマを途中で消すことなく連続的に少なくとも3回以上繰り返して行い、第1の時間及び第2の時間は、1秒以上15秒以下、第1工程における処理ガスの総流量と、第2工程における前記処理ガスの総流量は、同一若しくは異なる場合は、総流量の差が多い方の総流量の10%以下であり、第1工程と第2工程のいずれにおいても被エッチング膜のエッチングを進行させるガスを処理ガス中に含む半導体装置の製造方法。

(もっと読む)

ドライエッチング方法

【課題】コストの上昇を招くことなく、より安定した状態でInPの層がドライエッチング法によりエッチングできるようにする。

【解決手段】塩素ガスを用いたドライエッチング法によりマスクパターン106をマスクとして基板101を選択的にエッチングすることで、基板101にビアホール(開口パターン)107を形成する。例えば、温度条件を200℃程度とし、塩素ガスを用いた反応性イオンエッチング法によりエッチングすればよい。

(もっと読む)

パターン形成方法および含浸装置

【課題】本発明は、アスペクト比の大きな微細パターンを安定して形成できるパターン形成方法と、その方法に使用される含浸装置を提供することを目的とする。

【解決手段】被加工部材3上に所定のパターンが形成されたエッチングマスク9を形成する工程と、前記エッチングマスク9に所定の物質12を含浸させる工程と、前記所定の物質12を含浸した前記エッチングマスク9を用い、前記被加工部材3をパターニングする工程と、を備えたことを特徴とするパターン形成方法が提供される。

(もっと読む)

基板処理方法及び記憶媒体

【課題】低誘電率膜であるSiCOH膜とCu配線との夫々の露出面に炭素の脱落したダメージ層及び酸化物が夫々形成された基板に対してダメージ層を回復させ且つ酸化物を還元すること。

【解決手段】SiCOHを含む層間絶縁膜4とCuを含む配線2との夫々の露出面に炭素の脱落したダメージ層15及び酸フッ化層16が夫々形成されたウエハWに対して、H2ガスの供給とシリコン及び炭素を含むTMSDMAガスの供給とを同一の処理容器51においてこの順番で連続して行うことによって、酸フッ化層16の還元処理及びダメージ層15の回復処理を行う。

(もっと読む)

エッチング方法、エッチング装置及びリング部材

【課題】処理ガスをプラズマ化して基板上の被エッチング膜をドライエッチングするにあたり、基板に対して均一性高くエッチング処理を行うことができる技術を提供すること。

【解決手段】処理容器内に基板を搬入して載置台に載置する工程と、少なくとも表面部の主成分が基板の被エッチング膜の主成分と同じ材質であるリング部材を基板を囲むように配置した状態で、基板に対向するガス供給部から処理ガスをシャワー状に吐出すると共に処理ガスをプラズマ化して被エッチング膜をエッチングする工程と、前記処理容器内を排気路を介して真空引きする工程と、を含むようにエッチングを行う。それによって基板の周端部付近におけるプラズマの活性種の分布の偏りを抑える。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法

【課題】高周波電力の入力パワーに対して、プラズマ発生効率が良好で、エッチング速度が早く、スループットが高いプラズマ処理装置を提供することを目的とする。

【解決手段】処理物(6)をプラズマ室(33b)にセットし、誘導結合コイル(4)を誘電板(34)を隔ててプラズマ室(33b)に隣接して設け、誘導結合コイル(4)に高周波電力を印加してプラズマ室(33b)にプラズマを発生させて処理物(6)を処理する。コイル室(33a)の内部はプラズマが発生しない放電限界圧力に減圧されており、誘電板(34)の厚みを従来に比べて薄くでき、誘導結合コイル(4)で生成する電磁波の誘電板(34)での減衰を低減して、プラズマ発生の効率を向上させる。

(もっと読む)

ハードマスク材料

【課題】集積回路製造工程のバックエンドプロセス、およびフロントエンドプロセスにおいて利用することができる、高硬度、且つ低応力のハードマスク膜を提供する。

【解決手段】ハードマスク膜は、応力が約−600MPaから600MPaの範囲内であり、硬度は少なくとも約12Gpaである。ハードマスク膜は、PECVD処理チャンバにおいて、高密度化プラズマ後処理を複数回行うことによって、ドープ済または未ドープのシリコンカーバイドの副層を複数成膜することによって得られる。ハードマスク膜は、SixByCz、SixByNz、SixByCzNw、BxCy、およびBxNyから成る群から選択される高硬度のホウ素含有膜を含む。ハードマスク膜は、ゲルマニウム含有率が少なくとも約60原子パーセントと、ゲルマニウム含有率が高いGeNxハードマスク材料を含む。

(もっと読む)

マスクの製造方法、及び半導体装置の製造方法

【課題】開孔径が均一で開孔径の制御が容易な、微細化に適した開孔パターンを有するマスクを製造する。

【解決手段】第1及び第2のマスク層内に開孔を設ける。この後、第1のマスク層内の開孔の径よりも第2のマスク層内の開孔の径を、Xの量だけ大きくする。この後、第2のマスク層内の開孔内にマスク材料を形成することによって第2のマスク層内の開孔内に、Xの径の空洞部を形成する。この空洞部を開孔として有する第2のマスク層及びマスク材料を、マスクとして形成する。

(もっと読む)

ドライエッチングガス及びそれを用いたドライエッチング方法

【課題】半導体デバイスの製造プロセスにおいて、シリコン酸化膜、窒化シリコン膜、シリコン含有低誘電率膜等のシリコン含有膜のエッチング速度の低下を防ぎ、レジストや下地のシリコンなどに対して、選択的にエッチングすることができるドライエッチングガス及びそれを用いたエッチング方法を提供する。

【解決手段】CF3CF=CH2を含むドライエッチングガス。CF3CF=CH2の含有率は、流量比5〜100%であることが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に形成する溝の寸法を制御しやすい半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、デュアルダマシンのビアが形成された下側絶縁膜と、ビアを埋め下側絶縁膜上に延在しレジスト材料でできた樹脂膜と、樹脂膜上に形成された酸化シリコン膜と、酸化シリコン膜上方に形成されたレジストパターンとを有するエッチング対象物に対し、レジストパターンをマスクとし、C4F6、CHF3、C4F8、及びCH3Fから選択されたガスの使用量、及び、O2及びArから選択されたガスの使用量を定めるレシピを複数含みエッチングチャンバの制御装置に記憶されたレシピ群から選択されたレシピで、酸化シリコン膜をエッチングして、ハードマスクを形成する工程と、ハードマスクを用い、樹脂膜及び下側絶縁膜をエッチングして、デュアルダマシンのトレンチを形成する工程とを有する。

(もっと読む)

モリブデン系金属膜上の絶縁膜のドライエッチング方法および薄膜トランジスタパネルの製造方法

【課題】モリブデン系金属膜上の絶縁膜をドライエッチングする際に、選択比を比較的大きくする事ができる方法を提供する。

【解決手段】ドライエッチングにより、レジスト膜45の開口部46に対応する部分つまりソース電極9上におけるオーバーコート膜13にコンタクトホール14を形成し、また同時に、レジスト膜45の開口部47に対応する部分つまり金属膜21a上におけるオーバーコート膜13およびゲート絶縁膜4にコンタクトホール22を形成し、さらに同時に、レジスト膜45の開口部48に対応する部分つまり金属膜31a上におけるオーバーコート膜13にコンタクトホール32も形成する場合、エッチングガスとしてフッ素系ガス(SF6、CF4)、酸素ガスおよび窒素ガスからなる混合ガスを用いる事で窒化シリコン等からなるオーバーコート膜13とモリブデン系金属からなる金属膜31aとの選択比を大きくする。

(もっと読む)

エッチングガス

【課題】

本発明は、対レジスト選択比や加工形状のエッチング性能に優れるだけでなく、入手が容易で、環境に負荷をかけるCF4を実質的に副生しない新規なエッチングガスを提供する。

【解決手段】

CHF2COFを含んでなるエッチングガスであって、O2、O3、CO、CO2、F2、NF3、Cl2、Br2、I2、XFn(式中、XはCl、IまたはBrを表し、nは1≦n≦5の整数を表す。)、CH4、CH3F、CH2F2、CHF3、N2、He、Ar、Ne、Krなど、または、CH4、C2H2,C2H4,C2H6、C3H4、C3H6、C3H8、HI、HBr、HCl、CO、NO、NH3、H2など、または、CH4、CH3F、CH2F2、CHF3の中から選ばれた少なくとも1種のガスを添加物として含むエッチングガス。

(もっと読む)

半導体装置及びその製造方法

【課題】配線及び半導体素子等を自由に配置できない領域を減少させる。

【解決手段】半導体装置は、半導体素子3が形成されている第1面及び第1面とは反対側の第2面を有する半導体基板1と、半導体基板1の上に形成され、且つ、第1のビア7を有する層間絶縁膜と、半導体基板1内に形成され、且つ、第1のビア7と接続する第2のビア13とを有し、第1のビア7の径は、第2のビア13の径よりも小さいことを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】 デュアルダマシンプロセスを同一チャンバ内で行っても、再現性よくビアホールを貫通させる技術が望まれる。

【解決手段】 層間絶縁膜上の第1のマスク膜及び層間絶縁膜に、層間絶縁膜の厚さ方向の途中まで達するビアホールを形成する。第1のマスク膜の上に、下層レジスト膜を形成し、その上に、配線溝に対応する開口を有する第2のマスク膜を形成する。チャンバ内において、O2とCOとのプラズマを用い、下層レジスト膜をエッチングするとともに、ビアホール内の一部には、下層レジスト膜を残す。下層レジスト膜の開口の平面形状が転写された開口を、第1のマスク膜に形成するとともに、下層レジスト膜を除去し、ビアホールをさらに掘り下げて、下層配線を露出させる。層間絶縁膜を厚さ方向の途中までエッチングして配線溝を形成する。配線溝及び前記ビアホール内を、導電部材で埋め込む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造工程の簡略化および製造時間短縮を目的とする、メモリセルと周辺回路を備える半導体装置と製造方法を提供する。

【解決手段】トランジスタ形成層30上に、内部に配線10bを備え、かつ、表面に容量パッド14a,14bを有する絶縁層32を形成する工程と、絶縁層32を層間絶縁膜16で覆い、層間絶縁膜16を貫通する第一のホール16aと、第一のホール16aよりも大きい直径を有する第二のホール16bおよび第三のホール16cを、それぞれメモリセル部と周辺回路部に同時に形成する工程と、各ホール内を覆う下部電極18と容量絶縁膜19と上部電極20と容量サポート21を形成することにより第一のホール16aを充填するとともに、第二のホール16bと第三のホール16c内側に空洞を形成する工程と、空洞内に、配線10bと容量パッド14bにそれぞれ接続するコンタクト16d,16eを形成する工程と、を具備している。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法、ならびにコンピュータ読み取り可能な記憶媒体

【課題】レジスト層等の有機マスク層の耐プラズマ性を高く維持して高選択比でエッチングすることができ、また、電極への堆積物の付着を有効に解消することができ、さらにプラズマ密度のコントロールが可能なプラズマエッチング装置を提供すること。

【解決手段】チャンバ10に互いに対向して配置される上部電極34およびウエハ支持用の下部電極16を有し、下部電極16に相対的に周波数の高い第1の高周波電力を印加する第1の高周波電源89および相対的に周波数の低い第2の高周波電力を印加する第2の高周波電源90を接続し、上部電極34に可変直流電源50を接続し、チャンバ10内に処理ガスを供給してプラズマ化し、プラズマエッチングを行う。上部電極34に印加された直流電源50からの直流電圧に基づく電流をプラズマを介して逃がすために、常時接地されている導電性部材91を設ける。

(もっと読む)

半導体装置の製造方法

【課題】スペーサーを形成すべき凸部の相互間隔、溝の幅、又は孔の径が小さい場合に、基板保護膜を用いる必要がなく、かつノッチを生じさせずにスペーサーを形成する。

【解決手段】スペーサーを形成する時の異方性エッチングにおいて、「1−(異方性エッチングおける第2スペーサー形成膜5の垂直方向のエッチングレートに対する水平方向のエッチングレートの比)」を異方性度と定義し、「(第1スペーサー形成膜4の膜厚T1−第2スペーサー形成膜5の膜厚T2)/(第1スペーサー形成膜4の膜厚T1)」を第1スペーサー形成膜4の第2スペーサー形成膜5に対する膜厚増分率と定義した時に、第2スペーサー形成膜5の垂直方向のエッチングレートを第1スペーサー形成膜4の垂直方向のエッチングレートより小さく、かつ第1スペーサー形成膜4の垂直方向のエッチングレートに異方性度と膜厚増分率のうち小さい方を乗じた値より大きいエッチング条件にする。

(もっと読む)

貫通孔形成方法

【課題】プラズマエッチングにより基板に貫通孔を形成する方法を提供すること。

【解決手段】基板上にマスクパターンを形成し、バイアス電力500〜1000Wの条件で、プラズマエッチングによりホール又はトレンチを形成する際に、ホール又はトレンチの底部周囲にマイクロトレンチを形成し、基板に貫通孔を形成する。

(もっと読む)

レジスト膜の除去方法および表示装置の製造方法

【課題】 CF4、CHF3、C2F6等の地球温暖化の一因となるガスを用いずに、レジスト膜を良好にアッシングするレジスト膜の除去方法、およびそれを用いた表示装置の製造方法を提供する。

【解決手段】 薄膜トランジスタ及び画素電極の上層側に成膜されたオーバーコート膜12から前記画素電極の少なくとも一部を露出させる際のマスクとして前記オーバーコート層12上にパターニングして形成されたレジスト膜28を、前記オーバーコート層12から前記画素電極の少なくとも一部を露出させた後にCOF2またはF2のいずれか一方と酸素ガスとを含む混合ガスを用いて除去する。

(もっと読む)

81 - 100 / 584

[ Back to top ]