Fターム[5F004EB01]の内容

半導体のドライエッチング (64,834) | エッチング対象部の機能 (2,366) | コンタクトホール (584)

Fターム[5F004EB01]に分類される特許

61 - 80 / 584

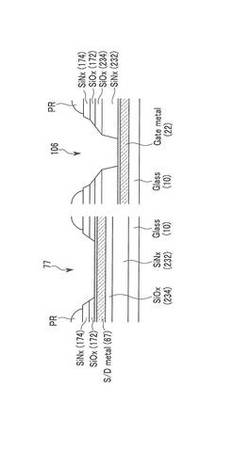

薄膜トランジスタ表示板及びその製造方法

【課題】高い電荷移動度を有し、大面積表示装置に対して均一な電気的特性を得ることができる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】絶縁基板上に形成されたゲート電極と、前記ゲート電極上に形成されたSiNxから構成された第1ゲート絶縁膜と、前記第1ゲート絶縁膜の上に形成されたSiOxから構成された第2ゲート絶縁膜と、前記ゲート電極と重畳するように形成され、チャネル部を有する酸化物半導体層と、前記酸化物半導体層及び前記ゲート電極の上部に形成されたSiOxから構成された保護膜とを含み、前記保護膜はドレイン電極拡張部を露出するコンタクトホールを含む。ここで、前記コンタクトホールは、ドレイン電極拡張部を直接的に露出する部分の保護膜が、その上部の保護膜よりさらに狭い領域を占める形状を有する。

(もっと読む)

半導体装置及び製造方法

【課題】少ない層間接続プロセス工程数で、コンタクト部分の面積を小さくすることのできる半導体装置及び製造方法を提供する。

【解決手段】多層導体配線10は、スルーホール15は、導体13の一部は、ひさし部13Cとしてスルーホール15の内側に露出する。そして、スルーホール15のスルーホール用孔の内側に埋め込まれた埋め込み金属16とひさし部13Cとで、側面コンタクト構造を形成することができる。

(もっと読む)

半導体装置

【課題】シリコン基板裏面をソース電極として使用するLDMOSFETにおいて、出力効率向上のため、基板抵抗を下げようとして高濃度ボロンドープ基板を用いると、ソースドレイン間のリーク不良が、多発することが、本願発明者等によって明らかにされた。更に、この不良解析の結果、ソース不純物ドープ領域からP型エピタキシ層を貫通してP型基板に至るP型ポリシリコンプラグに起因する不所望な応力が、このリーク不良の原因であることが明らかにされた。

【解決手段】本願発明は、LDMOSFETを含む半導体装置であって、LDMOSFETのソース不純物ドープ領域の近傍の上面から下方に向けてエピタキシ層内をシリコン基板の近傍まで延び、前記エピタキシ層内にその下端があるシリコンを主要な成分とする導電プラグを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】D−RAMのキャパシタを形成するシリンダのドライエッチ加工において、従来技術の製造方法ではアスペクト比が高いシリンダやコンタクトの形状がボーイング形状となり隣接するホール間ショートの問題やホール内に形成する電極成膜のカバレッジ異常などの問題が発生する。

【解決手段】本発明ではシリコン酸化膜4aにコンタクトホールを形成する際にボーイングが発生する部分にLow−k膜の炭化シリコン酸化膜5を挿入して積層構造とし、ドライエッチでシリコン酸化膜4aのエッチング速度に対し、炭化シリコン酸化膜5のエッチング速度が1/5〜1/10と遅い条件にすることでボーイング形状の抑制を可能にした。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明ではフォトリソグラフィー技術解像限界付近のパターン形成を安定して形成すると共に、コンタクトプラグなどの構造物における目合わせずれや接触面積の縮小による接触電気抵抗の増大や接続不良を解決する。

【解決手段】半導体基板上に形成された絶縁材料層100に、第1の方向に延在し、底部の幅W1より上部の幅W2が広い第1の溝101を形成する工程と、第1の溝101内に、溝の上端より低い位置まで埋め込み層102を形成する工程と、埋め込み層102上に露出している第1の溝101の側壁を覆うサイドウォール103を形成する工程と、サイドウォール103をマスクとして埋め込み層102をエッチングして第1の方向に分離する工程と、

を含むことを特徴とする。

(もっと読む)

洗浄組成物、半導体装置の製造方法及び洗浄方法

【課題】半導体基板のタングステンの腐食を抑制でき、かつ、半導体基板上のプラズマエッチング残渣及び/又はアッシング残渣の除去性に優れた洗浄組成物、並びに、前記洗浄組成物を用いた半導体装置の製造方法及び洗浄方法を提供すること。

【解決手段】(成分a)水、(成分b)アミン化合物、(成分c)ヒドロキシルアミン及び/又はその塩、(成分d)第4級アンモニウム化合物、(成分e)有機酸、並びに、(成分f)水溶性有機溶剤、を含み、pHが6〜9であることを特徴とする、半導体基板上に形成されたプラズマエッチング残渣及び/又はアッシング残渣除去用の洗浄組成物、並びに、前記洗浄組成物を用いた半導体装置の製造方法及び洗浄方法。

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

基板洗浄方法及び基板洗浄装置

【課題】異種金属が露出した基板表面の洗浄において卑金属の溶解を防止する。。

【解決手段】基板保持台26に保持された基板24表面の周縁部の上方にノズル21を配置し、カーボン電極23Aを通じて電圧発生装置29により電圧を印加された薬液213をノズル21から基板24表面の周縁部に供給する。次に、薬液213をノズル21から供給しながら、基板24表面の中央部の上方にノズル21を移動させた後、薬液213をノズル21から基板24表面の中央部に供給する。

(もっと読む)

薄膜のパターニング方法及び表示パネルの製造方法

【課題】コンタクトホールをより微細に形成することができる薄膜のパターニング方法及び表示パネルの製造方法を提供する。

【解決手段】所定の段差部を有した絶縁層25を形成する工程と、スパッタ法により前記段差部を覆うようにして前記絶縁層25上に犠牲層28を成膜する工程と、前記段差部に対応する領域における前記犠牲層28のうちの少なくとも一部の除去と、前記除去により前記犠牲層28から露出された領域における前記絶縁層25の除去とを、ドライエッチングにより連続して行う工程と、前記ドライエッチングで残存した前記犠牲層28の少なくとも一部をウェットエッチングにより除去する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】配線溝パターンの深さを精密に制御でき、かつ当該配線溝パターンのダメージ形成を抑制できる半導体装置の製造方法を提供する。

【解決手段】拡散防止膜ADF上に、第2の低誘電率膜LOWK2c、第3の低誘電率膜LOWK3c、マスク層となるべき膜がこの順に積層される。マスク層となるべき膜をエッチングし、底面が第3の低誘電率膜LOWK3cの表面により構成される配線溝パターンを形成することにより、マスク層SIO2dが形成される。アッシング処理により第1のレジストマスクが除去される。マスク層の配線溝パターンを用いて、底面が第2の低誘電率膜LOWK2cとなるように、配線溝TRCHが形成される。充填される銅金属CUaの頂面から第3の低誘電率膜LOWK3cまでの層がCMP法により除去される。上記各低誘電率膜はFSGよりも誘電率が低く、第2の低誘電率膜LOWK2cは第3の低誘電率膜LOWK3cよりも誘電率が低い。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】イオンエネルギー分布の制御に加えて正イオンによるチャージアップの緩和を行うことで、加工形状の制御をさらに高精度に行うことができる半導体装置の製造方法及び半導体製造装置を提供する。

【解決手段】半導体製造装置としてのプラズマ処理装置10は、チャンバー11と、チャンバー11に設けられ、半導体ウエハWが配置されるウエハ設置電極12と、ウエハ設置電極12に対向するようにチャンバー11内に設けられた対向電極13と、ウエハ設置電極12に高周波電圧を印加する高周波電源14と、ウエハ設置電極12に高周波電圧と重畳するように負の第1のDCパルス電圧V1を印加する第1のDCパルス電源17Aと、第1のDCパルス電圧V1のオフ期間に、対向電極13に負の第2のDCパルス電圧V2を印加する第2のDCパルス電源17Bとを備える。

(もっと読む)

エッチング処理方法

【課題】形成されるパターンのアスペクト比が高くてもパターンが歪むのを防止することができるエッチング処理方法を提供する。

【解決手段】処理室15内部にプラズマ生成用の高周波電力55が印加され、サセプタ12にイオン引き込み用の高周波電力56が印加され、上部電極板27に負の電位の直流電力が印加される基板処理装置10において、ウエハW上のフォトレジスト膜45において形成されたパターン44の形状を改良する際、フォトレジスト膜45をプラズマでエッチングし、該フォトレジスト膜45を用いてSiO2膜40をプラズマでエッチングする際、負の電位の直流電力を上部電極板27に印加するとともに、プラズマ生成用の高周波電力55及びイオン引き込み用の高周波電力56をパルス波状に印加してプラズマ生成用の高周波電力55及びイオン引き込み用の高周波電力56が印加されない状態を作り出す。

(もっと読む)

プラズマエッチング方法、プラズマエッチング装置及びコンピュータ記憶媒体

【課題】深さが深いホールであっても、良好な形状にエッチングすることのできるプラズマエッチング方法、プラズマエッチング装置及びコンピュータ記憶媒体を提供する。

【解決手段】所定のパターンが形成されたフォトレジスト層と、フォトレジスト層の下層に位置する有機系の反射防止膜と、反射防止膜の下層に位置するSiON膜と、SiON膜の下層に位置するアモルファスカーボン層と、により多層マスクを構成し、アモルファスカーボン層の下層に位置するシリコン酸化膜又はシリコン窒化膜を最終的なマスクとなるアモルファスカーボン層のパターンによりプラズマエッチングするプラズマエッチング方法であって、シリコン酸化膜又はシリコン窒化膜のプラズマエッチングを開始する際の初期マスクが、アモルファスカーボン層の上にSiON膜が残った状態であり、かつ、アモルファスカーボン層の膜厚/残ったSiON膜の膜厚≦14である。

(もっと読む)

基板の配線方法及び半導体製造装置

【課題】基板上に形成された配線用パターンの底部までCu埋め込みが可能な基板の配線方法を提供する。

【解決手段】真空状態に保持された処理容器100内にて配線用パターンが形成された基板を配線する方法であって、ウエハ上の配線用パターンを所望のクリーニングガスにより洗浄する前工程と、前工程後、クラスタ化された金属ガス(金属ガスクラスタCg)を用いて配線用パターン内に金属ナノ粒子を埋め込む埋め込み工程と、を含むことを特徴とする基板の配線方法が提供される。

(もっと読む)

プラズマエッチング方法

【課題】従来技術ではデュアルダマシン構造Via工程のLow−K膜エッチング後の孔底部のエッチングにおいて、ストッパ膜のエッチングが進行しない課題があった。

【解決手段】本発明はプラズマエッチングするデュアルダマシンプロセスにおいて、デュアルダマシンプロセスのVia加工方法は、Viaパターニングされた上層レジスト膜をマスクとして反射防止膜をエッチングする第1ステップと、上層レジスト膜及び反射防止膜をマスクとして下層レジスト膜をエッチングする第2ステップと、下層レジスト膜をマスクとして前記Low−K膜をエッチングする第3ステップと、ストッパ膜のエッチング前にプラズマ処理を行う第4ステップと、ストッパ膜をエッチングする第5ステップとを有することである。

(もっと読む)

半導体装置の製造方法

【課題】ホール形状を垂直として微細化を図ることができるとともに、従来に比べて工程数を削減することができ、生産性の向上を図ることのできる半導体装置の製造方法を提供する。

【解決手段】基板にホールを形成するホール形成工程と、前記ホール内にポリイミド膜を形成するポリイミド膜形成工程と、前記基板を、前記ホール内の側壁部の前記ポリイミド膜を覆うマスクを使用せずに異方性エッチングして、前記ホール内の側壁部の前記ポリイミド膜を残したまま、前記ホール内の底部の前記ポリイミド膜の少なくとも一部を除去して貫通させるプラズマエッチング工程と、前記ホール内に導体金属を充填する導体金属充填工程とを具備した半導体装置の製造方法。

(もっと読む)

ドライエッチング剤

【課題】経済性を備え、地球環境に対する影響が小さく、かつ必要とされる性能を有するドライエッチング剤を提供する。

【解決手段】(A)3,3,3−トリフルオロプロピンと、(B)O2、O3、CO、CO2、COCl2、及びCOF2からなる群より選ばれる少なくとも1種のガスを含むドライエッチング剤を用いることにより、酸化物、窒化物、炭化物、フッ化物、オキシフッ化物、シリサイド及びこれらの合金等を好適にエッチングできる。ドライエッチング剤は、大気中での分解性があり、地球温暖化への寄与もCF4やCF3H等のPFC類やHFC類より格段に低く、環境への負荷が低い。さらに、第二のガスとして、含酸素ガス、含ハロゲンガス、あるいは第三のガスとして不活性ガスと混合することで、飛躍的にプロセスウインドウを広げることができ、特殊な基板の励起操作等なしに高アスペクト比が要求される加工にも対応できる。

(もっと読む)

ドライエッチング剤

【課題】経済性を備え、地球環境に対する影響が小さく、かつ必要とされる性能を有するドライエッチング剤を提供する。

【解決手段】化学式CF3C≡CX(但し、XはF、Cl、Br、I、CH3、CFH2、又はCF2Hを表す。)で表される化合物を含むドライエッチング剤を用いることにより、酸化物、窒化物、炭化物、フッ化物、オキシフッ化物、シリサイド及びこれらの合金等を好適にエッチングできる。ドライエッチング剤は、大気中での分解性があり、地球温暖化への寄与もCF4やCF3H等のPFC類やHFC類より格段に低く、環境への負荷が低い。さらに、第二のガスとして、含酸素ガス、含ハロゲンガス、あるいは第三のガスとして不活性ガスと混合することで、飛躍的にプロセスウインドウを広げることができ、特殊な基板の励起操作等なしに高アスペクト比が要求される加工にも対応できる。

(もっと読む)

半導体装置の製造方法

【課題】DRAM素子のような半導体装置において、半導体基板の溝部におけるゲート電極の埋設状態が良好となり、配線抵抗が低減され、素子特性に優れた半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の表面にゲート電極溝13を形成する工程と、ゲート電極溝13の内面に第1のバリア膜16aを形成する工程と、第1のバリア膜16aをエッチバックして、ゲート電極溝13の底面に第1のバリア膜16aの一部を残存させながら除去する工程と、ゲート電極溝13の内面と残存した第1のバリア膜16aの表面に第2のバリア膜16bを形成する工程と、第2のバリア膜16aの表面にタングステン膜を形成する工程と、このタングステン膜及び第2のバリア膜16bをエッチバックしてゲート電極溝13内にそれぞれ一部を残存させながら各膜を一括除去する工程と、を具備する。

(もっと読む)

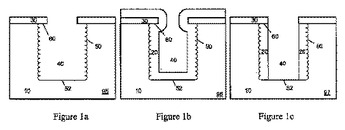

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

61 - 80 / 584

[ Back to top ]