Fターム[5F004EB01]の内容

半導体のドライエッチング (64,834) | エッチング対象部の機能 (2,366) | コンタクトホール (584)

Fターム[5F004EB01]に分類される特許

161 - 180 / 584

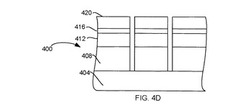

二重層マスク、三重層マスクのCD制御

【課題】パターンつきフォトレジストマスクと、その下に配された中間マスク層と、その下に配された機能性有機質マスク層と、その下に配されたエッチング層とによって形成されるスタックにおいてエッチング層内のエッチング構成の限界寸法を制御するための方法を提供する。

【解決手段】中間マスク層416は、パターンつきフォトレジストマスク420に対して選択的にエッチングすることによって開口される。機能性有機質マスク層412の開口は、COSを含む開口ガスを流すこと、プラズマを発生させること、および開口ガスを流すことを停止する工程とを含んでいる。その後エッチング層408は、所望の寸法にエッチングされる。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】CO2プラズマに晒された低誘電率絶縁膜のダメージを回復させて、低誘電率絶縁膜を良好な状態にすることができ、半導体装置における性能の向上と信頼性の向上を図ることのできる半導体装置の製造方法及び半導体装置の製造装置を提供する。

【解決手段】基板に形成された低誘電率絶縁膜をエッチングするエッチング処理工程と、当該エッチング処理工程の後に基板をCO2プラズマに晒すCO2プラズマ処理工程と、CO2プラズマ処理工程の後に、低誘電率絶縁膜に紫外線を照射する紫外線処理工程とを有する半導体装置の製造方法。

(もっと読む)

高度な微小寸法コンタクトのための自己整合多重パターン形成

【課題】 基板上の特徴部の密度を増大させる処理シーケンスを提供すること。

【解決手段】 本発明の実施形態は、単一の高解像度フォトマスクを使用する標準のフォトリソグラフィ処理技法を使用して可能なものに比較して、2次元において減少ピッチを有するパターン形成特徴部を基板上に形成する方法に関する。方形の角部の4つのコアの中心にディンプルを残すように選択された厚さを有するスペーサ層が、コアの2次元方形格子上に形成される。上記スペーサ層は、上記方形の中心において上記基板をさらすように、エッチングバックされる。上記コア材料を除去することにより、コアのフォトリソグラフィ画成格子のパターン密度が2倍とされる。露出された基板の領域には、再びコア材料を充填することができ、上記処理は、上記パターン密度が4倍となるように繰り返される。

(もっと読む)

半導体装置の製造方法

【課題】シリコン酸化膜に対して、高選択比にシリコン窒化膜をエッチングすることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、フルオロカーボンガスを含むエッチングガスを用いて、シリコン窒化膜5の上に設けられた層間絶縁膜6をドライエッチングする第一の工程と、第一の工程に引き続き、酸化性ガスを供給してプラズマを発生させて、サイドウォール4の上に設けられたシリコン窒化膜5をドライエッチングする第二の工程と、を含み、第二の工程は、フルオロカーボンガスを供給しないことを特徴とする。

(もっと読む)

プラズマエッチング方法及びプラズマエッチング装置

【課題】アスペクト比エッチングを行う際に,エッチングレートとレジスト選択比の両方を従来以上に向上させることができるプラズマエッチング方法を提供する。

【解決手段】堆積性を有するエッチングガス(例えばフルオロカーボン系ガス)を含む処理ガスにSF6ガスを添加ガスとして加えて処理室102内に導入してプラズマを形成し,その際に添加ガスの流量を調整することによって,ウエハW上に堆積する堆積物の膜厚を制御するとともに,堆積物の硬さを制御しながら,被エッチング膜のエッチングを進行させる。

(もっと読む)

半導体装置の製造方法

【課題】生産性を極端に落とすことなく、開口の形状悪化を抑止するエッチング方法を提供する。

【解決手段】半導体基板1上に絶縁層2を介して形成されたパッド電極3を被覆するように前記半導体基板1の表面に支持体5を接着する工程と、前記半導体基板1の裏面から前記パッド電極3の表面に到達するようにビアホールを形成する工程とを有するものにおいて、前記半導体基板1に対して前記絶縁層2が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板1に対して前記絶縁層2が露出する位置まで第2の開口8を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第2のエッチング工程は前記第1のエッチング工程よりも前記半導体基板に印加される交流電圧の周波数を低くする。

(もっと読む)

ドライエッチング方法及びドライエッチング装置

【課題】Si層と下地層としてのSiO2層を有する基板に貫通ビアを形成するドライエッチングにおいて、貫通ビアの開口部付近の側壁の角部ないし肩部を確実なくす。

【解決手段】基板7はSi層21、SiO2層22、フォトレジストマスク24を少なくとも備える。少なくともSF6とO2を含む混合ガスを使用したドライエッチングによりSi層21を貫通する貫通ビア31を形成する。次に、アッシングによりフォトレジストマスク24を除去する。さらに、高C/F比のフルオロカーボン系ガスを含むガスを使用したドライエッチングによりSiO2層22をエッチングし、それによって貫通ビア31がSiO2層22を貫通する。

(もっと読む)

半導体装置の製造方法

【課題】Alを含む金属配線の形成において、サイドエッチ量を低減した微細な金属配線を形成でき、金属配線上に形成するビアホールが金属膜を突き抜けるのを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板上に第一TiN膜3、Alを含む金属膜4、第二TiN膜5を順次積層した金属配線層6を形成する工程と、前記金属配線層6の上にストッパー膜7、シリコン酸化膜8を順次積層したハードマスク層12を形成する工程と、前記ハードマスク層12を選択的にエッチングして前記金属配線層6の上にハードマスク12aを形成する工程と、前記ハードマスク12aをマスクとしてエッチングし金属配線6aを形成する工程と、前記ハードマスク12aおよび前記金属配線6aの上に層間絶縁膜14を形成する工程と、前記ストッパー膜7をエッチングストッパとして前記層間絶縁膜14にビアホール17aを形成する工程とを含む。

(もっと読む)

電子基板、電子基板の製造方法、および表示装置

【課題】層間絶縁膜を介して配線された上下の導電パターンが、これらの導電パターン形成後に接続配線によって接続された構成において、接続抵抗の上昇を防止でき、さらにこの構成を製造する際のプロセスタクトタイムの削減が図られる電子基板を提供する。

【解決手段】基板1上に設けられた第1導電パターン3と、これを覆う状態で基板1上に設けられた層間絶縁膜5と、第1導電パターン3上に一部を重ねた状態で層間絶縁膜5上に設けられた第2導電パターン9とを備えている。第2導電パターン9と第1導電パターン3とが重なる位置には、第2導電パターン9および層間絶縁膜5に開口部31が設けられている。この開口部31は第1導電パターン3を底面としており、この開口部31の内壁を覆う接続配線33により、第2導電パターン9と第1導電パターン3とが結線されている。

(もっと読む)

コンタクトホール側壁の抵抗値測定方法

【課題】コンタクトホール側壁に付着した有機膜の抵抗値を簡単且つ的確に測定する。

【解決手段】基板20上に形成された下部電極であるポリSi膜22aと、このポリSi膜22a上にBPSG膜23を介して形成された中間電極であるポリSi膜24aと、このポリSi膜24a上にBPSG膜25を介して選択的に形成されたホトレジスト膜からなるホールパターン26aと、このホールパターン26aをマスクにしてプラズマエッチングにより形成され、ポリSi膜24a,22aを貫通するコンタクトホール27と、このコンタクトホール27の形成時に、コンタクトホール側壁に付着する有機膜28と、を有する半導体装置を用意する。そして、ポリSi膜22a,24a上に有機膜・レジスト膜26bが被着された状態で、ポリSi膜22a,24a上から、プローブ針31により複数回コンタクトを実施し、有機膜28の抵抗値を測定する。

(もっと読む)

半導体装置の製造方法

【課題】使用に伴う製造装置の性能劣化を抑えつつ、高品質の半導体装置を安定して製造する。

【解決手段】チャンバ内を水素を含むプラズマを用いて処理することによってクリーニングし(ステップS1)、クリーニングされたチャンバを用い、ウェーハにエッチングによりトレンチやビアホールを形成する等の加工を行う(ステップS2,S3)。チャンバ内のクリーニングに水素を含むプラズマを用いることにより、チャンバ内にCu等の金属が含まれたポリマが付着していた場合でも、そのような付着物が効果的に除去されるようになる。それにより、付着物に起因した製造装置の性能劣化を抑えることが可能になり、高品質の半導体装置を安定して製造することが可能になる。

(もっと読む)

有機化合物含有絶縁層の異方性エッチング

【課題】半導体加工において有機化合物含有絶縁層に小さな穴を形成する方法を提供する。

【解決手段】有機化合物含有絶縁層12を、この有機化合物含有絶縁層12上に形成されたレジストハードマスク層13とこのレジストハードマスク層13上に形成されたレジスト層14からなる2重層で覆い、次に、この2重層をパターニングする。そして、反応チャンバー内に、自然エッチングが実質的に避けられるように選ばれる、あらかじめ決められた割合で存在する酸素ガスと窒素ガスとからなる混合気体を流入し、有機化合物含有絶縁層12をプラズマエッチングする。これにより、レジスト層14を部分的に除去しつつ少なくとも一つの穴を形成する。

(もっと読む)

基板処理方法

【課題】処理対象の基板に対し、半導体デバイスの小型化要求を満たす寸法の開口部であって、エッチング対象膜に転写するための開口部をマスク膜又は中間膜に形成する基板処理方法を提供する。

【解決手段】SiN膜51、反射防止膜52及びフォトレジスト膜53が順に積層され、フォトレジスト層53は反射防止膜52の一部を露出させる開口部54を有する基板Wを処理する基板処理方法であって、一般式CxHyFz(x、y、zは、正の整数)で表わされるデポ性ガス、例えばCH3Fガス及びSF6ガスの混合ガスから生成されたプラズマによってフォトレジスト膜53の開口部54の側壁面にデポを堆積させて縮小させると共に、反射防止膜52をエッチングして縮小した開口部54に対応する開口部を反射防止膜52に形成するシュリンクエッチングステップを有する。

(もっと読む)

基板処理方法

【課題】処理対象の基板に対し、半導体デバイスの小型化要求を満たす寸法の開口部であって、エッチング対象膜に転写するための開口部をマスク膜又は中間膜に形成する基板処理方法を提供する。

【解決手段】シリコン基材50上にアモルファスカーボン膜51、SiON膜52、反射防止膜53及びフォトレジスト層54が順に積層され、フォトレジスト層54は、反射防止膜53の一部を露出させる開口部55を有するウエハQにおいて、ガス付着係数S

が、S=0.1乃至1.0のデポ性ガスであるCHF3から生成されたプラズマによってフォトレジスト膜54の開口部55の側壁面にデポ66を堆積させて開口部55の開口幅を所定幅に縮小させる開口幅縮小ステップを有する。

(もっと読む)

電極形成方法および半導体素子

【課題】電極パタンを精度よく形成する。

【解決手段】半導体基板の一方面(コンタクト層10)上に、SiO2膜12−1、SiN膜14−1、SiO2膜12−2、およびSiN膜14−2を順に積層した4層の絶縁膜を形成する工程と、それら4層の絶縁膜にコンタクト層10の表面まで貫通するコンタクトホールを形成する工程と、SiO2膜12に対するエッチングレートがSiN膜14に対するエッチングレートより高い薬液(たとえばフッ酸)を用いて、コンタクトホールに露出したSiO2膜12−2の側面をコンタクトホールに露出したSiN膜14−2の側面より所定長だけ後退させる工程と、コンタクトホールに露出したコンタクト層10上に、SiN膜14−2に当接しない厚さを有する電極層20−1を蒸着により形成する工程と、上記薬液を用いて、SiN膜14−2をSiO2膜12−2とともに除去する工程と、を含む。

(もっと読む)

プラズマ処理装置およびプラズマ処理方法

【課題】ウエハ処理に従い消耗するフォーカスリング厚さを監視する。

【解決手段】真空容器1と、被加工試料設置手段5と高周波電力導入手段4と高周波バイアス電力導入手段7を有し、真空容器1内に導入されたガスを高周波電力導入手段4から導入された高周波電力でプラズマ化したプラズマにより被加工試料6の表面処理を行うプラズマ処理装置であって、被加工試料設置手段5上に載置された被加工試料6の周囲に円環状部材11を備え、真空容器1側壁に対向してアスペクト比が3以上の一対の筒を設け、それぞれの筒はその先端をガラス材により真空に封じられ、それぞれの筒はガラス材の大気側に真空容器内に向けて配置された光源15または真空容器内に向けて配置された受光手段16を有しており、円環状部材11表面を通過してきた光を受光手段16にて受光する。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホールを形成する時に、コンタクトホールに加工不具合を生じさせることなく、ホール底の下地基板が削れることを抑制することを目的とする。

【解決手段】コンタクトホール11形成後、コンタクトホール11底面に露出したSiOC膜7を変質層12に変化させることにより、変質層12と半導体基板1の選択比大きくすることができ、選択的に変質層12をエッチング除去できるため、下地基板掘れ量を抑制し、重ね合わせずれなどが発生したときにも、基板リークの発生を抑制したコンタクトを形成することができる。

(もっと読む)

プラズマ処理方法及びプラズマ処理装置

【課題】成膜レートを安定に維持することができるプラズマ処理方法及びプラズマ処理装置を提供する。

【解決手段】本発明の一形態に係るプラズマ処理方法は、エッチング工程と保護膜形成工程とを交互に繰り返し実施することでシリコン基板に高アスペクト比のビアを形成する。そして、保護膜の形成工程にはスパッタ法が適用される。スパッタ工程では、アンテナコイル23に高周波電力(RF1)を供給して、真空槽21内にスパッタ用ガスのプラズマを形成する。このとき、アンテナコイル23に供給する高周波電力を2kW以上とする。アンテナコイル23に供給する高周波電力が2kW以上の場合、当該高周波電力が2kW未満である場合と比較して、ターゲット30の使用時間に依存しない安定した成膜レートを得ることが可能となる。

(もっと読む)

腐刻方法、清掃処理方法

【課題】微細化を可能にすると共に、安定して良好な腐刻を行うことを可能にする腐刻方法を提供する。

【解決手段】Si,Snのうち1種類以上の原子で構成された物質を腐刻対象物として、腐刻用ガスの放電により腐刻を行う際に、腐刻用ガスとして炭素原子を含まないハロゲン間化合物ガスを使用する。さらに、この腐刻用ガスに、腐刻側壁を表面酸化することにより異方性腐刻の水平方向の腐刻速度を低下させて異方性を強調するために、酸素原子を含む酸化性ガスを添加して、腐刻対象物に対して腐刻を行う。

(もっと読む)

半導体装置の製造方法

【課題】パッド領域上での堆積物の生成を抑制することのできる、半導体装置の製造方法を提供する。

【解決手段】パッド領域を有する配線層群を形成するステップと、前記配線層群が被覆されるように、絶縁性のカバー層を形成するステップと、前記パッド領域が露出するように、前記カバー層をプラズマエッチングにより除去するステップとを具備し、前記パッド領域は、アルミニウムにより形成され、前記プラズマエッチングにより除去するステップは、炭素ラジカル及びフッ素ラジカルを発生させるCF系ガスを用いて、前記パッド領域を露出させるステップと、前記露出させるステップの後に、塩素ラジカル又は塩素イオンを発生させるCl2系ガスを用いて、前記パッド領域の表面に生成した堆積物を除去するステップとを備える。

(もっと読む)

161 - 180 / 584

[ Back to top ]