Fターム[5F004EB01]の内容

半導体のドライエッチング (64,834) | エッチング対象部の機能 (2,366) | コンタクトホール (584)

Fターム[5F004EB01]に分類される特許

141 - 160 / 584

半導体装置の製造方法

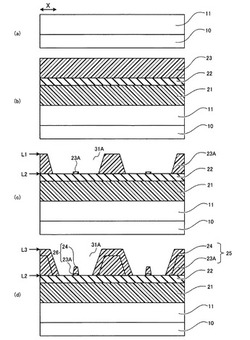

【課題】露光可能限界寸法よりも小さい間隔のパターンを形成することができる半導体装置の製造方法を提供する。

【解決手段】基板10上に形成された被加工膜11上にレジスト膜23を形成する工程と、前記レジスト膜を露光、現像し、第1の方向に伸長し、前記第1の方向に垂直な第2の方向にくびれ部を有する開口パターン31Aを形成する工程と、ガス存在雰囲気下で前記レジスト膜上に前記ガスを構成する元素を含む堆積物24を堆積し、前記くびれ部における前記開口パターンの底部を前記第2の方向に前記堆積物で接続した膜パターン25を形成する工程と、前記膜パターンが転写されるように、ドライエッチング法によって前記被加工膜をエッチングする工程と、を含む。

(もっと読む)

基板処理装置及び基板処理方法

【課題】基板に所望のプラズマ処理を適切に施すことができる基板処理装置を提供する。

【解決手段】基板処理装置10は、ウエハWを収容するチャンバ11内部をプラズマ生成室12及びウエハ処理室13に仕切るイオントラップ14と、プラズマ生成室12内に配置される高周波アンテナ15と、プラズマ生成室12内に処理ガスを導入する処理ガス導入部16と、ウエハ処理室13内に配置されてウエハWを載置し且つバイアス電圧が印加される載置台17とを備え、イオントラップ14は、プラズマ生成室12からウエハ処理室13へ向けて二重に配置された板状の上側イオントラップ板20及び下側イオントラップ板21を有し、上側イオントラップ板20及び下側イオントラップ板21のそれぞれは設置された導電体20a,21aと該導電体20a,21aの表面を覆う絶縁体からなる絶縁膜20b,21bとを有する。

(もっと読む)

プラズマ処理方法

【課題】ウエハに印加されるバイアス電力の一部を分割してフォーカスリングに印加しても、ウエハに印加するバイアス電力に影響を与えず一定となるように制御し、被処理基板全体のエッチング特性に変化を与えないプラズマ処理方法を提供する。

【解決手段】プラズマ処理により消耗するフォーカスリングの消耗量に応じて、前記フォーカスリングに印加する高周波バイアス電力を前記インピーダンス調整回路を制御することで変化させる一方、前記試料台に印加する前記高周波バイアス電力を、前記高周波バイアス電源の出力を制御することで、前記所定の高周波バイアス電力に制御する。

(もっと読む)

半導体装置の製造方法

【課題】配線抵抗値の異常やショートの抑制。

【解決手段】層間絶縁膜18にレジストパターン19を設けたうえで層間絶縁膜18をドライエッチングする工程の後と、レジストパターン19を除去した状態のストレッサーSiN膜17をさらにドライエッチングする工程の後とのうちのいずれかの時点で、半導体ウェーハ102を窒素プラズマ処理する。

(もっと読む)

プラズマエッチング方法、プラズマエッチング装置および記憶媒体

【課題】形状性良くかつ高いエッチングレートで被エッチング膜をエッチングして高アスペクト比のホールを形成することができるプラズマエッチング方法を提供すること。

【解決手段】プラズマエッチングによりエッチング対象膜にホールを形成するにあたり、プラズマ生成用高周波電力印加ユニットをオンにして処理容器内にプラズマを生成し、かつ直流電源から負の直流電圧を上部電極に印加する第1条件と、プラズマ生成用高周波電力印加ユニットをオフにして処理容器内のプラズマを消滅させ、かつ直流電源から負の直流電圧を上部電極に印加する第2条件とを交互に繰り返し、第1条件によりプラズマ中の正イオンによりエッチングを進行させ、第2条件により負イオンを生成し、直流電圧により負イオンを前記ホール内に供給することによりホール内の正電荷を中和する。

(もっと読む)

MEMSによるスプレイ装置用ノズル集積膜の製造方法、及び該ノズル集積膜を含むスプレイ装置

【課題】 MEMSテクノロジーで得られるスプレイ装置用ノズル集積膜を製造する方法、及び既知の技術が持つ欠点を有することのない上記膜を含むスプレイ装置を提案する。

【解決手段】 スプレイ装置のノズル膜を製造する方法は、基板(11)を設けるステップと、前記基板(11)上に膜層(13)を形成するステップと、前記膜層(13)内に複数のノズル(14)を形成するステップと、基板(10)内に複数の供給通路(15)を形成するステップとを含む。各供給通路(15)は、前記複数のノズルに含まれる個々のノズル(14)にほぼ直交して配置し、個々のノズル(14)と直接接触させる。

(もっと読む)

基板処理方法及び記憶媒体

【課題】ホールの上面形状を整えて線条痕をなくすと共に、ボトム形状に歪みがなく、しかもボーイング形状の発生を防止して良好な垂直加工形状のホールを処理対象層に形成することができる基板処理方法を提供する。

【解決手段】処理ガスとしてCF4ガス、CHF3ガス及びC4F8ガスを含有する混合ガスを用い、処理圧力100mTorr(1.33×10Pa)〜150mTorr(2.0×10Pa)で中間層としてのBARC膜53をエッチングし、次いで、処理ガスとしてCOSガス含有ガスを用いて下層レジスト層としてのACL52をエッチングし、その後、処理ガスとしてC6F6ガス含有ガスを用いて処理対象層としての酸化膜51をエッチングする。

(もっと読む)

半導体装置の製造方法及び設計支援装置

【課題】コンタクト領域の欠損を抑制する技術を提供する。

【解決手段】半導体装置の製造方法は、基板上方に導電膜を形成し、導電膜上に補助パターンを形成し、導電膜及び補助パターンを覆うように金属膜を形成し、金属膜をエッチバックし、補助パターンの側面にサイドウォール膜を形成し、補助パターンを除去し、導電膜及びサイドウォール膜の一部を覆い、一部を露出させるレジストパターンを形成し、レジストパターンをマスクとしてエッチングによりサイドウォール膜の露出している部分を除去し、サイドウォール膜をマスクとして導電膜をエッチングして、ゲート電極及びゲート電極と導通するコンタクト領域を形成し、露出している部分が除去されることにより導電膜上に残存するサイドウォール膜の形状は、ゲート電極及びコンタクト領域の形状に対応し、補助パターンの形状は、コンタクト領域の形状に対応するサイドウォール膜の少なくとも三辺と接する。

(もっと読む)

半導体装置の製造方法

【課題】工程数の増加を抑えながら、ビア間の耐圧の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】配線2上に低誘電率膜5及び6を形成した後、低誘電率膜5及び6上にハードマスク7、8及び9を形成する。ハードマスク7〜9上にレジストマスクを形成する。レジストマスクを用いて低誘電率膜5及び6にビアホール11を形成する。レジストマスクをアッシングする。このとき、レジストマスクから生じる飛散物をビアホール11の少なくとも側面に付着させて保護膜12を形成する。その後、ビアホール11を配線2まで到達させ、ビアホール11内に導電材を埋め込む。

(もっと読む)

半導体装置の製造方法およびウェハ処理システム

【課題】ドライエッチング加工を行ったウェハにおけるデガスの影響による異物の発生を低減する。

【解決手段】半導体装置の製造方法は、各ウェハ150を略水平にして複数のウェハ150を上下に並べて収容するとともに、側方に設けられたドア104を含む収納容器100に、ドライエッチング加工が行われた複数のウェハを順次収容する工程と、ドア104が開いた状態で、収納容器100に収容すべきすべてのウェハ150が当該収容容器に収容されてから30秒以上、収納容器100内のウェハ150に対して水平方向からパージガスを吹き付ける工程と、を含む。

(もっと読む)

真空処理装置及び真空処理方法

【課題】同一の処理室で、自然酸化膜が除去された後にシリコン基板の界面の酸素を確実に除去する。

【解決手段】NH3及びN2及びNF3を導入し、シリコン基板5の酸化表面にNHxFyを作用させることで(NH4)2SiF6を生成し、シリコン基板5を所定温度に制御することにより(NH4)2SiF6を昇華させてシリコン基板5の表面の酸化膜を除去し、続けてNH3及びN2及びNF3を導入し、温度が維持された状態でシリコン基板の表面にFラジカルを作用させてシリコン層をエッチングする。

(もっと読む)

プラズマエッチング方法

【課題】開口面積の広いガードリング(GR)や開口面積の小さいビアホール(Via)を同時に且つ均等深さにエッチングすることができるプラズマエッチング方法を提供する。

【解決手段】プラズマエッチング装置のサセプタ16に印加される第2の高周波電力を、ウエハWのLow−k膜又はフォトレジスト膜にデポが堆積する第1のパワーと、ウエハWのLow−k膜をエッチングする第2のパワーとの間でパワー変調させると共に、第2の高周波電力を変調する際のデューティー比(第2のパワー時間/1周期全体の時間)を25〜80%、好ましくは25〜50%としてウエハWのLow−k膜をエッチングする。

(もっと読む)

コンタクトホール形成方法、電気光学装置用基板、電気光学装置及び電子機器

【課題】コンタクトホールの微細化を図りつつ、コンタクトホールを形成する際のエッチング処理に起因する不具合を抑制する。

【解決手段】コンタクトホール形成方法は、第1レジストパターンをマスクとして、第2材料を含んでなる第2層を、エッチング液を用いてパターニングして、第1材料を含んでなる第1層を部分的に露出させる第1開口部を形成する第1エッチング工程と、第2レジストパターンをマスクとして、第4材料を含んでなる第4層を、エッチングガスを用いてパターニングして、形成された第1開口部の少なくとも一部に対応すると共に、第3材料を含んでなる第3層を部分的に露出させる第2開口部を形成する第2エッチング工程とを備える。第1材料は、エッチング液によりエッチングされる度合いが第2材料に比べて小さい材料であり、第3材料は、エッチングガスによりエッチングされる度合いが第4材料に比べて小さい材料である。

(もっと読む)

空隙を充填するべく低抵抗率のタングステン膜を堆積させる方法

【課題】抵抗率が低く、表面粗度が低く反射率が高いタングステンを、CVD法により基板上の間隙または凹状特徴部分に充填する方法を提供する。

【解決手段】基板に設けられた凹状部分を部分的に充填するタングステンバルクを堆積した後で、堆積されたタングステンの上部分を除去する。上部分の除去は、活性化されたフッ素種に基板を暴露することによって行われる。堆積されたタングステン粒子のうち急峻で突出している突起の頂点を選択的に除去することによって、除去処理は、凹状部分の側壁に沿ってタングステンを研磨することになる。堆積−除去のサイクルを複数回実行して、凹状部分を埋める。このようにして凹状部分が充填されると、CMPにおいてコアリング(coring)が発生しにくくなる。

(もっと読む)

ウェハ処理装置

【課題】半導体ウェハ内に深さの異なる複数の種類のトレンチを同時に形成できるとともに、半導体ウェハの無駄となる領域を少なくすることでチップの取れ数を増やすことができるウェハ処理装置を提供する。

【解決手段】ウェハ処理装置100は、ステージ14の表面に載置した半導体ウェハに対してプラズマ処理によってドライエッチングを行うための装置である。ウェハ処理装置100では、ステージ14が、ステージ14の周方向に4つの区画A〜Dに分割されている。区画A〜Dの各々には、ステージ14から半導体ウェハに伝熱される熱量を独立して制御する温度制御手段が設けられている。ステージ14の表面に半導体ウェハを載置したときに、半導体ウェハの周方向に温度の異なる複数の領域が形成され、領域毎に異なるエッチングレートでトレンチが形成される。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン法による解像限界以下の溝(トレンチ)及び凹部(孔又はビア)のパターンをCD値を高精度に形成することができる半導体装置の製造方法を提供する。

【解決手段】被エッチング層上に、第1のハードマスク膜と、第2のハードマスク膜とを成膜する成膜工程S11と、第1のピッチを有し、第2のハードマスク膜よりなるパターンであって、溝のパターンを形成する際のエッチングマスクとなる溝形成用マスクパターンを形成するための第1の溝形成用マスクパターン形成工程S12〜S14と、第4のピッチで設けられた開口部を有する第2のレジスト膜と、第2のレジスト膜の開口部と連通し、第2のレジスト膜の開口部の寸法より小さい寸法の開口部を有する第1の有機膜とよりなる第2レジストパターンを用いて、第1のハードマスク膜をエッチングする第1の凹部形成用マスクパターン形成工程S15〜S18とを有することを特徴とする。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】半導体装置の材料コスト、製造コストを低減可能な半導体装置およびその製造方法を提供する。

【解決手段】本発明にかかる半導体装置の製造方法は、シリコンサーメット膜5を形成する工程と、シリコンサーメット膜5を保護する保護膜4を形成する工程と、保護膜4をプラズマエッチングすることでコンタクトホール6を形成する開口工程と、を備える。そして、開口工程におけるエッチングの終点を検出するためのエッチング検出層3が保護膜4と接するように形成されている。保護膜4とエッチング検出層3の少なくとも一方には、保護膜4に含まれる元素とエッチング検出層3に含まれる元素のうち両方に共通しない元素が含まれている。開口工程において、両方に共通しない元素のプラズマ発光に基づき保護膜4のエッチングの終点を検出する。

(もっと読む)

基板内への構造の導入方法

本発明は、マイクロ構造を有する基板を製造する方法、並びに当該方法の自然科学及び科学技術−具体的には半導体デバイス、マイクロ流体デバイス、及び解析デバイス−への応用に関する。本発明は、制御された放電によって、構造−たとえば穴、空孔、チャネル、若しくはウエル又は凹部−又は構造変化を導入する方法に関する。  (もっと読む)

(もっと読む)

プラズマ処理装置のクリーニング方法

【課題】

本発明は、プラズマ処理装置のクリーニング方法であり、プラズマ処理室表面を効率良く清浄化し、スループットを向上できるプラズマ処理装置のクリーニングの方法を提供する。また、クリーニング中にウエハを設置する電極表面がプラズマに曝されないので電極の劣化を防止することができる。更に、クリーニングと同時に被処理体である低誘電率膜(Low−k膜)上に形成されたレジストマスクを除去する方法を提供する。

【解決手段】

スループットを向上させる手法として、CxFx系ガスを用いてエッチングされた低誘電率膜(Low−k膜)を、そのまま下部電極に載置した状態でCO2ガスによりプラズマクリーニングを行い、プラズマ処理室表面に付着したデポ物を除去する。この時、同時にLow−k膜上にパターニングされたレジストマスクを除去できるため、処理時間の大幅な短縮化が可能となる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置に含まれる半導体基板と当該半導体基板に形成される貫通孔(TSV)を含む配線との間の絶縁性を良好に保つことができる半導体装置の製造方法を提供する。

【解決手段】

貫通孔の内壁に形成された絶縁膜の開口底部に対応する部分を除く部分をエッチングレジストで被膜し、当該エッチングレジストをマスクとしたエッチングにより当該絶縁膜を除去して電極パッドを露出させた後、導電層を形成して配線する。

(もっと読む)

141 - 160 / 584

[ Back to top ]