Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

2,461 - 2,480 / 2,592

半導体装置

【課題】ターゲット等、光学的に位置検出するための大きな面積のパターン領域での表面平坦性を向上する。

【解決手段】ウェハのスクライブ領域SRに形成されるターゲットT2領域の下層に大面積ダミーパターンDLを形成する。また、製品領域PRおよびスクライブ領域SRの素子として機能するパターン(活性領域L1,L2,L3、ゲート電極17等)のパターン間スペースが広い領域に下層の小面積ダミーパターンと上層の小面積ダミーパターンDs2を配置する。このとき、上層の小面積ダミーパターンDs2は、下層の小面積ダミーパターンに対してハーフピッチシフトさせて形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通孔内に密着性が良好な絶縁樹脂層が形成され、これを介してビア(スルーホール導通部)が形成された信頼性の高い半導体装置を提供する。

【解決手段】半導体装置は、表面に素子が集積・形成された半導体基板1と、この半導体基板を貫通する貫通孔2と、貫通孔の側壁面に形成された第1の絶縁樹脂層5と、半導体基板の表裏両面に形成された第2の絶縁樹脂層6と、貫通孔内で第1の絶縁樹脂層上に形成された第1の導体層と、第2の絶縁樹脂層上に形成され第1の導体層と導通された第2の導体層7を有する。半導体基板にレーザ照射して貫通孔を形成する工程と、貫通孔内に絶縁樹脂を充填する工程と、充填された絶縁樹脂に樹脂貫通孔を同心的に形成する工程と、樹脂貫通孔の側壁面に導体層を形成し、半導体基板の表面と裏面を導通させるビアを形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクトと該コンタクトの上側の配線とのショートマージンを稼いだ半導体装置を得ること。

【解決手段】半導体基板1上に形成される所定形状の第1層配線10を含む第1の配線層8と、該第1の配線層8上に形成される層間絶縁膜11と、該層間絶縁膜11上に形成され、所定形状の第2層配線15を含む第2の配線層13と、第1層配線10と第2層配線15とを電気的に接続するコンタクト12と、を備える半導体装置において、コンタクト12は、所定の深さから上方に行くにしたがって積層方向におけるその断面形状が小さくなるように形成される。

(もっと読む)

半導体素子及びそれを備えたワイヤボンディング・チップサイズ・パッケージ

【課題】 短絡等の不具合が生じる虞がなく、配線自由度を容易に増大させることができ、配線の変更を容易かつ短時間で行うことができる半導体素子及びそれを備えたワイヤボンディング・チップサイズ・パッケージ(WBCSP)を提供する。

【解決手段】 本発明のWBCSPは、パッド33上に再配線パターン47aが、絶縁層43上に再配線パターン47bがそれぞれ形成され、再配線パターン47a、47b上にバンプ電極36a、36bが形成され、再配線パターン47bとパッド32とはボンディングワイヤ38により接続され、再配線パターン47a、47b及びボンディングワイヤ38は絶縁層39により封止され、ボンディングワイヤ38の最上部は、再配線パターン47a、47bより上方かつバンプ電極36a、36bの下端部より下方に位置していることを特徴とする。

(もっと読む)

半導体素子及びその製造方法

【課題】メッキ配線形成後の熱処理工程におけるビアホール周辺での膜浮き、及び膜剥がれを抑制し、高歩留まりかつ高信頼性を有する半導体素子を提供する。

【解決手段】本発明の半導体素子は、半導体基板1上に、凸状の段差4が形成されており、段差4の上面から基板1裏面に達するビアホール2を有しており、ビアホール2内にはシード層5を下層に有する第1のメッキ配線6が形成され、ビアホール2近傍の基板1の表面は絶縁膜3で覆われている。さらに、第1のメッキ配線6は段差4を覆うように形成されている。半導体基板1の裏面には全面に電極8が設けられており、第1のメッキ配線6は基板1の裏面で電極8と接続されている。

(もっと読む)

電子部品およびその製造方法

【課題】 接触抵抗の小さい電子部品およびその製造方法を提供する。

【解決手段】 下層金属配線4と、下層金属配線4上に形成された層間絶縁膜6と、層間絶縁膜6上に形成され、かつ層間絶縁膜6に形成された貫通孔5を介して下層金属配線4と電気的に接続された上層金属配線7と、を備える電子部品であって、下層金属配線4が少なくとも第1の金属と第2の金属とが拡散されてなり、第1の金属は第2の金属より酸化物の標準生成自由エネルギーが大きく、第2の金属は前記第1の金属より波長350〜440nmの光線の少なくとも一点で反射率が高く、かつ、上層金属配線8と下層金属配線4との間に、第1の金属より酸化物の標準生成エネルギーが小さい金属で形成される密着層7を備える。

(もっと読む)

多層ゲートスタック

プラズマによりパターン形成された窒化層を形成するために窒化層をエッチングすることからなる半導体構造体を製造する方法。窒化層は半導体の基板上にあり、フォトレジスト層は窒化層上にあり、プラズマは、少なくとも圧力10ミリトルでCF4及びCHF3のガス混合物から形成される。 (もっと読む)

半導体装置

【課題】 はんだ接続用パッドを有する半導体装置において、製造工程中の熱負荷などによって発生する恐れのある、パッド部の膜剥がれを防止する。

【解決手段】 シリコン、シリコン酸化膜上に形成されるTi膜またはTi化合物膜と、はんだが接続されるNi膜(またはCu膜)との間に、両者との密着性が良好なCr膜を挿入したパッド構造とする。さらに、Ti膜またはTi化合物膜とシリコン酸化膜との界面に生じる剥離を防止するため、Cr膜がTi膜またはTi化合物膜よりも大きな面積で形成された構造とする。

(もっと読む)

ドライエッチング方法

【課題】ハードマスクの角部分を、ラウンド形状に加工するドライエッチング方法を提供する。

【解決手段】パターンニングされたホトレジスト13によりシリコン窒化膜12のマスクを形成した後、ホトレジスト13をドライエッチングにより縮小させ、露出したシリコン窒化膜マスク12の角部分をエッチングすることで、シリコン窒化膜マスク12の角部分にラウンド形状を有する溝加工処理が可能となる半導体装置の製造方法。

(もっと読む)

軟金属導体およびその形成方法

【課題】 化学的機械的研磨プロセスで研磨した後でほぼ擦り傷なしの表面が得られるような、その最上部表面の硬度が改善された軟金属導体を提供する。

【解決手段】 その後の化学的機械的研磨ステップで研磨後にほぼ擦り傷なしの表面が得られるように、十分大きい粒子サイズを有する粒子から構成される最上部層を有する、半導体素子に使用するための軟金属導体78である。導電性軟金属構造の最上部層に軟金属構造の厚さの約20%以上の粒子サイズを有する金属粒子を付着する。

(もっと読む)

回路基板、電気光学装置、及び電子機器

【課題】 トランジスタ等の能動素子が安定に動作し、大画面化と長期にわたって安定した表示動作とを可能にする。

【解決手段】 陰極(222)と陽極(23)とに狭持され、基板(2)の上方に配置された電気光学素子と、電気光学素子を駆動する能動素子(24)と、陰極(222)及び陽極(23)のうち少なくとも一方と基板(2)との間に配置された誘電率が所定の値以下の絶縁材料からなる絶縁膜(283、284)とから電気光学装置(1)を構成する。

(もっと読む)

FeRAM用途のためのイリジウムエッチング

【課題】 FeRAM用途において、ハードマスクと下層とに対して選択性が高いイリジウムエッチングプロセスを提供する。

【解決手段】

強誘電体デバイスにおける使用のためのイリジウム層をエッチングする方法(10)は、基板を用意すること(12)と、基板の上にバリア層を堆積すること(14)と、バリア層の上にイリジウム層を堆積すること(16)と、イリジウム層の上にハードマスク層を堆積すること(18)と、ハードマスク層の上にフォトレジスト層を堆積し、パターニングし、現像すること(20)と、ハードマスク層をエッチングすること(22)と、高密度プラズマ反応炉においてアルゴン、酸素、および塩素成分を用いてイリジウム層をエッチングすること(24)と、強誘電体デバイスを完成させること(26)とを包含する。

(もっと読む)

エッチング液およびエッチング方法

【課題】反射防止膜とレジストを同時に除去する。

【解決手段】少なくとも1種の有機酸を含む、レジストと有機系反射防止膜、および/または有機系埋め込み材を除去するためのエッチング液。

(もっと読む)

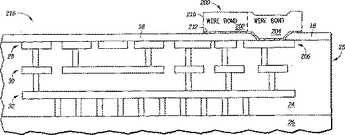

ボンディングパッドを有する半導体装置及びその形成方法

ボンディングパッド(200)は第1ワイヤボンディング領域(202)と、第2ワイヤボンディング領域(204)と、を含む。一実施形態では、第1ワイヤボンディング領域(202)がパッシベーション(18)を覆って延びる。別の実施形態では、ボンディングパッドはプローブ領域、第1ワイヤボンディング領域、及び第2ワイヤボンディング領域を有する。一実施形態では、プローブ領域及びワイヤボンディング領域がパッシベーション(18)を覆って延びる。ボンディングパッドはどのような数のワイヤボンディング領域及びプローブ領域も有することができ、かつこれらの領域をどのような構成として有することもできる。ボンディングパッドが複数のワイヤボンディング領域を含むことができるので、マルチチップパッケージにおける場合のように単一のボンディングパッドへの複数のワイヤ接続を行なうことができる。ボンディングパッドがパッシベーションを覆って延びる形でパッドを設けることができるので、集積回路チップ面積を小さくすることもできる。  (もっと読む)

(もっと読む)

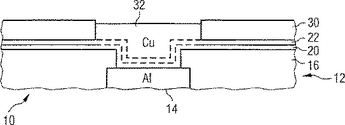

金属、特に銅を電着する方法、この方法の使用、および集積回路構造

とりわけ、絶縁層(16)内において相互接続(14)へのコンタクトホール(18)が生成される方法が示される。バリア層(20)が次いで提供される。その後、フォトレジスト層(30)が提供され、照射され、かつ、現像される。次いで、ガルバニック法を用いて、銅コンタクト(32)がコンタクトホール(18)において生成される。バリア層(20)またはさらなる境界電極層(22)のどちらか一方が、ガルバニック処理において境界電極としての役目をする。重大な金属汚染は、製造中、この方法によって抑制される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【目的】 点欠陥の集合によるボイドがCu配線内に形成しないようにすることを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S110)と、前記絶縁膜に開口部を形成する開口部形成工程(S112)と、前記絶縁膜表面と前記開口部とにシード膜を形成するシード膜形成工程(S116)と、前記シード膜を電極として第1の電流密度となる電流を流し、前記開口部に導電性材料をめっき法により堆積させる第1のめっき工程(S118)と、前記第1のめっき工程後、前記第1の電流密度より小さい第2の電流密度となる電流を流し、前記絶縁膜表面上に前記導電性材料をめっき法により堆積させる第2のめっき工程(S120)と、前記第2のめっき工程後、前記導電性材料が堆積した基体をアニール処理するアニール工程(S124)と、を備えたことを特徴とする。

(もっと読む)

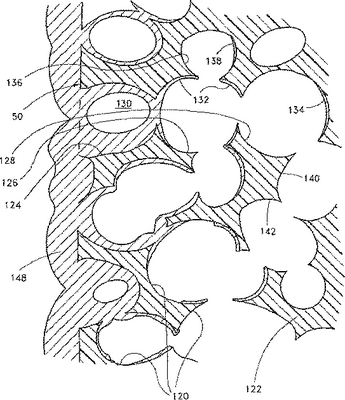

シーリング多孔質構造

集積回路中のデュアルダマシン(dual damascene)構造、特に多孔質材料中に形成された開口部のコンフォーマリティの裏張り(lining)のための方法及び構造が提供される。トレンチ(trench)及びコンタクトビア(contact via)が絶縁層中に形成される。これらのトレンチ及びビアの側壁上のポアがブロックされ、次いでこの構造は、所望のライニング材料の単層を形成するために交互に化学物質に曝される。例示的なプロセスフローにおいて、シーリング層の化学または物理気相成長法(chemical or physical vapor deposition)(CVDまたはPVD)により、不完全なコンフォーマリティに起因してポアをブロックする。交互のプロセスも、自己飽和(self−saturating)、自己制御(self−limiting)原子層堆積(atomic layer deposition)(ALD)プロセスと比較して減少されたコンフォーマリティを達成するようなパルス間隔及びパルス幅の選択によって構成され得る。なお別の構成において、異方性多孔質構造を有する層が、上部表面を選択的に溶融することによってシールされ得る。次いで、自己制御、自己飽和原子層堆積(ALD)反応により、有意にポアを充填することなくブロッキングが行われる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 容量値の均一性が高い容量素子を備える半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置1の容量素子形成領域20において、P型の半導体基板10の表層には、導電層としてN型ウエル22が形成されている。N型ウエル22が形成された半導体基板10の表面には、容量膜24が成膜されている。ここで、半導体基板10表面における容量膜24が成膜された部分は、実質的に平坦である。容量膜24上には、上部電極26が設けられている。上部電極26は、容量膜24を挟んで対向するN型ウエル22との間で容量素子(オンチップキャパシタ)を構成している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】 配線抵抗を低減させながら歩留まりを向上させたバリアメタル膜を形成することを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜に開口部を形成する開口部形成工程(S110)と、PVD法を用いて、前記絶縁膜上と開口部内とに第1のバリアメタル膜を形成する第1のバリアメタル膜形成工程(S116)と、その上に、CVD法を用いて第2のバリアメタル膜を形成する第2のバリアメタル膜形成工程(S118)と、その上に、PVD法を用いて第3のバリアメタル膜を形成する第3のバリアメタル膜形成工程S120)と、その上に、導電性材料を堆積させる堆積工程(S112,S124)と、を備え、前記絶縁膜上に形成された前記第1と第2と第3のバリアメタル膜の合計膜厚が、8nmより小さくなるように形成することを特徴とする。

(もっと読む)

アレイ基板の製造方法及びそれを用いた液晶表示装置の製造方法

【課題】本発明は、反射型や半透過型の液晶表示装置に用いられるアレイ基板の製造方法及びそれを用いた液晶表示装置の製造方法に関し、製造コストを削減しつつ良好な表示品質の得られるアレイ基板の製造方法及びそれを用いた液晶表示装置の製造方法を提供することを目的とする。

【解決手段】不規則な凹凸を表面に有する下地層を基板上に形成し、下地層表面に倣った凹凸を有する金属膜51を下地層上に形成し、金属膜51上に着色レジスト層を形成し、着色レジスト層をパターニングして規則的に配列する着色レジストパターン52を形成し、着色レジストパターン52の欠陥を光学的に検出するための光学検査を行い、光学検査により検出された着色レジストパターン52の欠陥を修復し、着色レジストパターン52をマスクとして金属膜51をエッチングする。

(もっと読む)

2,461 - 2,480 / 2,592

[ Back to top ]