Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

2,541 - 2,560 / 2,592

半導体装置

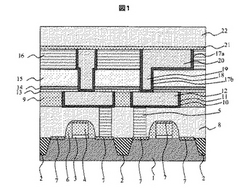

【課題】 銅を主構成材料とする配線構造において、ストレスマイグレーションによるボイドの発生を抑制し、信頼性の高い半導体装置を提供する

【解決手段】 半導体基板上の絶縁膜上に形成される多層配線構造において、主構成材料が銅からなる第1の配線の上面に接するように、下から順にバリア性が高く、かつ圧縮応力を有する第1の絶縁膜、引張応力を有する第2の絶縁膜、前記第1の絶縁膜と前記第2の絶縁膜よりも誘電率の低い第3の絶縁膜が少なくとも積層されており、前記第1の絶縁膜、前記第2の絶縁膜、および前記第3の絶縁膜を貫通し前記第1の配線に接するようにビアホールが設けられている配線構造とする。

(もっと読む)

半導体装置の製造方法

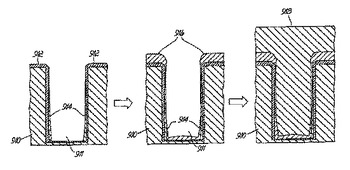

【課題】 アスペクト比の大きいコンタクトプラグにおいて、タングステン層等のプラグ用の下地導電層を形成した場合に、剥離による不良を低減することができる半導体装置の製造方法を提供する。

【解決手段】 導電層2の上に形成された層間絶縁層3を有するシリコン基板1において、層間絶縁層3の上にコンタクトホール5を形成するためのマスクを形成するマスク形成工程と、層間絶縁層3をドライエッチング法によりコンタクトホール5を形成するコンタクトホール形成工程と、コンタクトホール5内に導電層6aを形成する導電層形成工程と、前記コンタクトホール内に導電層6aよりも低応力の低応力導電層6bを形成する低応力導電層形成工程とを有する。

(もっと読む)

半導体パターン形成方法

【課題】 半導体パターン形成方法を提供する。

【解決手段】 この方法は無機ハードマスク膜、有機マスク膜、反射防止膜及びシリコン含有フォトレジスト膜が積層された多層のマスク層を形成し、O2プラズマで前記反射防止膜及び有機マスク膜を乾式エッチングしてパターンを形成することによって無機ハードマスク膜の損傷を防止することができる。

(もっと読む)

デュアル・ダマシン構造におけるMIMキャパシタの構造および製作方法

【課題】MIM(金属−絶縁体−金属)キャパシタ(242/252)構造およびそれを形成する方法を提供すること。

【解決手段】第1パターン(216)および第2パターン(218)を有するデュアル・ダマシン・パターンで、半導体デバイス(200)の誘電体層(214)をパターニングする。第2パターン(218)は、第1パターン(216)よりも深い。第1パターン中の誘電体層(214)の上に導電層(226)を形成し、第1パターン(216)中のこの導電層の上に導電層を形成する。第2パターン(218)の導電層(226)の上に、誘電体層(232)、導電層(234)、誘電体層(236)、および導電層(238)を配設する。導電層(234)、誘電体層(232)、および導電層(226)が、第1のMIMキャパシタ(252)を形成する。導電層(238)、誘電体層(236)、および導電層(234)が、第1のMIMキャパシタ(252)に並列な第2のMIMキャパシタ(242)を形成する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置、例えばSRAMのメモリセルのα線によるソフトエラーを低減する。

【解決手段】基板1aをエッチングして第1配線溝HM1を形成し、第1配線溝HM1下の素子分離2(または素子分離溝2および絶縁層1c)をエッチングして第2配線溝HM2を形成し、第1配線溝HM1および第2配線溝HM2の内壁に沿って局所配線16a,16bを形成し、一方の局所配線16aを下部電極ELとして、その下部電極EL上に容量絶縁膜となる窒化シリコン膜17、さらに上部電極EUを形成することにより、容量CA1の面積を増加させて、メモリセルの記憶ノードに相対的に大きな静電容量を付加する。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、低抵抗であって且つ絶縁膜及び配線との間で高い密着性を有するバリアメタル膜を有する半導体装置を提供する。

【解決手段】 半導体装置は、基板(1)上に形成された絶縁膜(6,8)と、絶縁膜(6,8)中に形成された埋め込み配線(14)と、絶縁膜(6,8)と埋め込み配線(14)との間に形成されたバリアメタル膜(A1)とを有する。バリアメタル膜(A1)は、絶縁膜(6,8)が存在している側から埋め込み配線(14)が存在している側へ向かって順に積層されている金属酸化物膜(11)、遷移層(12a)及び金属膜(13)よりなり、遷移層(12a)は、金属酸化物膜(11)の組成と金属膜(13)の組成とのほぼ中間的な組成を有する単一の原子層よりなる。

(もっと読む)

相互接続構造の製造方法

【課題】 従来のデュアル・ダマシンとULK IMD材料との統合が有する問題を解決するための相互接続構造を形成する方法を提供する。

【解決手段】 相互接続構造は、原子層堆積又は超臨界流体ベースのプロセスによって薄いコンフォーマルな不動態化誘電体及び/又は拡散障壁キャップ及び/又はハード・マスクを堆積させるステップを含む方法により製造される。

(もっと読む)

接触抵抗が低減された半導体デバイス

【課題】パワー半導体デバイスの電気抵抗を小さくする。

【解決手段】 第1の導電性の材料から構成され、表面に電極を有する半導体ダイと、前記第1の導電性の材料の抵抗率よりも低い抵抗率を有する第2の材料から構成され、前記電極の上に設けられた導電性本体とを備える半導体デバイスと、第1の導電性の材料から構成された、半導体デバイスの電極の表面にバリア層を形成するステップと、前記第1の材料の電気抵抗率よりも電気抵抗率が低い第2の導電性の材料から構成されたシード層を、前記バリア層の上に形成するステップと、前記第2の材料から構成された前記シード層の上に導電製本体を形成するステップとを有する、半導体デバイスを製造するための方法に関する。

(もっと読む)

スパッタ反応装置内で金属バリアを形成するために特にマルチステッププロセスで使用される可変四重電磁石アレー

スパッタチャンバ(70)及びそれが可能にするマルチステッププロセス。チャンバ軸と同軸な四重電磁石矩形アレー(72)はチャンバ内のRFコイル(46)の裏側にあることが好ましい。異なる磁場分布を生成するために、例えば、ターゲット材料をウエハ(32)上にスパッタするためにスパッタターゲット(38)が給電されるスパッタ堆積モードとRFコイルがアルゴンスパッタリングプラズマをサポートするスパッタエッチングモードとの間でコイル電流を個別に制御できる。ターゲット材料のRFコイルにおいては、コイルにDCバイアスをかけることができ、コイルアレーがマグネトロンとしての機能を果たす。このようなプラズマスパッタチャンバ内で行なわれるマルチステッププロセスは、様々な条件下でのターゲットからのバリア材料のスパッタ堆積と、基板のアルゴンスパッタエッチングとを含んでいてもよい。ターゲット電力及びウエハバイアスの減少を伴うフラッシュステップが適用される。 (もっと読む)

アクティブマトリクス基板、その画素欠陥修正方法及び製造方法

【課題】異物や膜残り等によるソース電極とドレイン電極との短絡、ドレイン電極やドレイン引出配線の断線及びTFT動作不良等による画素欠陥に対して、開口率を減少させることなく、点欠陥となる画素を容易かつ確実に修正することができ、液晶表示装置の歩留りを向上させることができるアクティブマトリクス基板を提供する。

【解決手段】基板上に、複数本の走査信号線及びデータ信号線と、信号線の交点に設けられ、ゲート電極が走査信号線に接続され、ソース電極がデータ信号線に接続された薄膜トランジスタと、上記薄膜トランジスタのドレイン電極又はドレイン引出配線に接続された画素電極とを備えるアクティブマトリクス基板であって、上記アクティブマトリクス基板は、データ信号線が少なくとも部分的に複線化された構造を有し、かつ修正用接続電極を備えるアクティブマトリクス基板である。

(もっと読む)

感光性誘電体層を分解することによる相互接続構造の形成

本発明は、感光性材料の層が直接にパターン化される方法を提供する。その後、感光性材料は、少なくとも部分的に分解され、層内にボイドまたは空隙を残し、低減された抵抗キャパシタンス遅延特性を有する低誘電率の層を提供する。  (もっと読む)

(もっと読む)

イオン化物理蒸着方法

iPVDシステム(200)は、真空チャンバー(30)内で突出部(14)を最小化または除去しながら、フィールド(10)と底部(15)被覆と比較して側壁(16)被覆性を向上させる処理を用いて、障壁層材料(912)のような均一な材料を半導体基板(21)上の高いアスペクト比のナノサイズの開口部(11)に蒸着するために調整される。そのiPVDシステム(200)は、そのターゲットから材料をスパッタするために、低いターゲットパワーと50mTより高い圧力で動作される。RFエネルギーは、高密度プラズマを生成するそのチャンバーに連結される。小さなRFバイアス(数ボルト未満)は、特に、底部における被覆性を高めることを助けるために印加されることができる。  (もっと読む)

(もっと読む)

メモリセル形成のためのインサイチュ表面処理

有機メモリセルの製造中などに実施されうるものなど、導電層上にパッシブ層を形成するためのシステムおよび方法が開示され、これは、一般に、従来の無機メモリデバイスに固有の不具合を低減させる。パッシブ層は硫化銅(Cu2S)などの導電促進化合物を含み、これは、導電材料の上部から形成される。この導電材料はメモリセルにおいて下部電極として作用し、導電材料の上部が、フッ素(F)系ガスから生成されたプラズマによる処理によってパッシブ層に変換されうる。  (もっと読む)

(もっと読む)

エッチング残渣を除去するための水溶液

本発明は、エッチング残渣を除去するための改善された特性を有する新規溶液及び半導体製造におけるその使用に関する。本発明は、特に、半導体の製造プロセスの間にエッチング残渣及びパーティクルを除去しなければならないメタライジング部に対して及び表面に対して低いエッチング速度を有する水溶液に関する。 (もっと読む)

高度に選択的な酸化ケイ素エッチング組成物

少なくとも一種のカルボン酸からなる溶媒中に溶解した少なくとも一種の酸性フッ化物供給源化合物の生成物を含有し、更に約(0.5)〜約(3)溶液重量%のフッ化水素酸と約(1)〜約(5)溶液重量%の水とを含む酸化ケイ素エッチング溶液であって、ここで酸性フッ化物供給源化合物の総濃度は、溶媒1キログラム当たり約(1.25)〜約(5.0)モルである、前記酸化ケイ素エッチング溶液。金属表面から酸化ケイ素と金属のケイ酸塩とを選択的に除去する方法も開示する。 (もっと読む)

CMP後洗浄用の改善された酸性化学剤

本開示は、半導体装置の製造中における化学的機械的平坦化(CMP)後の半導体ウエハの洗浄を検討する。金属特に銅の相互接続を含有するウエハのCMP後洗浄のための酸性化学剤が開示されている。残存スラリー粒子、特に銅または他の金属粒子は、金属を有意にエッチングすることなく、表面に付着物を残すことなく、または有意の有機(炭素のような)汚染質を表面に与えることなく、しかも金属を酸化および腐食から保護しながら、表面から除去される。さらに、溶液中の金属イオンを錯化し、誘電体からの金属の除去を促進し、ウエハ上への再付着を防止するために、少なくとも1種の強力なキレート化剤が存在する。酸性化学剤を用いると、CMP後に使用される洗浄溶液のpHをウエハ表面で使用された最後のスラリーのそれとマッチさせることができる。 (もっと読む)

カーボンナノチューブ複合材相互接続ビアを用いた集積回路チップ

【課題】 カーボンナノチューブを用いて集積回路の導電性パスを形成することによって、好結果のデバイスを設計する。

【解決手段】 集積回路の導電体パスが、銅であることが好ましい導電性金属に埋設された複数の画一的なカーボンナノチューブを用いて形成される。導電体パスは、導電体層の間に延びるビアを含むことが好ましい。複合材ビアは、導電体上のビアが作られる位置に金属触媒パッドを形成するステップと、誘電体層を堆積しエッチングして空洞部を形成するステップと、空洞部内の触媒の上に実質的に平行なカーボンナノチューブを成長させるステップと、残された空洞部内の空隙を銅で埋めるステップによって形成されることが好ましい。次に、ビア・ホールの上に導電体層が形成される。

(もっと読む)

炭素含有アンチヒューズ材料を使用した再プログラム可能な金属−金属間のアンチヒューズ

金属−金属間のアンチヒューズが集積回路内の2つの金属相互接続層の間に配置される。下側のバリア層はTiから形成される。下側の付着力促進層は下側のTiバリア層の上に配置される。アモルファス炭素、および、水素およびフッ素の少なくとも1つによりドープされたアモルファス炭素のうち少なくとも1つを有するグループから選択されたアンチヒューズ材料層が、下側の付着力促進層上に配置される。上側の付着力促進層がアンチヒューズ材料層の上に配置される。上側のTiバリア層が上側の付着力促進層の上に配置される。  (もっと読む)

(もっと読む)

補強された内部接続メタライゼーションを有するワイヤボンディングされた半導体部品

ドープされたシリコン基板製の半導体チップ2を含む半導体部品であって、前記チップは、半導体デバイスの中へドープされて構造化され、そして、コンタクトウインドウ中に内部接続メタライゼーション7を含み、前記半導体チップの前記内部接続メタライゼーションは、ワイヤボンド接続9によって、各外部接続メタライゼーションと接続され、前記内部接続メタライゼーションは、前記ドープされたシリコン基板上に開放格子構造体を有する補強システム8を含むことを特徴とする半導体部品。  (もっと読む)

(もっと読む)

レーザ除去タングステン・ヒューズ用配線保護要素(電気的構造体および形成方法)

【課題】集束放射線(52)によるヒューズ・リンク除去中に電気的構造体(25)を保護するための構造および対応する形成方法を提供すること。

【解決手段】構造体(1)は、ヒューズ要素(2)と、保護プレート(10)と、第1誘電体層(14)と、第2誘電体層(4)とを含む。構造体(1)は、半導体デバイス(5)内に形成される。保護プレート(10)は、ダマシン・プロセスを使用して第1誘電体層(14)内に形成される。第2誘電体層(4)は、保護プレート(10)および第1誘電体層(14)上に形成される。ヒューズ要素(2)は、第2誘電体層(4)上に形成される。ヒューズ要素(2)は、レーザビーム(52)で切断されるように構成される。第2誘電体層(4)の誘電率は、第1誘電体層(14)の誘電率より大きい。保護プレート(10)は、第1誘電体層(14)をレーザビーム(52)のエネルギーから遮蔽するように構成される。

(もっと読む)

2,541 - 2,560 / 2,592

[ Back to top ]