Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

2,561 - 2,580 / 2,592

半導体装置及びその製造方法

底部電極(11)及び又はキャパシタ誘電体上に導電性平滑化層(16、19)を形成することにより、幾何学的に高くされた電場を低下させると共に、電極を平滑化することで、形成されるMIMキャパシタの信頼性を向上させることができる。一実施形態において、難溶性窒化物で形成された第1のキャッピング層(14)上には、難溶性金属又は難溶性金属リッチ窒化物を含む第1の層(16)が形成される。更に、キャパシタ誘電体上には、難溶性金属(18)又は難溶性金属リッチ窒化物を含む第2の層(19)が形成される。導電性平滑化層(16、19)は、例えば、ゲート電極とゲート誘電体との間のトランジスタ等の他の半導体装置にも使用される。  (もっと読む)

(もっと読む)

金属の化学的機械的研磨用の新規なスラリー

一般に集積回路の製造に有用な、金属を取り除くための、及び、特に貴金属の化学的機械的研磨用の、スラリーは、過ヨウ素酸、研磨剤、及び緩衝系を組み合わせることによって、形成されてもよく、ここでそのスラリーのpHは、約(4)と約(8)との間にある。

(もっと読む)

(もっと読む)

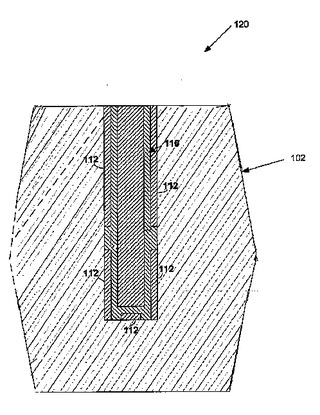

無電解メッキ化学反応を用いた深いビアシードの修復

高アスペクト比ビア内に連続シード層を形成する方法とそれに関連付けられる構造体を記載する。この方法は、基板内に凹部(104)を形成する段階と、凹部内に非連続金属層を形成する段階と、凹部内の非連続金属層(112)と、少なくとも1つの非堆積領域(109)を活性化させる段階と、凹部内の非連続金属層及び少なくとも1つの非堆積領域上にシード層(116)を無電解メッキする段階と、実質的にボイドがなく、金属が充填された凹部を形成するようシード層上に金属充填層を形成する段階を含む。  (もっと読む)

(もっと読む)

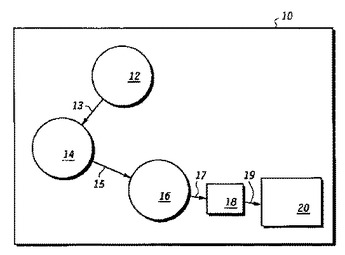

無電解堆積のエンドポイントを検出するための装置および方法

基板の表面に向けて電磁放射を方向付けて、該基板の該表面上の部材から反射された該電磁放射の強度の変化を1つ以上の波長で検出することによって無電解堆積プロセスをコントロールするための装置および方法。一実施形態において、該基板が検出機構に対して移動されると、無電解堆積プロセスステップの検出された終了が測定される。別の実施形態において、多数の検出ポイントが、該基板の該表面にわたる該堆積プロセスの状態を監視するために使用される。一実施形態において、該検出機構は該基板上で無電解堆積流体に浸される。一実施形態において、コントローラは、記憶されたプロセス値、異なる時間に収集されたデータの比較、および種々の算出された時間依存データを使用して無電解堆積プロセスを監視、記憶および/またはコントロールするために使用される。 (もっと読む)

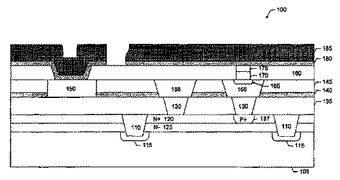

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

能動領域ボンディングの両立性のある高電流構造体

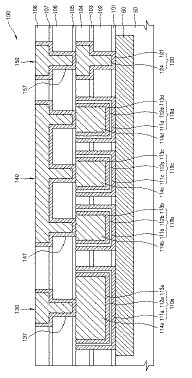

ボンディング・パッド下方に各回路を有する集積回路。一実施例において、集積回路は基板と、最上部導電層と、1つ以上の中間導電層と、絶縁材料から成る各層と、各デバイスとを具備する。最上部導電層は少なくとも1個のボンディング・パッド及び比較的硬質の材料から成る副層を有する。1つ以上の中間導電層は最上部導電層及び基板の間に形成する。絶縁材料から成る各層は各導電層を分離する。更に、絶縁材料から成る各層のうちの1つの層は比較的硬質で、最上部導電層及びこの最上部導電層に最も近接した中間導電層の間に位置する。各デバイスは集積回路に形成する。また、最上部導電層に最も近接した少なくとも中間導電層は、ボンディング・パッド下方の各選択デバイスの機能的相互接続部に対して適合する。

(もっと読む)

(もっと読む)

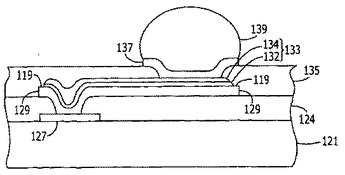

ボンドパッドの形成方法

パッシベーション層(68)及びポリイミド層(72)の下層には、ボンドパッド層(62)を覆うように最上層(64)が形成される。パッシベーション層(68)及びポリイミド層(72)の内部には、開口部(70,74)の形成時にボンドパッド層(62)を保護する最上層(64)を露出させるように、開口部(70,74)が形成される。一実施形態において、露出した最上層(64)は、過酸化水素及び水酸化アンモニウム等のアミンを用いて選択的にエッチングされる。この化学系は、ボンドパッド層(62)に攻撃を加えないため、ボンドパッド層の薄化が回避される。従って、ボンドパッドの信頼性が維持される。  (もっと読む)

(もっと読む)

金属−絶縁物−金属キャパシタおよび配線構造

【課題】 金属−絶縁物−金属キャパシタおよび配線構造を提供する。

【解決手段】 ダマシン工程を利用してMIMキャパシタおよび配線構造を含む半導体装置を製造する。前記MIMキャパシタおよび配線構造は静電容量を増やしつつ同じ深さで形成する。

(もっと読む)

チタン・タングステンのベース層および関連構造体を含む導電構造体を形成する方法

基板、基板上の導電パッド、および基板上の絶縁層を含む電子デバイスを形成する方法であって、上記絶縁層は導電パッドの一部を露出するバイアホールを有する。詳細には、絶縁層上であり導電パッドの露出部分上に導電構造体を形成できる。導電構造体は、チタン・タングステン(TiW)のベース層と、アルミニウムおよび/または銅のうちの少なくとも1つの導電層とを含みうる。さらに、導電構造体のベース層を、導電層と絶縁層との間に形成できる。関連デバイスについても説明する。

(もっと読む)

(もっと読む)

ビア開口部中に形成されるポリマーメモリデバイス

本発明は、ビア内にポリマーメモリデバイスを製造する方法に関する。この方法は、少なくとも1つの金属を含む層をその上に備える半導体基板を提供するステップと、この金属を含む層中に少なくとも1つの銅コンタクトを形成するステップと、銅コンタクト上に少なくとも1つの絶縁層を形成するステップと、絶縁層に少なくとも1つのビアを形成し、銅コンタクトの少なくとも一部を露出するステップと、ビアの下側部分にポリマー材料を形成するステップと、ビアの上側部分にトップ電極材料層を形成するステップとを含む。  (もっと読む)

(もっと読む)

バリヤ金属上に直接銅めっきするマルチステップ電着法

本発明の実施形態は、基板表面に、通常はバリヤ層に銅シード層を堆積させる方法を教示している。その方法は、基板表面を銅溶液に入れるステップであって、該銅溶液が錯体形成銅イオンを含んでいる、前記ステップを含んでいる。電流又はバイアスを基板表面に印加し、錯体形成銅イオンを還元してバリヤ層に銅シード層を堆積させる。 (もっと読む)

半導体デバイスを製造する方法およびその方法で使用するための装置

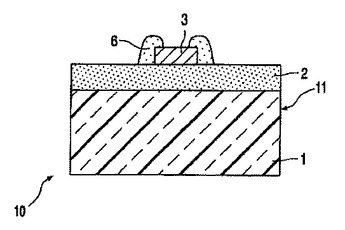

本発明は、基板(1)および少なくとも1つの半導体要素を含んだ半導体本体(11)を有した半導体デバイス(10)の製造方法に関する。その方法では、要素の形成後、少なくとも1つの電気的絶縁層(2)または電気的導体層(3)を含んだ層構造が形成され、開口部が、パターン形成されたフォトレジスト層(4)およびエッチング・プロセスの助けによって層構造中に形成され、残渣が、エッチング・プロセス中に半導体本体(11)の表面上に形成され、エッチング・プロセス後に、フォトレジスト層(4)が、酸素含有化合物を使用する処理によって灰にされ、その後、表面が、酸を水で希釈した溶液を含んだ洗浄剤を、室温より高い温度に加熱して使用する洗浄作業を受け、それによって形成された残渣が除去される。本発明によれば、硫酸が、洗浄剤用の酸として選択される。  (もっと読む)

(もっと読む)

半導体装置

【課題】ESD 保護回路のサージ電流経路に使用される配線層に生じる熱を効率よく放熱でき、サージ電流経路に使用される配線層も保護する。

【解決手段】外部端子と内部回路との間の配線に接続され、外部端子に印加された過大な静電サージ入力から内部回路を保護する保護素子を有する入力保護回路と、入力保護回路に接続され、そのサージ電流経路に含まれる第1のメタル配線層25と、第1のメタル配線層に連なり、熱伝導性が良好な材質の配線を用いてなる放熱器20とを具備する。

(もっと読む)

半導体製造プロセスの過程で導電面を不動態化するための方法

半導体ウェハの製造プロセスが開示されている。メタル配線の表面に発生するデンドライトや電気分解反応を抑止するため、半導体ウェハに対して溶液が適用される。その溶液は、CMP処理の際又はCMP洗浄後処理の際に適用される。その溶液は、界面活性剤及び防食剤を含む。一実施形態では、その溶液中に含まれる界面活性剤の濃度が約1重量パーセント未満に設定され、防食剤の濃度が約1重量パーセント未満に設定される。また、その溶液は、溶媒及び共溶媒を含むこともできる。別の実施形態では、その溶液が、界面活性剤及び防食剤を含まず、溶媒及び共溶媒を含む。一実施形態では、CMP処理及びCMP洗浄後処理を、約1μm未満の波長を持つ光の存在下で実施できる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】段差が存在する下地上でAl合金配線を形成するためのエッチング時にイオンシェーディング現象の発生を抑制してAl合金配線の側面が逆テーパー形状となるのを抑制できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、段差を有する下地である層間絶縁膜11上にTi層を形成する工程と、このTi層上にAl層又はAl合金層を形成する工程と、熱処理を行うことにより、Ti層とAl層又はAl合金層を合金化反応させてAl3Ti層5aを形成する工程と、このAl3Ti層5aの上にレジストパターン12を形成する工程と、このレジストパターン12をマスクとしてAl3Ti層5aをエッチングすることにより、層間絶縁膜11上にAl合金配線13を形成する工程と、を具備するものである。

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

絶縁膜形成用塗布液とそれを用いた半導体装置

【課題】配線の信号伝播性能向上を絶縁被膜の誘電率分布の均一化によって実現することを課題とする。

【解決手段】アルコキシシランを加水分解して得られたシリカからなる、平均粒径が1000Å以下であって、粒径の3σが平均粒径の20%以下である第一の微粒子と、平均粒径が1第一の微粒子の1/3以下で、粒径の3σが第二の微粒子の平均粒径の20%以下である第二の微粒子とを含有し、半導体デバイスに用いるに好ましい被膜形成用塗布液。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの下層におけるクラックの発生を抑制しつつ、ボンディングパッドの下層を有効活用して装置の小型化を図る。

【解決手段】半導体装置10は、半導体基板11と、外部との電気的接続をとるための接続領域12aを有するボンディングパッド12と、半導体基板11とボンディングパッド12との間に介在する第1層間絶縁層13と、第1層間絶縁層13に埋設されたメタル配線層14とを備える。メタル配線層14は第1層間絶縁層13より硬度の小さい材質からなる。メタル配線層14の少なくとも一部は、積層方向において接続領域12aと重なり、接続領域12aと重なるメタル配線層14の領域には、積層方向に貫通し、メタル配線層14をその層方向において分離している切欠部30a〜30eが形成されているとともに、この切欠部30a〜30eに第1層間絶縁層13の一部が埋め込まれている。

(もっと読む)

配線構造

【課題】 高い周波数が印加され、数cm〜数10cmの長さを有する配線の抵抗を低減し、伝送される信号波形のなまりを低減する。

【解決手段】 高周波が印加される配線111は、層間絶縁膜107を介して、配線111の線方向にそって複数設けられたコンタクトホールにより配線106と電気的に並列接続している配線構造を採用する。その配線構造を周辺回路一体型アクティブマトリクス型液晶表示装置の周辺回路に用いることで、高周波信号が印加される配線において信号波形のなまりを低減できる。

(もっと読む)

配線構造並びにその形成方法及び装置

【課題】 凹部への埋め込み性が良好で、長期に亘り安定した良好な電気的特性を得ることができ、さらに作製工程を可及的に低減し得る配線構造を提供する。

【解決手段】 Cu板と基板3との温度及び温度差を所定通りに制御しつつ、原料ガスであるCl2 ガスのプラズマによりCu板をエッチングすることによりCu成分とCl2 ガスとの前駆体であるCuClを形成し、この前駆体が基板3に吸着され、その後Cu成分を析出させることによりCuの薄膜を形成する成膜反応と、この成膜反応により形成されたCu膜をCl2 ガスのプラズマでエッチングするエッチング反応とを共存させるとともに、前記成膜反応の速度が前記エッチング反応の速度よりも大きくなるように制御することにより前記凹部3aにその底部から順にCu膜を積層してこの凹部3aにCuを埋め込んだ。

(もっと読む)

2,561 - 2,580 / 2,592

[ Back to top ]