Fターム[5F033HH18]の内容

半導体集積回路装置の内部配線 (234,551) | 単一配線層の材料,層間接続の上層配線層の材料 (33,767) | 金属及びその合金(シリサイドを除く) (23,853) | 高融点金属 (8,733) | Ti (2,592)

Fターム[5F033HH18]に分類される特許

2,481 - 2,500 / 2,592

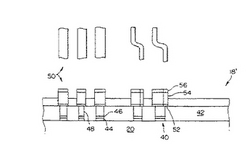

反射防止コーティング及び積層配線ライン

【解決手段】 チタニウム−アルミニウム−窒素(「Ti−Al−N」)が半導体基板上に積層されて反射防止コーティングとしての役割を果たす。配線ラインの実施の形態に対して、アルミニウム導電層(54)及びアルミニウム−チタニウム下層(52)は、反射防止キャップ層の下に形成される。

【効果】 配線ライン製造プロセスに対して、Ti−Al−N層は、製造中の不要なフォトリソグラフ光(即ち、光子)の反射を防止するキャップ層(56)としての役割を有する。電界放射ディスプレイ装置(FED)(150)に対して、Ti−Al−N層は、ディスプレイスクリーン(118)のアノードに由来する光がトランジスタ接合部を通過して装置動作を妨害するのを防止する。Ti−Al下層は熱処理中にアルミニウム導電層に起きる収縮を低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】 容量値の均一性が高い容量素子を備える半導体装置およびその製造方法を提供する。

【解決手段】 半導体装置1の容量素子形成領域20において、P型の半導体基板10の表層には、導電層としてN型ウエル22が形成されている。N型ウエル22が形成された半導体基板10の表面には、容量膜24が成膜されている。ここで、半導体基板10表面における容量膜24が成膜された部分は、実質的に平坦である。容量膜24上には、上部電極26が設けられている。上部電極26は、容量膜24を挟んで対向するN型ウエル22との間で容量素子(オンチップキャパシタ)を構成している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】 配線抵抗を低減させながら歩留まりを向上させたバリアメタル膜を形成することを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜に開口部を形成する開口部形成工程(S110)と、PVD法を用いて、前記絶縁膜上と開口部内とに第1のバリアメタル膜を形成する第1のバリアメタル膜形成工程(S116)と、その上に、CVD法を用いて第2のバリアメタル膜を形成する第2のバリアメタル膜形成工程(S118)と、その上に、PVD法を用いて第3のバリアメタル膜を形成する第3のバリアメタル膜形成工程S120)と、その上に、導電性材料を堆積させる堆積工程(S112,S124)と、を備え、前記絶縁膜上に形成された前記第1と第2と第3のバリアメタル膜の合計膜厚が、8nmより小さくなるように形成することを特徴とする。

(もっと読む)

アレイ基板の製造方法及びそれを用いた液晶表示装置の製造方法

【課題】本発明は、反射型や半透過型の液晶表示装置に用いられるアレイ基板の製造方法及びそれを用いた液晶表示装置の製造方法に関し、製造コストを削減しつつ良好な表示品質の得られるアレイ基板の製造方法及びそれを用いた液晶表示装置の製造方法を提供することを目的とする。

【解決手段】不規則な凹凸を表面に有する下地層を基板上に形成し、下地層表面に倣った凹凸を有する金属膜51を下地層上に形成し、金属膜51上に着色レジスト層を形成し、着色レジスト層をパターニングして規則的に配列する着色レジストパターン52を形成し、着色レジストパターン52の欠陥を光学的に検出するための光学検査を行い、光学検査により検出された着色レジストパターン52の欠陥を修復し、着色レジストパターン52をマスクとして金属膜51をエッチングする。

(もっと読む)

半導体装置の製造方法

【目的】 層間絶縁膜が剥離または破壊される事態が起こりにくい半導体装置の製造方法を提供することを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜上に導電性材料を堆積させる堆積工程(S114〜S118)と、堆積した前記導電性材料を所定の深さまでウェットエッチングするウェットエッチング工程(S120)と、ウェットエッチングされた前記導電性材料を研磨する研磨工程(S122)と、を備えたことを特徴とする。

(もっと読む)

電解研磨のためのシステムと方法

【課題】電解研磨のためのシステムと方法を提供する。

【解決手段】本発明は、半導体ウェハの導電性表面を電解研磨する処理を提供する。この処理中、コンタクト溶液中のコンタクト電極は、導電層の表面上のコンタクト領域にコンタクト溶液を接触させる。さらに、この処理中、処理溶液中の処理電極は、導電性表面上の処理領域に処理溶液を接触させ、同時に、コンタクト電極と処理電極との間に電位差を与えて、処理領域の導電層の表面を電解研磨する。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】 ヴィア(ヴィアコンタクト)の加工形状を均一にすることを目的とする。

【構成】 第1の配線層と、前記第1の配線層の上方に形成された第2の配線層と、前記第1の配線層と前記第2の配線層との間のヴィア層に配置され、前記第2の配線層下面から前記第1の配線層上面まで導電性材料が堆積したヴィア20と、前記第1の配線層と前記第2の配線層との間のヴィア層に配置され、前記第2の配線層下面から前記ヴィア層の途中まで導電性材料が堆積した、前記ヴィア20より径の小さなヴィア22と、を備えたことを特徴とする。

(もっと読む)

半導体素子の金属配線形成方法

【課題】エッチング停止膜のアンダーカットなどのプロファイル不良を防止する半導体素子の金属配線形成方法を提供する。

【解決手段】半導体素子の金属配線形成方法は、まず、導電性パターンが埋め込まれている基板上に、エッチング阻止膜121,122及び絶縁膜131,132を順次に形成する。次いで、絶縁膜をパターニングしてエッチング阻止膜を露出させる開口部を形成する。次いで、開口部の内面に沿って第1拡散防止膜161を形成する。次いで、スパッタリング方式のエッチングを通じて、開口部の底面の第1拡散防止膜及びエッチング阻止膜を除去する。次いで、導電性パターンと電気的に連結される導電物質を、開口部に埋め込む。

(もっと読む)

半導体基板洗浄用組成物を用いた半導体装置製造方法

【課題】不純物の除去力を向上させながらも、金属層の損傷を最小化することができる半導体基板洗浄用組成物を用いた半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法において、半導体基板上に金属を含む構造物パターン形成し酸性水溶液78ないし99.98質量%、第1キレート剤0.01ないし11質量%を含む半導体基板洗浄用組成物を、半導体基板に適用して構造物パターンの不純物が覆っていない第1表面部位上に第1腐食抑制膜を形成し、構造物パターンの不純物が覆っている第2表面部位上の不純物を除去する。

(もっと読む)

スタックされた有機メモリデバイス及びその製造及びオペレーション方法

本発明は、多層の有機メモリデバイス(10,24,28,34,54,58,74,78,100,700,704)を与え、非揮発性メモリデバイスとしてオペレートし得るし、その中に構築された複数のスタックされた及び/又はパラレルメモリを有する。複数セルと多層有機メモリコンポーネント(30,34,50,54,70,74)は、2あるいはそれ以上の電極(110,122,132,140,220,244,332,348,432,448,514,560,616,704,710)で形成され得るし、電極間(110,122,132,140,220,244,332,348,432,448,514,560,616,704,710)に選択的導電媒体(706,708)を有し、個々のセルを形成する。一方でパーティションコンポーネント(40,44,48,60,64,68,80,84,88)を、先に形成されたセルの上部に又は関連して追加のメモリセルをスタックすることを可能にするために利用する。メモリスタック(30,34,50,54,70,74)は、追加の層−追加のパーティションコンポーネントによって分離された各層を加えることによって形成され得るし、複数スタックが高密度メモリデバイスを与えるために併存して形成され得る。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 ボイドの移動経路となるバウンダリーが顕著に低減されるため、SIV不良の発生を効果的に抑制することができ、信頼性の高い半導体装置を提供する。

【解決手段】 相対的に広幅の第2銅配線110,126の上面において、銅のグレインが数10μm程度と非常に大きい。第2銅配線110,126の配線幅は0.3μm〜数10μm程度であるので、第2銅配線110,126の上面において配線幅方向のバウンダリーが顕著に低減され、第2銅配線110,126とビア113との接続部分にボイドが集中・合一して大きなボイドが形成されることを抑制することができ、SIVの発生が効果的に抑制される。相対的に狭幅の第1銅配線111,127の面方位はEM耐性を向上させるために主にCu(111)であり、相対的に広幅の第2銅配線110,126の面方位はSIV耐性を向上させるために主にCu(200)である。

(もっと読む)

成膜方法

【課題】 金属と窒素と炭素を含む第1の処理ガスと、当該第1の処理ガスを還元する第2の処理ガスを交互に供給して薄膜を形成する成膜方法において、前記薄膜に含まれる、前記金属、窒素、および炭素のうち、少なくともいずれか一つの含有率の制御することを可能とすること。

【解決手段】 被処理基板を保持する保持台を内部に備えた処理容器に、金属と窒素と炭素を含む第1の処理ガスと、当該第1の処理ガスを還元する第2の処理ガスを供給し、前記被処理基板上に薄膜を形成する成膜方法であって、前記処理容器に前記第1の処理ガスを供給する第1の工程と、前記処理容器に前記第2の処理ガスを供給し、前記処理容器に設けられたプラズマ励起手段によって当該第2の処理ガスをプラズマ励起する第2の工程と、を有し、前記プラズマ励起手段に印加される高周波電力を変更することにより、前記薄膜に含まれる、前記金属、窒素、および炭素のうち、少なくともいずれか一つの含有率を制御することを可能としたことを特徴とする成膜方法。

(もっと読む)

ハイパフォーマンスメタライゼーションキャップ層

【課題】 ハイパフォーマンスメタライゼーションキャップ層を提供する。

【解決手段】 非導電性のキャップ層を有する半導体デバイス100の、第一金属成分からなる非導電性のキャップ層112は、導電線と導電線間の絶縁材料上の、第一窒化金属、第一酸化金属、或いは、酸窒化金属からなる。界面領域114は、導電線の上表面上に形成され、界面領域114は、キャップ層の金属成分を含む。キャップ層112は、導電線中の導電材料が、近接する絶縁材料層中に移動、或いは、拡散するのを防止する。キャップ層112は、エッチ停止層としても機能する。

(もっと読む)

半導体装置およびその製造方法

【課題】 誘導素子を備え、エネルギー損失が少なく、特性が優れた半導体装置を得る。

【解決手段】 表面に電極3が設けられた半導体基板1と、半導体基板1を覆うように設けられ、電極3と整合する位置に第1の開口部16を有する第1の絶縁樹脂層11と、第1の絶縁樹脂層11の上に設けられ、第1の開口部16を介して電極3と接続された第1の配線層12と、第1の絶縁樹脂層11及び第1の配線層12を覆うように設けられ、半導体基板1の表面に沿う位置が第1の開口部16とは異なる位置に開口した第2の開口部17を有する第2の絶縁樹脂層13と、第2の絶縁樹脂層13上に設けられ、第2の開口部17を介して第1の配線層12と接続された第2の配線層14とを有する半導体装置10であって、第2の配線層14は誘導素子15を有し、第1の絶縁樹脂層11と第2の絶縁樹脂層13との層厚の和が5μm以上60μm以下である。

(もっと読む)

半導体装置の製造方法、半導体装置、及び電子機器

【課題】 積層された半導体チップの接合強度が高く、これにより高い信頼性を確保することができる半導体装置の製造方法及び半導体装置、並びに当該半導体装置を備える電子機器を提供する。

【解決手段】 半導体基板10を貫通する電極20,21を有する半導体装置の製造方法であって、集積回路が形成された半導体基板10の能動面10aから半導体基板10の内部にかけて孔部H3を形成する工程と、孔部H3の内側に導電材料を充填して第一接続端子20を形成する工程と、半導体基板10を裏面側10bから薄板化して、電極20の先端部を露出させる工程と、先端部の周辺に導電材料を配置して第二接続端子21を形成する工程と、を有する。

(もっと読む)

研磨方法及び半導体装置の製造方法

【課題】 気密性を保ったままスラリや洗浄薬液などの溶液を研磨布上などに供給させることにより供給寸前まで外気との接触を避け、ウエハの欠陥を低減することができる研磨方法及び半導体装置の製造方法を提供する。

【解決手段】 スラリ保持容器からスラリ16をウエハ15上の被研磨対象物に供給する工程と、前記被研磨対象物を研磨する工程とを備える。スラリ保持容器は、密封容器であり、スラリの残量によって容積を可変にすることにより容器内のスラリが外気と接することがないように構成された気密性可変容器10を用いる。スラリが完全に密閉された容器に収容され、気密性を保ったまま被研磨対象物に供給されるので、供給寸前まで外気との接触を避けてダストの混入やバクテリアの増殖、成分の揮発などを防ぐことが可能となり、スラリ等の粗大粒子を低減できる。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッド部のパッド剥がれを抑制した半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、層間絶縁膜8上にバリアメタル層14を形成する工程と、パッド開孔部の下に位置する前記バリアメタル層の少なくとも一部を除去する工程と、前記除去する工程により露出した層間絶縁膜8及び前記バリアメタル層14の上に第2のAl合金膜15を形成する工程と、第2のAl合金膜及び前記バリアメタル層をパターニングすることにより、前記層間絶縁膜上にボンディングパッド部17aを形成する工程と、前記ボンディングパッド部及び前記層間絶縁膜の上にパッシベーション膜18を形成する工程と、前記パッシベーション膜に、前記ボンディングパッド部上に位置するパッド開孔部を形成する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】コリメータを備えるスパッタリング装置の生産効率を向上させることのできる技術を提供する。

【解決手段】上部シールド13の上部折曲部13aと下部折曲部13bとの上下垂直位置の距離を相対的に短く、上部シールド13の下縁部の内径を相対的に広くして、ターゲット3と上部シールド13との間の隙間量を相対的に広くし、さらに台座リング15の内径を相対的に広く、台座リング15の高さを相対的に低くして、パッキングプレート11(ターゲット3)と台座リング15との間の隙間量を相対的に広くすることにより、ターゲット3と上部シールド13との接触またはパッキングプレート11(ターゲット3)と台座リング15との接触を回避する。

(もっと読む)

非結晶性炭素膜を犠牲ハードマスクとして用いる半導体素子の製造方法

【課題】 本発明は、犠牲ハードマスクのエッチング選択比を増加させ、パターン変形を最小化できる半導体素子の製造方法を提供すること。

【解決手段】 本発明は、被エッチング層上に犠牲ハードマスク用の非結晶性炭素膜を形成するステップと、該犠牲ハードマスク用の非結晶性炭素膜上にフォトレジストパターンを形成するステップと、該フォトレジストパターンをエッチングマスクとして前記犠牲ハードマスク用の非結晶性炭素膜をエッチングし、犠牲ハードマスクを形成するステップと、少なくとも前記犠牲ハードマスクをエッチングマスクとして前記被エッチング層をエッチングし、所定のパターンを形成するステップとを含む。

(もっと読む)

充填金属部付き基板の製造方法および製造装置ならびに充填金属部付き基板

【課題】微細孔に金属を充填するにあたり、微細孔内への異物の侵入をなくす。

【解決手段】一方の面4に開口してなる微細孔5を備え、前記一方の面4および前記微細孔5の内面が絶縁性を有する基板1(a)を用い、前記微細孔5に金属を充填する方法であって、基板1の一方の面4に第1の金属層11を形成する第1の金属層形成工程(b)と、前記微細孔5に充填されるとともに前記第1の金属層11上を覆うように第2の金属層12を形成する第2の金属層形成工程(c)と、少なくとも備えたことを特徴とする充填金属部付き基板の製造方法による。本発明においては、さらに、第1の金属層11および第2の金属層12からなるランド部15及び/又は配線部を設けるパターニング工程を行うことができる(d)。

(もっと読む)

2,481 - 2,500 / 2,592

[ Back to top ]