Fターム[5F033JJ25]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | シリサイド (585)

Fターム[5F033JJ25]の下位に属するFターム

高融点金属のシリサイド (433)

Fターム[5F033JJ25]に分類される特許

121 - 140 / 152

半導体デバイスの製造方法および該方法で得られた半導体デバイス

本発明は、基板(11)と、少なくとも一つの半導体素子(E)を設けた半導体本体(12)とを有し、単結晶シリコン(1)領域を具え、該単結晶シリコン領域(1)の上に金属シリサイド領域(3)を設け、そして金属シリサイド領域(3)の上に低結晶性シリコン領域(4)を設け、その後、低結晶性シリコン領域(4)を加熱することにより高結晶性を有するエピタキシャルシリコン領域(2)に変化させ、その処理の間に金属シリサイド領域(3)を低結晶性シリコン領域(4)の下部からエピタキシャルシリコン領域(2)の上へと移動させることにより、単結晶シリコン領域(1)の上にエピタキシャルシリコン領域(2)を形成する、半導体デバイス(10)の製造方法に関する。上記本発明によれば、金属シリサイド領域(3)より高い位置に、孔(6)を設けた絶縁層(5)を形成し、低結晶性シリコン領域(4)を孔(6)中および絶縁層(5)の上に析出させ、絶縁層(5)上の低結晶性シリコン領域(4)の一部(4A、4B)を平坦化処理により取り除き、その後にエピタキシャルシリコン領域(2)を形成する。この方法では、自己整合方式で金属シリサイドコンタクト(領域)が設けられており、そしてトランジスタのような半導体素子(E)の一部を形成できる、エピタキシャルシリコン領域(2)、好ましくはナノワイヤ(2)が簡単に得られる。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

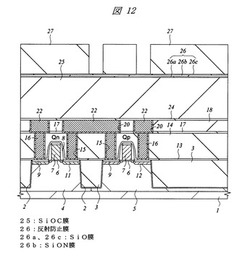

【課題】層間絶縁膜上に形成する反射防止膜の光反射率を低減することによって、デュアルダマシンプロセスにおけるリソグラフィの解像度を向上させる。

【解決手段】フォトレジスト膜をマスクにしたドライエッチングで層間絶縁膜にCu配線埋め込み用のビアホールおよび配線溝を形成する際、SiOC膜25からなる層間絶縁膜上の反射防止膜26をSiO膜26a、SiON膜26bおよびSiO膜26cの3層膜で構成し、フォトレジスト膜27のハレーションを抑制する。SiO膜26aの膜厚とSiON膜26bの膜厚の好ましい組み合わせは、SiO膜26aの膜厚が40nm以下または75nm以上、かつSiON膜26bの膜厚が40nm以上であり、より好ましくは、SiO膜26aの膜厚が30nm以下または80nm以上、かつSiON膜26bの膜厚が50nm以上である。

(もっと読む)

半導体装置

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110(プラグを構成する導電物は例えばタングステン(W))との間に、シリサイド膜111を形成する。ここでは、導電プラグ110の下地膜をシリサイド膜111とする場合を例示する。

(もっと読む)

金属相互接続構造体

【課題】 チップの金属ラインから外向き方向の、銅の所望されない輸送を低減することである。別の目的は、ビアと金属ラインとの間の界面における空隙の発生を回避又は低減することである。

【解決手段】 相互接続構造体及びその製造方法が提供される。相互接続構造体は、パターン形成された開口部を有する誘電体層と、パターン形成された開口部内に配置された金属構造と、金属構造の上に重なる誘電体キャップとを含む。誘電体キャップは、内部引張応力を有し、この応力は、特に金属ラインが引張応力を有する場合に、金属ラインから離れる方向のエレクトロマイグレーションが発生することを回避するのに役立つ。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 密着性を高める機能を併せ持つバリア層が形成されるまでの期間に、配線部材の十分な密着性を確保し、配線部材の剥離を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に、凹部が設けられた層間絶縁膜を形成する。(b)凹部の内面及び層間絶縁膜の上面に密着層を形成する。(c)密着層の表面を、第1の金属元素を含むCu合金からなる補助膜で被覆する。(d)凹部内に、第1の金属元素以外の第2の金属元素を含む導電部材を充填すると共に、補助膜の上に導電部材を堆積させる。(e)熱処理を行うことにより、補助膜内の第1の金属元素の原子を、凹部の内面に偏析させる。この密着層は、層間絶縁膜の表面上に補助膜を直接堆積させた場合に比べて、補助膜の密着性を高める元素を含む。

(もっと読む)

改良された接触パッドを有する半導体デバイスとその製造方法

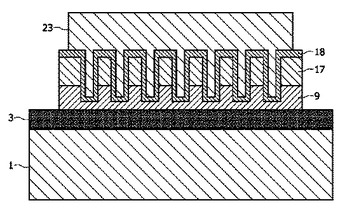

半導体デバイスおよびその製造方法が開示される。このデバイスは、1以上の導電性ゲート(11)を具えた活性半導体領域(1A)と、前記活性半導体領域(1A)の周辺に位置し主としてフィールド酸化領域(3)よりなるコンタクト領域(1B)とを具える。周辺コンタクト領域(1B)上、および、少なくとも一部の活性半導体領域(1A)上に、導電性ゲート(11)の間にコンタクト窓(19a)が形成された絶縁層(17)が積層される。絶縁層(17)上に積層された金属コンタクトパッド(23)が、前記コンタクト領域(1B)に設けられる。この金属コンタクトパッド(23)は、導電性のパターンを介して、絶縁層(17)の下に埋設されているコンタクトストリップ(15)に接触し、この導電性のパターンは、コンタクト窓(19b)充填物の複数個で構成されており、コンタクトパッド(23)の実質的な領域を横切って延びている。このパターンは平行な一連のトレンチに充填されたもので構成されているのが好ましい。  (もっと読む)

(もっと読む)

ピッチ増倍コンタクトを形成する方法

集積回路内で使用するための導電性および/または半導電性のフィーチャを形成する方法を開示する。種々のパターン転写ステップおよびエッチング・ステップをピッチ縮小技術と組み合わせて用いて、高密度実装フィーチャを生成することができる。フィーチャは、1つの方向に縮小ピッチを有し、別の方向に広いピッチを有することができる。従来のフォトリソグラフィ・ステップをピッチ縮小技術と組み合わせて用いて、たとえばビット線コンタクト(732)など、細長いピッチ縮小フィーチャを形成することができる。いくつかの実施形態では、コンタクト(732)は、マスキング材料の複数の層が上にある絶縁層(334)を設けることによって形成することができる。次に、一連の選択的に画定可能な線(124)をマスキング材料中に形成することができ、そこでその線がパターンを有する。次に、スペーサ材料(170)を使用して線に対してピッチ縮小を実施すると、スペーサ軸に沿って延びるピッチ縮小マスキング線(175)を生成することができる。したがって、ピッチ縮小空所によって各ピッチ縮小マスキング線(175)を分離することができる。次に、マスキング・フィーチャの一部分と交差するフォトレジストの第2のパターン(たとえば第2のマスク480のパターン)を付けることができる。第2のパターンは、ピッチ縮小マスキング線(175)、および隣接するピッチ縮小空所をフォトレジストで覆われないままにする窓(482)を有することができる。窓(482)は、ピッチ縮小マスキング線の長軸に対して平行ではない長軸を有することができる。次に、一部にはピッチ縮小空所によって画定された第3のパターンを介して絶縁層(334)をエッチングすると、絶縁層(334)中にコンタクトビア(584)を生成することができる。コンタクトビア(584)を導電材料で充填して電気コンタクト(732)を生成することができる。 (もっと読む)

半導体装置およびその作製方法

【課題】薄膜トランジスタにおいて、ソース/ドレイン領域へのコンタクトの方法を改良することにより、配線抵抗を減らす。

【解決手段】ガラス基板上に第1の絶縁膜、島状の結晶性珪素膜、ゲイト絶縁層、ゲイト電極、第1の配線、ゲイト電極及び第2の絶縁膜を形成し、第2の絶縁膜及びゲイト絶縁層をエッチングしてゲイト電極及び第1の配線の側面に側壁を形成するとともに、島状の結晶性珪素膜のソース領域及びドレイン領域を露出し、ゲイト電極、第1の配線、側壁、島状の結晶性珪素膜及び第1の絶縁膜上に金属層を形成し、ソース領域及びドレイン領域と、金属層とを反応させて島状の結晶性珪素膜の側面から上面にわたって密着したシリサイド層を形成し、金属層をエッチングして、ソース領域又はドレイン領域の一方のシリサイド層と第1の配線とを接合する第2の配線を形成する。

(もっと読む)

キャパシタおよびその製造方法

【課題】

ギガビット級DRAM用キャパシタの誘電体に用いる酸化タンタルの高誘電率化のために結晶化すると、結晶粒界が膜厚方向に貫通してリーク電流のパスが生成され電荷保持特性が劣化する。リーク電流の増大を回避し、酸化タンタルを含む誘電体のEOTが2nm以下となる、MIM構造でスタックトレンチ型のキャパシタおよびその製造方法を提供する。

【解決手段】

酸化タンタルを原子層蒸着法で形成し、ポスト酸化アニールを不要とし、金属下部電極の酸化剥離を防止する。酸化タンタルの結晶化が容易な4〜4.8nmの膜厚で形成し非酸化性雰囲気で結晶化する。その上に厚さ0.5〜1.5nmの結晶分断層を形成し、さらに酸化タンタルおよび結晶分断層を積層して多層化する。これにより、酸化タンタル積層時のエピタキシャル成長を抑止して結晶粒界の膜方向貫通を防止する。

(もっと読む)

表示装置、及び表示装置の作製方法

【課題】信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】一導電型の不純物領域を含む半導体層と、半導体層上にゲート絶縁層と、ゲート電極層と、一導電型の不純物領域と接する配線層と、ゲート絶縁層上に設けられ、配線層と接する導電層と、導電層と接する第1の電極層と、第1の電極層上に電界発光層と、第2の電極層とを有し、配線層は導電層を介して第1の電極層と電気的に接続している。

(もっと読む)

半導体装置の製造方法

【課題】良好な抵抗値を示すコンタクトプラグを備えた半導体装置の製造方法を提供する

こと。

【解決手段】

コンタクトプラグを備えた半導体装置の製造方法であって、半導体シリコン基板表面に設けられた高濃度N導電型拡散層の表面部分および層間絶縁層により形成されたコンタクトホールを通じて、加速エネルギーを30〜120keVの範囲とし、注入量を1.0×1013〜5.0×1014/cm2の範囲としてインジウムイオンを注入するこにより、前記コンタクトホール下部の前記高濃度N導電型拡散層の表面部分にインジウム含有層を形成することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体ダイオードを含む低温で製作された高密度不揮発性メモリアレイ

高密度のモノリシックな三次元メモリアレイにおける使用に適したメモリセルを説明する。メモリセルの好ましい実施形態において、比較的低い温度で結晶化させることができるゲルマニウムまたはゲルマニウム合金で形成された半導体接合ダイオードが、導体間に配置されて形成される。低温度材料の使用により、導体を銅またはアルミニウムで形成することが可能になり、銅およびアルミニウムは両方とも、非常に小さいフィーチャサイズで十分な電流を提供する、非常に密なスタックアレイを見越した、低抵抗率材料である。  (もっと読む)

(もっと読む)

成膜方法、前処理方法および成膜システム

【課題】 混載デバイスに対しても、前処理によって接合部位の自然酸化膜を確実に除去し、抵抗上昇を生じさせない成膜方法を提供する。

【解決手段】 被処理体に露出したSi含有部表面に金属含有膜を成膜する成膜方法は、Si含有部分の表面を、高周波を用いたプラズマにより物理的に処理する物理的表面処理工程と、プラズマによる処理が施されたSi含有部分の表面を反応性ガスにより化学的に処理する化学的表面処理工程と、化学的表面処理が施されたSi含有部分上に金属含有膜を成膜する成膜工程と、を具備する。

(もっと読む)

カーボンナノチューブ配線の形成方法

【課題】 半導体デバイス用配線として適用することができるカーボンナノチューブ配線を形成する。

【解決手段】 触媒金属成分(Ni)とCl2ガスとの前駆体(NiCl)を基板3に吸着させ、その後、Niを析出させることによりNi膜を形成する成膜反応と、成膜反応により形成されたNi膜をCl2ガスラジカルでエッチングするエッチング反応を共存させると共に、成膜反応の速度がエッチング反応の速度よりも大きくなるように制御することにより基板3の凹部の底面だけにNiを成膜し、凹部の底面だけに成膜されたNiを触媒金属として基板3の凹部にカーボンナノチューブを成長させて所定の配線を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 スルーホール等の凹部において、ボイドフリーな膜を形成することを目的とする。

【解決手段】 半導体基板上に形成された、スルーホールを有する絶縁層と、スルーホール内に形成された導電層において、導電層内部に埋め込まれた埋め込み絶縁膜を形成し、ボイドフリーの膜とする。

(もっと読む)

半導体装置

【課題】電極構造下方のプラグの酸化を抑制する半導体装置を提供する。

【解決手段】半導体基板(S)と、この半導体基板に形成されたトランジスタの活性領域(107)に接続した導電性プラグ(118)と、この導電性プラグの底面部及び側面部に被覆する金属シリサイド膜(117)と、前記導電性プラグ上に形成された電極構造(200)と、を備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】 プラグと配線との接続抵抗および絶縁膜の誘電率を効果的に低下させる。

【解決手段】 半導体装置100は、半導体基板(不図示)と、半導体基板の上部に設けられ、銅含有金属により構成される第一配線108と、第一配線108の上部に設けられ、第一配線108に接続する導電性の第一プラグ114と、第一配線108の上部において、第一プラグ114が設けられた領域以外の領域に設けられたCuシリサイド層111と、第一プラグ114の上部に設けられたCuシリサイド層117と、第一配線108の側面から第一プラグ114の側面にわたって形成されるとともに、第一配線108の側面と、第一配線108の上部と、第一プラグ114の側面とを被覆する第一ポーラスMSQ膜105と、を含む配線構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の配線構造中の絶縁膜を低誘電率化するとともに、製造安定性を向上させる。

【解決手段】 半導体装置100は、銅含有金属により構成される第1配線108と、第1配線108の上部を被覆する第1のCuシリサイド層111と、Cuシリサイド層111の上部に設けられ、第1配線108に接続される導電性の第1プラグ114と、第1プラグ114の上部を被覆するCuシリサイド層117と、第1配線108の側壁から第1プラグ114の側壁にわたって設けられ、第1配線108の側壁と、第1配線108の上部と、第1プラグ114の側壁とを覆うように形成された第1ポーラスMSQ膜105と、第1ポーラスMSQ膜105の下層にあって、第1配線108の側壁下部に接するとともに、第1ポーラスMSQ膜105よりも膜密度の高い第1SiCN膜103と、を有する配線構造を備える。

(もっと読む)

半導体装置

【課題】 ゲート電極に多結晶Si/金属積層構造を用いつつ、多結晶Si/金属界面の空乏化を抑制することを目的とする。

【解決手段】

ゲート電極が上層に多結晶Si層6、下層に金属層(TiN層7)の積層構造を成して、かつ上部配線とのコンタクト部分は、上部配線がゲート積層構造の下層金属層まで到達させることで、多結晶Siと下層金属(TiN)に電位差が生じないため、空乏層が伸びることなく、ゲートに印加した電圧と同じだけゲート絶縁膜に電圧が掛かり十分なキャリアがチャネル領域に形成され、駆動電流の向上が得られる。また、ゲート加工が基本的には既存技術をそのまま適用できるため、金属ゲート電極を有する半導体装置の製造及びその技術開発が簡略化される。

(もっと読む)

MEMS素子およびMEMS素子の製造方法

【課題】 耐湿性が良好で信頼性の向上したMEMS素子およびMEMS素子の製造方法を提供する。

【解決手段】 半導体基板10に構造体18が形成され、構造体18の周辺部に構造体18を囲むように配線21と層間絶縁膜20,22とが積層された配線部40を備えるMEMS素子1であって、配線部40を構成する各膜の間に、平面視において構造体18を囲む形状のガードリング31,33,35が形成され、かつ、各膜を貫通し上下に位置するガードリング31,33,35に全周を接する貫通ガードリング30,32,34が形成され、配線部40に配置される配線21は各ガードリング31,33,35および各貫通ガードリング30,32,34の外側に配置される。

(もっと読む)

121 - 140 / 152

[ Back to top ]