Fターム[5F033JJ36]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 化合物 (4,106) | 炭化物 (89)

Fターム[5F033JJ36]に分類される特許

61 - 80 / 89

半導体装置の製造方法

【課題】RC遅延が抑制された半導体装置の製造方法を提供する。

【解決手段】まず、基板上に設けられた層間絶縁膜7に、配線溝8aと接続孔8bとからなるデュアルダマシン開口部8を形成する工程を行う。次に、デュアルダマシン開口部8の内壁を覆う状態で、層間絶縁膜7上にMnからなる金属膜21を形成する工程を行う。次いで、熱処理を行い、金属膜21中の金属を層間絶縁膜7の構成成分と反応させて、金属膜21と層間絶縁膜7との界面に、Mn化合物からなる自己形成バリア膜11を形成する工程を行う。続いて、金属膜21の未反応部分を選択的に除去する工程を行う。その後、デュアルダマシン開口部8に、Cuを含む導電層を埋め込んで、配線溝8aと接続孔8bとに上層配線12とヴィア13とをそれぞれ形成する工程を行うことを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 密着性を高める機能を併せ持つバリア層が形成されるまでの期間に、配線部材の十分な密着性を確保し、配線部材の剥離を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板上に、凹部が設けられた層間絶縁膜を形成する。(b)凹部の内面及び層間絶縁膜の上面に密着層を形成する。(c)密着層の表面を、第1の金属元素を含むCu合金からなる補助膜で被覆する。(d)凹部内に、第1の金属元素以外の第2の金属元素を含む導電部材を充填すると共に、補助膜の上に導電部材を堆積させる。(e)熱処理を行うことにより、補助膜内の第1の金属元素の原子を、凹部の内面に偏析させる。この密着層は、層間絶縁膜の表面上に補助膜を直接堆積させた場合に比べて、補助膜の密着性を高める元素を含む。

(もっと読む)

半導体装置の製造方法

【課題】カーボンナノチューブを形成するための触媒粒子を含有する薄膜層を容易かつ確実に溝構造底部に形成することができる半導体装置の製造方法を提供する。

【解決手段】シートフィルムFに感光性樹脂薄膜層1を塗布形成し、さらにその上層にカーボンナノチューブ形成のための触媒となる金属または金属化合物の粒子を含有するゲル状またはペースト状の触媒薄膜層2を塗布形成する。一方、半導体ウェハWのパターン形成面には下層配線層3および層間絶縁層4が形成されており、層間絶縁層4にはパターン化された溝部5が形成されている。これらのシートフィルムFと半導体ウェハWと押し付けて密着させることにより、感光性樹脂薄膜層1および触媒薄膜層2を半導体ウェハWに転写し、溝部5に感光性樹脂薄膜層1および触媒薄膜層2を充填する。その後、感光性樹脂薄膜層1と層間絶縁層4上面の触媒薄膜層2とを除去する。

(もっと読む)

半導体装置

【課題】銅配線を覆って設けられるバリアメタル膜のバリア性能が向上されており、低比誘電率層間絶縁膜から放出されるガスによりバリアメタル膜が酸化されても、銅配線の信頼性や性能、および品質等が低下するおそれの殆ど無い半導体装置を提供する。

【解決手段】比誘電率が3以下である絶縁膜3が基板1上に少なくとも1層設けられている。少なくとも一部がこの絶縁膜3内に形成されている凹部10の内面を覆って第1のバリアメタル膜6が設けられている。この第1のバリアメタル膜6の表面を覆って凹部10内に第2のバリアメタル膜7が設けられている。この第2のバリアメタル膜7の表面を覆って凹部10内に第3のバリアメタル膜8が設けられている。この第3のバリアメタル膜8の表面を覆って凹部10内にCu膜11が埋め込まれて設けられている。

(もっと読む)

半導体装置

【課題】 埋込銅配線を有する半導体装置の信頼性を向上させる。

【解決手段】 絶縁膜14,15に配線溝を形成し、その配線溝の底面および側面上を含む絶縁膜15上に導電性バリア膜18と銅の主導体膜19を形成し、CMP法により不要な部分を除去して配線20を形成する。そして、主導体膜19上にタングステンからなる金属キャップ膜22を選択成長させてから、配線20を埋込んだ絶縁膜15上に絶縁膜23〜26を形成し、ビア30が金属キャップ膜22を貫通して主導体膜19を露出するようにビア30及び配線溝31を形成し、ビア30の底部で露出した主導体膜19上にタングステンからなる金属キャップ膜32を選択成長させた後に、ビア30および配線溝31の内部を含む絶縁膜26上に導電性バリア膜33と銅の主導体膜34を形成し、CMP法により不要な部分を除去して配線35を形成する。

(もっと読む)

ナノ・スケール・チャネルトランジスタのためのブロックコンタクトアーキテクチャ

ナノスケールチャネルデバイスのコンタクトアーキテクチャは、複数の並列半導体本体を有するデバイスのソースまたはドレイン領域に結合されかつその間に延びるコンタクト構造を有する。コンタクト構造は、サブリソグラフィックピッチを有する並列半導体本体と接触することができる。 (もっと読む)

半導体装置及びその製造方法

基体平面に対して突出した半導体凸部と、この半導体凸部を跨ぐようにその上部から相対する両側面上に延在するゲート電極と、このゲート電極と前記半導体凸部の間に介在するゲート絶縁膜と、前記半導体凸部に設けられたソース/ドレイン領域とを有するMIS型電界効果トランジスタ、このトランジスタを含む基体上に設けられた層間絶縁膜、及びこの層間絶縁膜に形成された埋め込み導体配線を有し、この埋め込み導体配線は、前記半導体凸部のソース/ドレイン領域と、前記層間絶縁膜下の他の導電部とに接続されていることを特徴とする半導体装置。  (もっと読む)

(もっと読む)

電気的接続構造、その製造方法および半導体集積回路装置

【課題】 低抵抗の電気的接続構造を提供する。

【解決手段】 導電体に炭素細長構造体が電気的に接続された電気的接続構造において、導電体上に、導電性触媒担持体層と炭素細長構造体を生成するための触媒微粒子層と炭素細長構造体とを順次積層して、電気的接続構造を得る。

(もっと読む)

小さく、スペースの狭い構成物の配列を形成する方法

集積回路に用いるための、小さく高密度に間隔をあけた孔もしくは支柱の配列を形成するための方法を開示する。高密度に充填された構成物を形成するために、様々なパターン転写ステップ、および、エッチングステップを、ピッチ減少化技術と組み合わせて用いることができる。一つの層に統合することができる、交差し引き伸ばされた構成物のピッチが減少しているパターンの重ね合わせたものを形成するために、従来のフォトリソグラフィーステップをピッチ減少化技術と組み合わせて用いることができる。 (もっと読む)

積層構造を備えた集積回路構造およびその製造方法

【課題】銅または銅合金からなる導電性のダマシン構造を含んだ集積回路構造のバリア層の形成方法を提供する。

【解決手段】導電構造(16、22)の側壁には、金属層、中間層が交互に積層され、少なくとも3つの層を含んだ積層構造(32)が設けられている。積層構造(32)の中に非常に薄い層があるにもかかわらず、外部電流を用いて銅を電解析出するために必要な導電率の高さに起因した銅の拡散に対する、高い障壁作用が得られる。

(もっと読む)

デュアル・ダマシン・パターニング・アプローチ

【課題】半導体素子のビアファーストを用いたデュアル・ダマシン構造のパターニングの方法において、レジスト汚染と低k誘電体絶縁材料の損傷を避けるか、少なくとも最小にする方法を提供する。

【解決手段】低k誘電体絶縁層5にエッチングによりホールを形成し、ホールにギャップ充填材料を堆積し部分的に除去する。この上に金属ハードマスク8と結像材料9を堆積し、トレンチパターンを金属ハードマスクに形成する。結像材料とギャップ充填材料を除去し、金属ハードマスクを用いて無酸素プラズマにより低k誘電体絶縁層をエッチングすることによりトレンチを形成する。トレンチとホールにバリア層と銅を堆積し平坦化する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】より高性能、高信頼性の記憶装置、及びその記憶装置を備えた半導体装置を低コストで、歩留まりよく作製できる技術を提供することも目的とする。

【解決手段】第1の導電層と、第1の導電層の側端部と接して設けられる第1の絶縁層と、第1の導電層及び第1の絶縁層上に設けられる第2の絶縁層と、第2の絶縁層上に設けられる第2の導電層とを有し、第2の絶縁層は、絶縁性材料によって形成されており、絶縁性材料が流動化したときの流動化物に対するぬれ性は、第1の導電層より第1の絶縁層の方が高い。

(もっと読む)

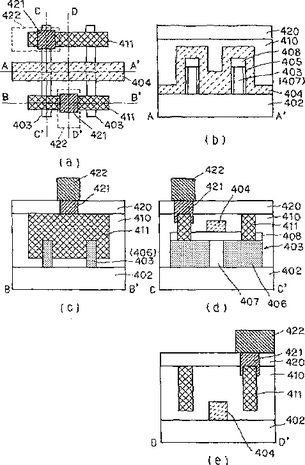

半導体装置及びその製造方法

【課題】アスペクト比の高いコンタクトホールに対して、カバレッジ等の埋め込み特性を向上させ、信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板101の上に形成された絶縁膜102に、下層配線溝103を形成する。次に、下層配線溝103内に第1のバリアメタル膜104及び第1の金属膜105からなる下層配線106を形成する。次に、絶縁膜102の上に、拡散防止絶縁膜107及び層間絶縁膜108を順次堆積する。その後、層間絶縁膜108及び拡散防止絶縁膜107を除去し、下層配線103に到達するコンタクトホール109を形成する。次に、コンタクトホール109の下部領域に第2の金属膜110を選択的に形成する。次に、コンタクトホール109内の第2の金属膜110上に第2のバリアメタル膜111及び第3の金属膜112からなるコンタクトプラグ113を形成する。

(もっと読む)

表面被覆方法、及び該方法を使用するマイクロエレクトロニクス相互接続の作製、並びに集積回路

本発明は、基板の表面を、金属材料から作られる核生成フィルムで被覆する方法に関し、前記表面は、導電性又は半導電性表面であり、凹部及び/又は凸部を含む。 本発明方法は、有機フィルムを表面上に蒸着する工程であって、前記フィルムの厚さが、その自由面が、導電性又は半導電性表面(その上に、フィルムが蒸着されている)の凹部及び/又は凸部に共形的にならうものから成る工程;金属材料の前駆体を、表面上に蒸着した有機フィルムに挿入する工程であって、前記表面上に有機フィルムを蒸着させることから成る工程と同時の又はその後に続く工程;及び金属材料の前駆体を金属材料に変換する工程にある。 本発明方法は、集積回路、超小型電子相互接続及びマイクロシステムの製造のために使用することができる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 多孔質絶縁膜中の成膜ガス等の侵入による配線容量の増加を抑制し、多孔質絶縁膜とバリアメタルとの密着性を向上させた半導体装置及び半導体装置の製造方法を提供する

【解決手段】 配線溝4a,4bを有し、比誘電率が3以下の多孔質絶縁膜2と、配線溝4a,4b表面の膜密度の異なる複数の膜を有するバリアメタル層5a,5bと、バリアメタル層5a,5bと多孔質絶縁膜2との間に形成された金属浸透領域6a,6bと、バリアメタル層5a,5bを介して配線溝4a,4bの中に埋め込まれた金属配線7a,7bとを備える。

(もっと読む)

半導体装置の製造方法

【目的】 p−lowk膜上にバリアメタルを連続に形成することを目的とする。

【構成】 本発明の半導体装置の製造方法は、基体上に、表面にメチル(CH3)基が結合している絶縁膜を形成する絶縁膜形成工程(S102〜S108)と、前記絶縁膜表面に、イミド系の高融点金属化合物を原料として、バリアメタル膜を形成するバリアメタル膜形成工程(114)と、を備えたことを特徴とする。そして、前記バリアメタル膜形成工程において、原子層気相成長法によりバリアメタル膜を形成する。

(もっと読む)

成膜方法、半導体装置の製造方法、半導体装置、プログラムおよび記録媒体

【課題】 半導体装置のCu拡散防止膜とCu配線との密着力を良好とし、半導体装置の信頼性を良好とする。

【解決手段】 被処理基板上にCu膜を成膜する成膜方法であって、前記被処理基板上に形成されたCu拡散防止膜上に密着膜を形成する第1の工程と、前記密着膜上にCu膜を成膜する第2の工程と、を有し、前記密着膜はPdを含むことを特徴とする成膜方法。

(もっと読む)

基板にダマシン構造を製造する方法、集積回路の製造方法およびこれらの方法によって製造される半導体装置

ダマシン構造の製造は、ダマシン構造用の凹部(30)の周りの領域を保護するため、犠牲層(20)を基板(10)上に形成する工程と、前記凹部内に、前記犠牲層と電気接触状態でバリヤ層(40)を形成する工程と、前記凹部内にダマシン構造(50)を形成する工程と、平坦化する工程とを含む。平坦化の間、犠牲層は、バリヤ層またはダマシン構造と電気化学的に反応する。これは、ダマシン構造のくぼみまたは突起を減少させ、銅の残渣を減少させ、そして、バリヤ腐食を減少させるように、ダマシン構造および犠牲層の除去の相対速度を変えることができる。バリヤ層は、ALCVDによって形成することができる。バリヤ層の材料は、WCNおよびTaNの1以上である。犠牲層は、TaN、TiNまたはWとすることができる。  (もっと読む)

(もっと読む)

配線接続構造およびその形成方法

【課題】 配線上に良好なカーボンナノチューブを形成する。

【解決手段】 下層Cu配線1上にMoを堆積して接続層2を形成し、この接続層2上にCVD法を用いてカーボンナノチューブ6を成長させる。Moからなる接続層2を形成することにより、カーボンナノチューブ6を成長させるCVDの際に熱が加えられても、下層Cu配線1からのCuの熱拡散が抑制され、触媒金属5の活性低下が抑えられる。さらに、Moはカーボンナノチューブ6との間の接触抵抗が低いため、下層Cu配線1との低抵抗接続を確保しつつ、良好なカーボンナノチューブ6を形成することができる。

(もっと読む)

カーボンナノチューブ構造体、半導体装置、および半導体パッケージ

【課題】 カーボンナノチューブ束の密度を向上し、電気抵抗や熱抵抗の低減を図るカーボンナノチューブ構造体、半導体装置、および半導体パッケージを提供する。

【解決手段】 第1配線層21、層間絶縁膜22、第2配線層23が順次積層され、層間絶縁膜22を貫通するビアホール24に、第1配線層21と第2配線層23を電気的に接続するカーボンナノチューブ束25が形成されてなるビア26から構成する。カーボンナノチューブ束25は、第1配線層21の凹部28の側面および底面に形成された触媒層29から成長させ、側面から成長したカーボンナノチューブ25aによりカーボンナノチューブ束25の密度を向上する。

(もっと読む)

61 - 80 / 89

[ Back to top ]