Fターム[5F033KK08]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Al (2,131)

Fターム[5F033KK08]の下位に属するFターム

Al合金 (660)

Fターム[5F033KK08]に分類される特許

81 - 100 / 1,471

半導体装置の製造方法及び半導体装置

【課題】電極パッドの表面の突出部に起因する不具合が発生し難い半導体装置の製造方法及び半導体装置を提供する。

【解決手段】半導体装置の製造方法は、表面の突出部に突出部、例えば、プロービング痕21が存在する電極パッド2を備える基板1上に、電極パッド2の少なくとも一部を覆う第1の絶縁膜4を形成する第1の絶縁膜形成工程と、第1の絶縁膜4の表面から突起した部分22を除去することができる処理を行う除去処理工程と、除去処理工程後に、第1の絶縁膜4上及び電極パッド2上に第2の絶縁膜5を形成する第2の絶縁膜形成工程とを有する。

(もっと読む)

半導体装置、半導体装置の製造方法、回路基板および電子機器

【課題】電極パッドと貫通電極との接続面積を確保しつつ、下地膜が確実に形成される半導体装置、半導体装置の製造方法、回路基板および電子機器を提供する。

【解決手段】半導体基板10の能動面10a側に設けられた第一絶縁膜22と、第一絶縁膜22上に設けられた電極パッド12と、電極パッド12の形成位置に対応し、半導体基板10および第一絶縁膜22に形成された貫通孔H3と、貫通孔H3の少なくとも側面に設けられた第二絶縁膜23と、第二絶縁膜23と電極パッド12とを覆うように設けられた下地膜24と、下地膜24の内側で、貫通孔H3に埋め込まれた導電材料からなる貫通電極30と、を具備した半導体装置100において、貫通孔H3の側面と電極パッド12の裏面との角部23aに、第二絶縁膜23がフィレット状に形成されている。

(もっと読む)

めっき装置及び半導体装置の製造方法

【課題】ウェハの周縁部で膜を正常に成長させることができるめっき装置を提供する。

【解決手段】めっき槽2内部に取り付けられた第1電極6と、めっき槽2の側壁5cにおいて、環状のフランジ7cを介してめっき槽2の内から外に向けて直径の小さい順に隣接する環状の第1、第2の開口部7a,7bと、第2の開口部7b内でフランジ7cの上に取り付けられるシールパッキン8と、シールパッキン8の上に、第2の開口部7bの内壁から離れて取り付けられる環状の第2の電極9と、第2の電極9に対向する位置に周縁を有するウェハ保持領域11xを有する第2の開口部7bよりも大きなウェハステージ11と、ウェハステージ11のウェハ保持領域11xの周囲の領域に形成され、シールパッキン8に一端が向けられる加圧用ホール11iと、ウェハステージ11を移動してめっき槽2の側壁5cに押し当てて前記第2の開口部7bを閉塞させる駆動部13とを有する。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】配線幅若しくは配線間隔の縮小に伴い、加工限界の制約を受けるために微細な配線形成が困難になりつつある。

【解決手段】絶縁層(第1の絶縁層12及び第2の絶縁層13)に溝15を形成し、導体膜(バリア膜16及び金属膜17)を溝15を埋設しない膜厚で形成し、続いて導体膜をエッチバックすることで溝15の側壁にサイドウォール状の配線18を形成することで、配線幅は導体膜の膜厚で制御できるために加工限界の制約を受けず、配線抵抗は配線高さを高くすることにより所定の配線抵抗を維持することができる。

(もっと読む)

半導体装置

【課題】とりわけ表面マークの下部に配線タングステンパッドがある場合でも、表面マークのコントラスト低下を抑制する。

【解決手段】メモリチップ31は、配線タングステン階層WTL、第1、第2、第3アルミニウム配線階層1AlL,2AlL,3AlLを備える多層配線構造を備える。各配線層の間には、第1、第2、第3層間絶縁膜315,316,317がそれぞれ形成され、第3アルミニウム配線階層3AlLとポリイミド膜PIとの間には、第4層間絶縁膜318が形成されている。第1のダミーパターンDP1は、第1アルミニウム配線階層1AlLに形成され、第2層間絶縁膜316に覆われている。第2のダミーパターンDP2は、第2アルミニウム配線階層2AlLに形成され、第3層間絶縁膜317に覆われている。第2ダミーパターンDP2は、第1ダミーパターンDP1よりも幅が長い。

(もっと読む)

半導体装置および配線レイアウト方法

【課題】配線間のピッチを縮小可能にした半導体装置を提供する。

【解決手段】半導体基板に形成された複数のトランジスタと、第1の方向に延在する第1の配線を備えた第1の配線層と、第1の配線層よりも上層に設けられ、第1の方向と交差する第2の方向に延在し、第1の配線と電気的に接続された第2の配線を備えた第2の配線層と、半導体基板と第1の配線層との間に設けられ、複数のトランジスタに接続する第1の中継配線と、第1の中継配線が形成された第1の中継配線層と第1の配線層との間に設けられ、第1の配線と複数のトランジスタのうちの一つとを接続する第2の中継配線とを有する構成である。

(もっと読む)

半導体装置

【課題】伝送線路を接続するビア層の周囲のグラウンドを強化することができると共に、ビア部の特性インピーダンスを調整することが可能な半導体装置を提供する。

【解決手段】絶縁層14を介して積層された第1の半導体基体11及び第2の半導体基体21と、第1の半導体基体11に形成され、信号線12とグラウンド13とを含む第1の伝送線路と、第2の半導体基体21に形成され、信号線22とグラウンド23とを含む第2の伝送線路と、第1の伝送線路の信号線12及び第2の伝送線路の信号線22に接続された信号線用のビア層と、第1の伝送線路のグラウンド13及び第2の伝送線路のグラウンドに接続された、グラウンド用の第1のビア層と、第2の伝送線路のグラウンド23に接続され、かつ、信号線用のビア層に対向して形成された帯状のビア層を含む、グラウンド用の第2のビア層16を有する半導体装置を構成する。

(もっと読む)

半導体チップ

【課題】金属原子の拡散に起因する素子特性の劣化を抑制する。

【解決手段】半導体チップは、半導体基板10と、半導体基板10を貫通する貫通電極20と、半導体基板10を貫通する金属柱40と、アライメントマーク47と、絶縁性を有する筒状の絶縁膜50とを有する。アライメントマーク40は、半導体基板10の外部に露出した金属柱40の端部によって形成されている。筒状の絶縁膜50は、半導体基板10に形成されており、金属柱40を取り囲んでいる。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体装置及びその作製方法

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

Cu合金膜、及びそれを備えた表示装置または電子装置

【課題】基板及び/又は絶縁膜との高い密着性を有し、且つ、液晶表示装置などの製造過程で施される熱処理後も低い電気抵抗率を有する新規なCu合金膜を提供する。

【解決手段】基板上にて、基板及び/又は絶縁膜と直接接触するCu合金膜であって、前記Cu合金膜は基板側から順に、合金成分としてX(Xは、Ag、Au、C、W、Ca、Mg、Al、Sn、BおよびNiよりなる群から選択される少なくとも一種の元素)を含有するCu−Mn−X合金層(第一層)と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる層(第二層)で構成されたCu合金膜である。

(もっと読む)

半導体装置、回路基板および電子機器

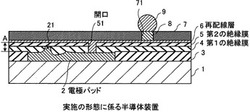

【課題】半導体基板と貫通電極との絶縁を確実とする半導体装置を提供する。

【解決手段】半導体装置10の一方の面14から他方の面16に形成された電極パッド24の裏面に到達する貫通電極13を形成した半導体装置10であって、他方の面16側には第1の絶縁膜20を介して電極パッド24が設けられ、貫通電極13を構成する貫通孔21と第1の絶縁膜20との境界面に、一方の面14側の開口よりも大きい開口を有し、貫通電極13を形成する際、他方の面16側の貫通孔21開口部内周に貫通電極13を構成する導電材料と電極パッド24との間に第2の絶縁膜23を備え、貫通孔21内壁面および第2の絶縁膜上に第3の絶縁膜22が設けられる。

(もっと読む)

発光装置の作製方法

【課題】微細な配線パターンを備えた発光装置の作製方法の提供。

【解決手段】Inと、Gaと、Znとを有する酸化物半導体層を形成し、酸化物半導体層上に第1の導体パターンを形成し、第1の導体パターンより微細な第2の導体パターンを形成し、前記第2の導体パターンと電気的に接続する発光素子を形成する発光装置の作製方法であって、第2の導体パターンは、酸化物半導体層を横断する。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】デバイスの損傷を防ぎ、保護することができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】基板1上に配線層3が形成された第1の積層体10と、第1の積層体10の主面上にその主面を重ねて配設され、基板上11に配線層13が形成された第2の積層体20と、第1の積層体10または第2の積層体20の少なくとも一方の基板上に形成された機能素子とによって構成された半導体装置100に対して、第1の積層体10及び第2の積層体20の主面に垂直な方向から見て、機能素子2,12の周囲に配設され、第1の積層体10と第2の積層体20の界面を貫通する貫通金属部材29を設ける。また、この貫通金属部材29は、第1の積層体10と第2の積層体20を接合した後に、第1の積層体10と第2の積層体20を貫通する貫通孔を設け、貫通孔内に金属を埋め込むことで形成できる。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ダイシング面からチップ領域への水分の浸入を抑制しつつ、スクライブ領域とチップ領域とを配線により接続する。

【解決手段】半導体装置は、チップ領域16と、スクライブ領域15と、2重に配置された第1シールリング18及び第2シールリング17と、チップ領域16からスクライブ領域15まで延伸する配線60と、を有する。半導体装置は、2重に配置された第1シールリング18及び第2シールリング17のうちの一方のシールリングが配線60を通すためにシールしていない層を、他方のシールリングでシールする構造となっている。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】一つの実施形態によれば、半導体装置は、電極、メッキ膜、半田、及びコネクタが設けられる。電極は、半導体チップ表面に設けられた第一の電極部と、第一の電極部上に設けられた絶縁膜の開口部を覆うように設けられ、第一の電極部に接続された突起状の第二の電極部とから構成される。メッキ膜は、第二の電極部上に設けられる。半田は、絶縁膜及びメッキ膜上に設けられる。コネクタは、一端の第一の構成部が半田上に設けられ、他端の第二の構造部が端子に接続され、電極と電極端子の間を接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】積層ハードマスクを部分的に残存させつつ、配線層用のビアプラグのアスペクト比を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の配線層102を形成し、第1の配線層102上に、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を順に形成し、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を含むピラー状の構造体を形成する。第1の配線層102上に、構造体の上面及び側面を覆うように、第3及び第4の絶縁膜109,106を形成し、第4の絶縁膜106を、第2の絶縁膜105が露出するように、部分的に除去する。第1及び第2の絶縁膜内に、半導体素子材料に接続された第1のビアプラグ107を形成し、第3及び第4の絶縁膜内に、第1の配線層102に接続された第2のビアプラグ108を形成し、第1及び第2のビアプラグ上に第2の配線層111を形成する。

(もっと読む)

81 - 100 / 1,471

[ Back to top ]