Fターム[5F033KK08]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | Al (2,131)

Fターム[5F033KK08]の下位に属するFターム

Al合金 (660)

Fターム[5F033KK08]に分類される特許

121 - 140 / 1,471

半導体装置及びその製造方法

【課題】凹形状を有するホールの内壁側面上に側壁保護膜の一部を残留させることにより、ホールの内壁側面を平滑化する。後の工程でホール内に材料を埋設する際にも、ボイドを発生させることなく優れた埋設性でホール内を材料で埋設させる。

【解決手段】半導体基板の裏面上にマスクを設ける工程と、マスクを用いて半導体基板を貫通すると共に凹形状の内壁側面を有するホールであって内壁側面が側壁保護膜で覆われたホールを形成する工程と、側壁保護膜の一部を残留させるようにマスクを除去する工程と、を有する半導体装置の製造方法。

(もっと読む)

固定された導電性ビアおよびその製造方法

【課題】導電性ビアおよびそれを形成する方法に関する。

【解決手段】導電性ビアが、導電性接触構造と該導電性接触構造上に配置された誘電体層の突出部との間に配置された部分を含む。1つの実施形態において、突出部は、導電性接触構造上にアンダーカット層を形成し、次に、該導電性接触構造およびアンダーカット層上に誘電体層を形成することによって形成される。誘電体層に空洞を形成し、誘電体層の突出部を形成するようにアンダーカット層の材料が該空洞を通して除去される。導電性ビアの導電性材料は次に、突出部の下および空洞に形成される。

(もっと読む)

半導体集積回路装置用ルテニウムバリア膜とその作製方法及び該ルテニウムバリア膜を有する半導体集積回路装置とその製造方法

【課題】クレバスの面積比が小さく、低抵抗を維持した薄膜の状態で、配線層を構成する銅又はアルミニウム等の拡散を防止できるルテニウムバリア膜とその作製方法及び該ルテニウム膜を有する半導体集積回路装置とその製造方法を提供する。

【解決する手段】ルテニウムバリア膜は、ルテニウムを主成分とする金属からなり、表面上に観測されるクレバス(溝、割れ目又は深く鋭いくぼみ)の占める面積比が、前記バリア膜表面の全面積に対して15%以下であり、広角X線回折測定によって得られるX線回折プロファイルにおいて、ルテニウムの結晶配向面(002)及び(100)に起因するスペクトルのそれぞれのピーク強度比であるRu(002)/Ru(100)が10以上であり、また、スパッタリング法によって、温度を500℃以上に加熱した状態の半導体基板の配線溝上に成膜されることを特徴とする。

(もっと読む)

半導体集積回路

【課題】製造コストを増大させずに、半導体集積回路の電源配線、接地配線の電圧降下を減少させる。

【解決手段】半導体チップ1上の第1の方向に延びる電源配線12Aが配置され、半導体チップ1上の第2の方向に延びると共に、第2の方向から第1の方向に屈曲し、電源配線12Aの一部と重畳する屈曲部24Aを有する電源引き出し配線22Aが配置されている。また、第1の方向に延びる接地配線12Bが配置され、第2の方向に延びると共に、第2の方向から、第1の方向とは逆方向の第3の方向に屈曲し、接地配線12Bの一部と重畳する屈曲部24Bを有する接地引き出し配線22Bが配置されている。電源引き出し配線22Aと接地引き出し配線22Bを覆う第1の層間絶縁膜13の中には、電源配線12Aと屈曲部24Aを接続する電源配線ビアコンタクト14Aと、接地配線12Bと屈曲部24Bを接続する接地配線ビアコンタクト14Bが配置されている。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備え、前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線及びその他の所定の前記配線層の中間配線は、それぞれ前記ビアを前記積層方向に直交する方向で貫通し、且つ、前記ビア内において相互に交差していることを特徴とする。

(もっと読む)

ヴィア構造およびその作製方法

【課題】より小さな径の基板貫通ヴィアが形成できるようにする。

【解決手段】基板101の回路が形成されている主表面101a側から所望の孔径の範囲で形成可能な深さに形成された第1孔部102と、基板101の裏面側から形成されて第1孔部102に接続する第2孔部103と、第1孔部102の内部に形成された第1孔部配線104と、第1孔部配線104に接続して基板101の主表面101a側に形成された表面配線層105と、第2孔部103の内部に第1孔部配線104に接続して形成された第2孔部配線106と、第2孔部配線106に接続して基板101の裏面側に形成された裏面配線層107とを備える。

(もっと読む)

半導体装置の製造方法

【課題】レジストの膜減りによって残すべき配線がエッチングされることを防止すると共に、露光機による配線パターニング時のフォーカスずれを抑制し、配線の線幅にバラツキが生じることを防止する。

【解決手段】スクライブライン内において、スクライブラインの両側では層間絶縁膜2、4、6が存在せず半導体基板1の表面が露出する領域を設け、スクライブラインの中央位置、つまり溝Tの間に挟まれた領域には層間絶縁膜2、4、6を残す。これにより、スクライブラインとチップとの境界位置近傍において、第3配線層7を形成する際のマスクとして用いるレジスト21が膜減りすることを抑制できる。したがって、レジスト21の膜減りによって残すべき配線がエッチングされることを防止できると共に、露光機による第3配線層7のパターニング時のフォーカスずれを抑制でき、第3配線層7の線幅にバラツキが生じることを防止することが可能となる。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

(もっと読む)

半導体装置

【課題】半導体装置の小型化、特に、狭ピッチ化に対する技術を提供する。

【解決手段】半導体チップ1C上に設けられたパッド2と、プローブ領域10Aおよび接続領域10Bのパッド2上に開口部11を有し、半導体チップ1C上に設けられたパッシベーション膜3と、接続領域10Bのパッド2上に開口部12を有し、パッド2上およびパッシベーション膜3上に設けられたパッシベーション膜5と、パッド2と電気的に接続され、接続領域10B上およびパッシベーション膜5上に設けられた再配線7とを備える。接続領域10Bより半導体チップ1Cの外周部側に設けられたプローブ領域10Aのパッド2にプローブ痕100が存在し、接続領域10Bから半導体チップ1Cの中央部側に延びて再配線7が存在している。

(もっと読む)

半導体装置の配線構造及びその製造方法

【課題】第2メタル層が密着する絶縁層にクラックを生じさせ難い半導体装置の配線構造及びその製造方法を提供する。

【解決手段】半導体装置の配線構造は、絶縁層12と、絶縁層12によって覆われた第1メタル層13と、互いに間隔をあけて絶縁層12上に配列され且つ第1メタル層13より厚く形成された複数の電極部分101,102,…を有する第2メタル層14とを備え、絶縁層12の複数のビアホール内に配置された第1メタル層13と複数の電極部分101,102,…との間を繋ぐ複数の電極部分によって、複数の電極部分を第1メタル層13に電気的に接続する複数の貫通配線15を備えている。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び電子機器

【課題】センサ基板と回路基板とを電極間で張り合わせてなる構成において電極間の接合面積を確保することが可能な3次元構造の固体撮像素子を提供する。

【解決手段】光電変換部21が配列形成されたセンサ基板2と、光電変換部21を駆動する回路が形成されセンサ基板2に対して積層された回路基板7と、センサ基板2における回路基板7側の界面に引き出されたセンサ側電極45と、回路基板7におけるセンサ基板2側の界面に引き出された回路側電極65とを備え、センサ側電極45と回路側電極65とは、凹型電極に凸型電極を嵌め合わせた状態で接合されていることを特徴とする固体撮像素子1である。

(もっと読む)

半導体装置、及び積層型半導体装置

【課題】本発明は、積み重ねられた半導体装置間の電気的接続信頼性を向上可能な半導体装置及び積層型半導体装置を提供することを課題とする。

【解決手段】表面58a及び裏面58bを有する半導体チップ38を貫通する第1の貫通電極48と、半導体チップ38の表面側に位置する第1の貫通電極48の一端に接続される第1の表面電極53と、半導体チップ38の裏面側に位置する第1の貫通電極48の一端に接続される第1の裏面電極55と、半導体チップ38を貫通する第2の貫通電極49と、半導体チップ38の裏面側に位置する第2の貫通電極49の一端に接続される第2の裏面電極56と、を備え、半導体チップ38の表面側に位置する第2の貫通電極49の一端には電極を設けない。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜に空隙が発生することを抑制し、半導体装置の製造における歩留まりの向上を図ることができる。

【解決手段】半導体装置100の製造方法は、一面に互いに隣接する少なくとも2つの凸部90を有する半導体基板10の一面上に、2つの凸部90間における膜厚が2つの凸部90のうち少なくとも一方の高さの1.2倍以上となるように絶縁膜50を形成する工程と、絶縁膜50上に、絶縁膜50よりも硬い絶縁膜60を形成する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

半導体装置およびその製造方法ならびに実装体

【課題】 半導体集積回路チップを実装基板に封止樹脂を用いて接合させた時などに、チップを構成する半導体基板に印加される応力を緩和し、応力による半導体素子特性のバラツキを低減させ、また回路動作中に効率的に放熱できるようにする。

【解決手段】 半導体装置は、半導体基板1の表面上に形成された半導体回路形成層2、

半導体回路形成層2内に形成され、半導体回路を構成するトランジスタ、半導体回路形成層2上に形成され、半導体回路と電気的に接続された電極5とを有する。さらにこの半導体装置において、半導体基板1の裏面側には凹部7が形成され、凹部7を含む裏面上に金属膜6が形成される。一例として半導体装置はその電極5と配線基板本体8のパッド電極9とが熱圧着されると共に封止樹脂10で配線基板に接合される。

(もっと読む)

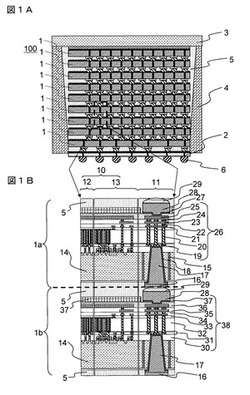

半導体装置及び半導体装置の製造方法

【課題】絶縁層及び金属層の密着性を向上させる。

【解決手段】半導体基板1には、一方の平面1aから他方の平面1bに貫通するビアホール2が形成され、ビアホール2の底部2aとなる電極パッド層4が他方の平面1bに設けられている。この半導体基板1の一方の平面1a及びビアホール2の側壁部2bには、絶縁層6が形成されている。また、金属層7が、半導体基板1の一方の平面1a及びビアホール2の側壁部2bに絶縁層6を介して形成され、ビアホール2の底部2aに直接形成されている。ビアホール2の側壁部2bには、ビアホール2の底部2aにおける開口径がビアホール2の開口端部2cにおける開口径よりも大きくなるように傾斜面2dが形成されている。傾斜面2dには、複数の凹凸2eが形成されている。

(もっと読む)

開口部の形成方法及び半導体装置の作製方法

【課題】少なくともフォトマスクの枚数を増加させることなく、積層構造の下部の導電層が露出するように該導電層上の絶縁膜に対する開口部の形成方法を提供する。

【解決手段】開口部が設けられる部分の積層構造の下部の導電層を、該開口部を形成するフォトマスクと同一のフォトマスクを用いて形成されたエッチングマスクにより予め露出させ、その後保護絶縁膜を形成し、前記積層構造の上部の導電層が開口部において露出されないように、保護絶縁膜に開口部を形成する。このような開口部の形成方法は、半導体装置の作製方法に適用することができる。

(もっと読む)

半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【解決手段】基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層とから形成されていることを特徴としている。このような構成とすることで、フォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる。

(もっと読む)

121 - 140 / 1,471

[ Back to top ]