Fターム[5F033KK18]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続の下層配線層の材料 (17,020) | 金属及びその合金(シリサイドを除く) (9,842) | 高融点金属 (3,578) | Ti (1,040)

Fターム[5F033KK18]に分類される特許

81 - 100 / 1,040

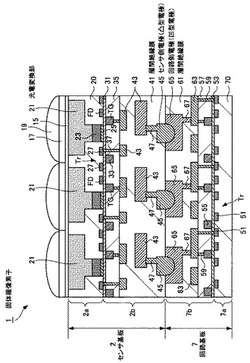

固体撮像素子、固体撮像素子の製造方法、及び電子機器

【課題】センサ基板と回路基板とを電極間で張り合わせてなる構成において電極間の接合面積を確保することが可能な3次元構造の固体撮像素子を提供する。

【解決手段】光電変換部21が配列形成されたセンサ基板2と、光電変換部21を駆動する回路が形成されセンサ基板2に対して積層された回路基板7と、センサ基板2における回路基板7側の界面に引き出されたセンサ側電極45と、回路基板7におけるセンサ基板2側の界面に引き出された回路側電極65とを備え、センサ側電極45と回路側電極65とは、凹型電極に凸型電極を嵌め合わせた状態で接合されていることを特徴とする固体撮像素子1である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【解決手段】半導体装置100は、層間絶縁膜10と、層間絶縁膜10中に設けられた配線20と、層間絶縁膜10上および配線20上に設けられたSiN膜30と、を備え、FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。これにより、配線金属の拡散を防ぐためのバリア絶縁膜である窒化シリコン膜において、リーク電流を抑制することができる

(もっと読む)

半導体装置及びその製造方法

【課題】配線の絶縁膜内へのCu溶出を抑制すると共に、配線間におけるショートの発生を抑止し、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】MCMの半導体装置において、ベアチップ1,2間を接続する配線4aをCu材料13を用いてダマシン法で形成する際に、上面が有機絶縁膜11の表面から上方に突出し、上面の配線幅方向の中央部位が端部位よりも厚い配線4aを形成し、配線4aのCu材料13上のみにメタルキャップ膜5を形成する。

(もっと読む)

能動領域ボンディングの両立性のある高電流構造体

【課題】ボンディング・パッド下方に各回路を有する集積回路。

【解決手段】一実施例において、集積回路は基板と、最上部導電層と、1つ以上の中間導電層と、絶縁材料から成る各層と、各デバイスとを具備する。最上部導電層は少なくとも1個のボンディング・パッド及び比較的硬質の材料から成る副層を有する。1つ以上の中間導電層は最上部導電層及び基板の間に形成する。絶縁材料から成る各層は各導電層を分離する。更に、絶縁材料から成る各層のうちの1つの層は比較的硬質で、最上部導電層及びこの最上部導電層に最も近接した中間導電層の間に位置する。各デバイスは集積回路に形成する。また、最上部導電層に最も近接した少なくとも中間導電層は、ボンディング・パッド下方の各選択デバイスの機能的相互接続部に対して適合する。

(もっと読む)

半導体装置

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

半導体構造およびその製造方法

【課題】カーボンナノチューブによりビアプラグを構成する半導体装置の製造方法において、製造効率を向上させる製造方法を提供する。

【解決手段】絶縁膜中にビアホールを形成し、ビアホールの底に触媒粒子3cを付着させる。ビアホール中において触媒粒子を起点に、カーボンナノチューブを絶縁膜の表面を超えて成長させ、複数のカーボンナノチューブよりなるカーボンナノチューブの束を形成する。絶縁膜上に前記カーボンナノチューブの束を覆って、誘電体膜の塗布液を塗布し、絶縁膜上における塗布液の厚さを、絶縁膜上における塗布膜の表面の高さが絶縁膜表面におけるカーボンナノチューブの高さ以下になるように減少させる。厚さが低減された塗布膜を硬化させて誘電体膜4Dを形成し、誘電体膜を除去して絶縁膜の表面を露出させ、絶縁膜の表面に、カーボンナノチューブによりビアプラグ4VA,4VBを形成する。

(もっと読む)

開口部の形成方法及び半導体装置の作製方法

【課題】少なくともフォトマスクの枚数を増加させることなく、積層構造の下部の導電層が露出するように該導電層上の絶縁膜に対する開口部の形成方法を提供する。

【解決手段】開口部が設けられる部分の積層構造の下部の導電層を、該開口部を形成するフォトマスクと同一のフォトマスクを用いて形成されたエッチングマスクにより予め露出させ、その後保護絶縁膜を形成し、前記積層構造の上部の導電層が開口部において露出されないように、保護絶縁膜に開口部を形成する。このような開口部の形成方法は、半導体装置の作製方法に適用することができる。

(もっと読む)

半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【解決手段】基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層とから形成されていることを特徴としている。このような構成とすることで、フォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる。

(もっと読む)

半導体装置

【課題】3次元的に積層された複数の半導体チップを有する半導体装置の製造歩留まりを向上できる技術を提供する。

【解決手段】半導体基板1の第2面1bからパッド3に達する貫通電極17が形成されている。貫通電極17の内部にある貫通空間は、第1孔7および第1孔7よりも孔径の小さい第2孔11によって構成されている。半導体基板1の第2面1bから半導体基板1を貫通して層間絶縁膜2の途中まで第1孔7が形成されている。そして、第1孔7の底部から層間絶縁膜2を貫通してパッド3に達する第2孔11が形成されている。このとき、半導体基板1の第1面1aに形成されている層間絶縁膜2は、第1孔7の底面と半導体基板1の第1面1aとの段差を反映して段差形状になっている。すなわち、第1孔7の底面とパッド3間に存在する層間絶縁膜2の膜厚がその他の場所の層間絶縁膜2の膜厚よりも薄くなっている。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置

【課題】高周波特性を低下させることなくLDMOSFETを有するチップの面積を縮小する。

【解決手段】LDMOSFETのソース領域と基板1の裏面に形成されたソース裏面電極36とを電気的に接続するp型打ち抜き層4を不純物を高濃度でドープした低抵抗のp型多結晶シリコン膜もしくは低抵抗の金属膜から形成する。そして、LDMOSFETの基本セルのソース同士を電気的に接続するソース配線は配線24Aのみとし、ソース配線を形成する配線層数は、ドレイン配線(配線24B、29B、33)を形成する配線層数より少なくする。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極のための開口部を形成する時に、上部配線層の配線とのミスアラインメント問題が発生しない半導体装置を製造する方法の提供。

【解決手段】第1面及び第1面の反対側に第2面を有する基板を準備する段階と、基板の第1面から基板の厚さ方向に延長して貫通電極が形成される領域に犠牲膜パターンを形成する段階と、基板の第1面上に形成され、犠牲膜パターン上に位置する配線を有する上部配線層を形成する段階と、基板の第2面を部分的に除去して犠牲膜パターンを露出させる段階と、犠牲膜パターンを基板の第2面から除去して配線を露出させる開口部を形成する段階と、開口部内に配線と電気的に接続される貫通電極を形成する段階と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】水素又はカルボン酸を用いたリフロー時の導電部と絶縁層の密着力低下を抑制する。

【解決手段】半導体基板の上に設けられた第1導電部上に絶縁層を形成し(ステップS1)、その絶縁層を被覆するようにバリア層を形成した後(ステップS2)、そのバリア層の上に第2導電部を形成する(ステップS3)。そして、第1導電部上の絶縁層がバリア層で被覆されている状態で、第2導電部を水素又はカルボン酸を含む雰囲気中で溶融し(ステップS4)、その後、その第2導電部をマスクにして、絶縁層の上からバリア層を除去する(ステップS5)。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の検査方法

【課題】層間絶縁膜に生じたボイドを高感度に検出する。

【解決手段】この半導体装置は、多層配線層(非図示、以下略)と、多層配線層中に形成された第一TEGパターン(非図示)を備える。第一TEGパターンは、互いに平行に延伸した複数の第一下層配線402と、層間絶縁膜(非図示)を貫通し、平面視で第一下層配線402間に位置する第一ビア602と、多層配線層の最上層(非図示)に形成され、第一ビア602に接続している第一端子762と、上記した同一の最上層に形成され、第一下層配線402に接続している第二端子764と、を備える。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線の製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13を形成する工程と、第1配線層上の層間絶縁膜内にコンタクト孔15を形成する工程と、コンタクト孔内の第1配線層上にカーボンナノチューブ16を成長させ、コンタクト孔から先端が突き出た複数のカーボンナノチューブを形成する工程と、層間絶縁膜上及び複数のカーボンナノチューブ間に、ストッパ膜17を形成する工程と、ストッパ膜上及び複数のカーボンナノチューブ上に絶縁膜を形成する工程と、ストッパ膜をストッパとして用い、ストッパ膜上の絶縁膜と共に、コンタクト孔上の複数のカーボンナノチューブを除去する工程と、複数のカーボンナノチューブ上に第2配線層14を形成する工程とを備える。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

半導体装置、半導体装置の製造方法およびデータ処理システム

【課題】本発明はコンタクト開口をエッチングにより形成した場合にその下に位置する埋込絶縁膜がエッチングされないようにした構造の提供を目的とする。

【解決手段】本発明は、半導体基板と、半導体基板の主面に形成され活性領域を横断して素子分離領域まで延在するトレンチと、トレンチの下部側に形成された埋込型ゲート電極と、活性領域において埋込型ゲート電極の上方のトレンチ内を充填し、かつ、素子分離領域において埋込型ゲート電極の上方のトレンチ内を完全には充填せずにトレンチの内側面に接して配置されるサイドウォールを構成するキャップ絶縁膜と、素子分離領域においてサイドウォールの内側のトレンチを埋めて埋込型ゲート電極に接続形成されたパッドコンタクトプラグと、パッドコンタクトプラグおよびキャップ絶縁膜上を覆う層間膜と、パッドコンタクトプラグに接続するゲートコンタクトプラグとを具備してなる。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3層構造とすることで課題を解決する。本発明は、アルミニウム原子のチャネル形成領域への拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、その第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、配線又は電極を3層構造としてITOと接合させる。

(もっと読む)

81 - 100 / 1,040

[ Back to top ]