Fターム[5F033MM01]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 埋め込み型配線、ダマシン (3,807)

Fターム[5F033MM01]の下位に属するFターム

デュアルダマシン (1,592)

Fターム[5F033MM01]に分類される特許

101 - 120 / 2,215

半導体装置の製造方法

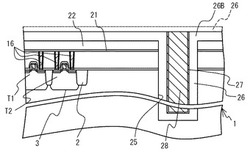

【課題】貫通電極の形成過程で、余分な酸化膜を確実に除去する。

【解決手段】貫通電極を形成するビアホール25の内面に酸化膜26を形成した後、Cu膜28を埋め込む。第1層間絶縁膜22の上に形成された余分なCu膜28をCMP法による研磨で除去するときに、酸化膜26も研磨されて膜厚が薄くなる。膜厚が薄くなった酸化膜26Bをハードマスクとして第1層間絶縁膜14に配線溝を形成する。このとき、酸化膜26Bの膜厚が薄くなる。配線溝に導電材を埋め込んだ後、余分な導電材を研磨によって除去する。このとき、残りの酸化膜26Bが全て研磨により除去される。

(もっと読む)

無電解薄膜析出法により平坦化銅相互接続層を形成する方法および装置

【課題】基板に定形された形態部の内部に、表面が平坦化された導電性材料を形成する方法を提供する。

【解決手段】平坦化表面を形成する方法であって、狭小形態部と幅広形態部が形成された基板上に、第1のプロセスでは電気めっき法により狭小形態部および幅広形態部の少なくとも一部を充填し、第1の層を形成し、第2のプロセスでは無電解めっき法により幅広形態部のに対応する第1の層中の孔および第1の層上に第2の層を充填形成し、表面が平坦な上層部110を形成する。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

誘電フィルム及び材料における疎水性を回復する方法

【課題】誘電率の増加、シラノールの増加、または有機部分の減少、の少なくとも一つによって損傷した、基体上のシリカ誘電フィルムの損傷を回復する。

【解決手段】基体上のそのような損傷シリカ誘電フィルムを表面改質組成物と接触させて、該損傷シリカ誘電フィルムの誘電率の減少、該損傷シリカ誘電フィルムの誘電率のシラノールの減少、該損傷シリカ誘電フィルムの誘電率の有機部分の増加、の1つ以上をもたらす。このとき、該損傷シリカ誘電フィルムに疎水性を与える。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクト或いはビアの位置の特定を容易にする。

【解決手段】半導体装置は、コンタクト又はビア(例えば、孤立コンタクト10a)と、コンタクト又はビアよりも上層に配置されたダミーパターン20と、を有する。ダミーパターン20は、コンタクト又はビアの真上の所定範囲の領域R1には存在せず、且つ、所定範囲の領域R1の周囲の領域においては、所定の規則性に従って平面視において分散して配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ワイヤがCuワイヤであっても、ボンディング時の衝撃による金属のスプラッシュを抑制する。

【解決手段】半導体装置は、電極パッド103を有する半導体チップと、電極パッド103にボンディングされたワイヤ(例えばCuワイヤ105)と、を有している。電極パッド103において、ワイヤがボンディングされている領域の少なくとも表層はルテニウム又は酸化ルテニウムにより構成され、その表層の膜厚は20nm以上である。

(もっと読む)

電子部品、電子部品の製造方法、基板

【課題】チッピング検出用配線が他の部材で覆われている状態であっても、ダイシングによって電子部品を形成した後に、チッピング検出用配線の導通状態を検出するための電圧を印加できる基板を提供する。

【解決手段】電子部品40は、互いに平行を成す一方の主面41aと他方の主面41bが矩形状の基体41を有する。基体41の一方の主面41aには、第一チッピング検出用配線42が配されている。また、基体41の他方の主面41bには、第二チッピング検出用配線44が配されている。第一チッピング検出用配線42は貫通配線43aを介して第二チッピング検出用配線44に電気的に接続される。

(もっと読む)

偏在率算出方法、半導体装置の製造方法及びプログラム

【課題】レイアウトデータからCu残が発生しやすい品種やレイヤであるか否かを判定することのできる偏在率算出方法を提供する。

【解決手段】CPUは、検証レイヤにおいて所定サイズの検証エリア毎にパターン密度を算出するステップS13と、算出されたパターン密度を複数の密度範囲に分別し、各々の密度範囲に属するパターン密度の分布を示す複数の密度マップMAP0〜MAP7を生成するステップS14とを実行する。また、CPUは、各密度マップMAP0〜MAP7に所定量のプラスシフトを加えるステップS15と、パターン密度の密度差が第1基準値以上となる組み合わせの密度マップMAP0〜MAP7を重ね合わせ、両密度マップで重複した領域を抽出するステップS16とを実行する。CPUは、その抽出した領域の総面積を算出するステップS17と、算出した総面積と第2基準値とを比較するステップS18とを実行する。

(もっと読む)

集積回路装置及びその製造方法

【課題】ビアの形成が容易で抵抗が低い集積回路装置及びその製造方法を提供する。

【解決手段】相互に平行に配列された複数本の配線14a、14bと、各配線に接続されたビア16とを備える。配線におけるビアが接続された部分には、配列の方向に延出した凸部31が形成されており、配線における凸部が形成された部分から離隔した部分には、配列の方向に後退した凹部32が形成されている。隣り合う2本の配線において、一方の配線に形成された凸部と他方の配線に形成された凹部とは相互に対向している。各配線において、凹部が形成された部分はその両側の部分から切込33で分断されており、凸部が形成された部分からも分断されている。

(もっと読む)

半導体集積回路装置及びその製造方法

【課題】配線幅若しくは配線間隔の縮小に伴い、加工限界の制約を受けるために微細な配線形成が困難になりつつある。

【解決手段】絶縁層(第1の絶縁層12及び第2の絶縁層13)に溝15を形成し、導体膜(バリア膜16及び金属膜17)を溝15を埋設しない膜厚で形成し、続いて導体膜をエッチバックすることで溝15の側壁にサイドウォール状の配線18を形成することで、配線幅は導体膜の膜厚で制御できるために加工限界の制約を受けず、配線抵抗は配線高さを高くすることにより所定の配線抵抗を維持することができる。

(もっと読む)

半導体装置

【課題】複数のスパイラルを直列に接続してインダクタを形成する場合において、スパイラルを大面積化することなく、スパイラルの巻線を長くする。

【解決手段】インダクタ10は、第1スパイラル100及び第2スパイラル200を有している。第1スパイラル100は、インダクタ10の巻軸と平行な第1の方向から見た場合、中心から外側に向かって巻かれている。第2スパイラル200は、第1の方向から見た場合、外側から中心に向かって、第1スパイラル100と同一の向きに巻かれている。第1スパイラル100及び第2スパイラル200は、外側の端部同士、または中心側の端部同士が、外側接続部材300又は中心側接続部材400を介して接続されている。第2スパイラル200は、第1スパイラル100を、巻軸を回転中心として右回りに90°回転させてから、巻軸に直交する平面に含まれる水平線を基準に鏡映させ、かつ縦横比を変更した形状である。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】 2層構造のビットライン配線において、製造工程を減少することができる半導体記憶装置及びその製造方法を提供する。

【解決手段】 実施形態に係る半導体記憶装置は、半導体基板を持つ。前記半導体基板上に第1及び第2のコンタクトプラグが設けられる。前記第1のコンタクトプラグに接する第1のビットラインが設けられ、前記第2のコンタクトプラグ上には第2のビットラインが設けられる。前記第1のコンタクトプラグは、前記第1のビットラインの上面と接し、かつ前記第2のビットラインと電気的に絶縁しており、前記第2のビットラインの底面の高さは、前記第1のビットラインの上面よりも高い。

(もっと読む)

Cu配線の形成方法および成膜システム

【課題】Cuめっきを用いることなくPVDのみでトレンチまたはホールCuを埋め込んでCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202の全面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上にPVDによりCuがマイグレーションする条件でトレンチ203内に第1のCu膜206を形成する工程と、第1のCu膜206の上に、第1のCu膜206よりも大きな成膜速度でPVDにより第2のCu膜207を形成する工程と、CMPにより全面を研磨する工程とを有する。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置にダミーパタンを配線空隙に効率よく製造容易的に形成する。

【解決手段】多層配線構造の半導体装置において、狭い配線空隙(Area_S1)に、広い配線空隙(Area_S2)に形成されたダミーパタン(22,23)と異なる向きのダミーパタン(21)が形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13内、ビア孔14内および層間絶縁膜12上に、チタン、ジルコニウムおよびマンガンのうちのいずれか、もしくはこれらの合金である金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、トレンチ溝13の底部および側壁とビア孔14の側壁に、タンタル、タングステンのいずれか、もしくはこれらの合金である金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

101 - 120 / 2,215

[ Back to top ]