Fターム[5F033MM30]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 基板内部や裏面に配線が有るもの (1,122)

Fターム[5F033MM30]に分類される特許

21 - 40 / 1,122

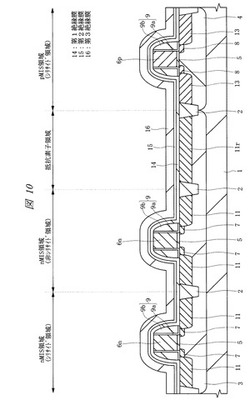

半導体装置の製造方法

【課題】電界効果トランジスタを有する半導体装置のトランジスタ性能を向上させることのできる技術を提供する。

【解決手段】ゲート絶縁膜5およびゲート電極6n,6pの側面にサイドウォール9を形成した後、サイドウォール9の両側の半導体基板1に不純物をイオン注入して不純物領域を形成する。続いて、半導体基板1の主面上に第1絶縁膜14、第2絶縁膜15、および第3絶縁膜16を順次形成した後、イオン注入された上記不純物を活性化する熱処理を行う。ここで、第1絶縁膜14は、第2絶縁膜15よりも被覆性のよい膜であり、かつ、第2絶縁膜15とエッチング選択比が異なる膜である。第2絶縁膜15は、第1絶縁膜14よりも水素の拡散を阻止する機能が高い膜である。第3絶縁膜16は、第1絶縁膜14および第2絶縁膜15よりも内部応力の変化が大きい膜である。

(もっと読む)

エッチング装置及び方法

【課題】基材の幅全体をエッチングして、埋め込まれた表面構造を露出させる方法を提供すること。

【解決手段】基材の表面をその幅の全体にわたりエッチングして材料を実質的に均一に除去すること、当該エッチング処理の間エッチングされる面に光を当てること、当該面から反射又は散乱した光に端部検出技術を適用して、埋め込まれた表面構造の出現を検出すること、そして当該埋め込まれた表面構造の検出に応じエッチングを修正することを含むエッチング方法。基材をその幅の全体にわたりエッチングして、埋め込まれたを露出させるためのエッチング装置も開示される。

(もっと読む)

半導体装置、及びその製造方法

【課題】TSV付き半導体装置において、貫通孔側面すべてにバリア及びシード層を成膜しないことで、空隙の発生を防止する。

【解決手段】

第1の溝部、及び前記第1の溝部より水平断面積が小さい第2の溝部からなる凸状溝部を画成し、且つ、前記第1及び第2の溝部により両端を開口する貫通ビアホールが形成される半導体基板と、前記第1の溝部の内面から、前記第2の溝部の側面の一部まで被覆して、前記貫通ビアホールの側面に隆起するバリア層およびシード層と、前記シード層の表面上、及び、前記シード層で被覆されていない前記第2の溝部内部に形成されて、前記半導体基板の両表面から露出する電極と、を備える半導体装置が提供される。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマーク終端部への応力集中により基板にクラックが発生することを軽減する。

【解決手段】基板の第1の主面に、第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置、電子機器

【課題】空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供する。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

(もっと読む)

半導体装置の製造方法、半導体装置及び電子機器

【課題】半導体装置に含まれる貫通孔を微細化した場合であっても、メッキで貫通孔の内部に貫通電極を形成する。

【解決手段】半導体装置100の製造方法は、基板10の表面10a側にシード層30を形成するシード層形成工程と、シード層形成工程後、シード層30上に配線層40を形成する配線層形成工程と、配線層形成工程後、基板10の裏面10bからシード層30に達する貫通孔10cを形成する貫通孔形成工程と、貫通孔形成工程後、貫通孔10c内にメッキで貫通電極60を形成する貫通電極形成工程と、貫通電極形成工程後、シード層30を複数に分断する分断工程とを含んでいる。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアを用いた実装における端子間のショートや実装精度の低下を防止する。

【解決手段】半導体チップ88の貫通ビア86の上に、他の半導体チップ101を実装する。半導体チップ101のバンプ103は、4つの貫通ビア86で囲まれた領域に導かれて接合される。各貫通ビア86は、バンプ103に面する側面及び上面の保護膜31がエッチングによって除去されており、バンプ103のハンダ材料への濡れ性が保護膜31で覆われた領域よりも良好になっている。このために、ハンダ材料のはみ出しによる他の電極との間のショートが防止される。さらに、1つのバンプ103に複数の貫通ビア86からなる接続端子を配置するので、バンプ103に確実に接合できる。

(もっと読む)

ウェーハ薄膜加工制御方法

【課題】ウェーハ内部のビア底部からウェーハ研削面までの残存寸法に基づいて薄膜化加工を行うウェーハ薄膜加工制御方法を提供する。

【解決手段】ウェーハに予め貫通電極用のビアを形成後、ウェーハの研削面を上にして加工装置のチャックテーブル上にウェーハを保持し、ウェーハの研削面にグラインディングホイールを押し当てて研削加工を行う。この研削加工では、NCIGにより、ウェーハ全体の膜厚を測定して膜厚データを取得すると共に、ビア底部からウェーハ研削面までの寸法を測定して残存寸法データを取得する。仕上げ研削加工時において、ビア底部からウェーハ研削面までの残存寸法データを、ウェーハ全体の膜厚データを参照して導出することで、ビアの底部直前まで研削加工を行うことができる。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホールの側壁に制御性良く傾斜を形成することで、コンタクトプラグにボイドが形成されることを抑制する。

【解決手段】絶縁膜10に第1のコンタクトホール(破線部)を形成する工程と、第1のコンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施して内壁が傾斜した第2のコンタクトホール13を形成する工程と、第2のコンタクトホール内にコンタクトプラグを形成する工程とを有する。

(もっと読む)

基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

(もっと読む)

流動性充填材の充填方法、充填装置及びウエハ

【課題】ウエハに設けられた微細孔内に流動性充填材を、より確実に充填し得、しかも、ウエハ上から充填材残渣を取り払い得る充填方法、そのための充填装置及びウエハを提供すること。

【解決手段】ウエハ7に存在する微細孔73内に流し込まれた流動性充填材9を、加圧手段1,3により加圧する工程において、ウエハ7の受圧面71に対する流動性充填材9の表面張力と、加圧手段1,3の加圧面311に対する流動性充填材9の表面張力とを互いに異ならせる。

(もっと読む)

半導体装置及びその製造方法

【課題】高信頼性のBSV方式のTSVを実現する。

【解決手段】実施形態に係わる半導体装置は、表面及び裏面を有し、表面側にLSIが形成される半導体基板11と、表面側において半導体基板11内に形成され、開口部を有する絶縁層12と、表面側において開口部上に形成され、LSIに接続される導電層13と、裏面側から開口部を介して導電層13に接続されるビア17とを備える。ビア17のサイズは、裏面から半導体基板11と絶縁層12の界面までの範囲内において開口部のサイズよりも大きく、開口部内において開口部のサイズに等しい。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】裏面照射型の固体撮像装置において、受光面と遮光膜との距離を小さくすることにより、光電変換部での受光特性の向上を図る。

【解決手段】光電変換部が配列形成された画素領域を有するセンサ基板と、センサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、画素領域における受光面上に設けられた遮光膜と、遮光膜を覆って設けられた保護絶縁膜と、画素領域の外側の周辺領域において、保護絶縁膜からセンサ基板にかけて埋め込まれ駆動回路に接続された複数の貫通ビアを備えた固体撮像装置。

(もっと読む)

半導体装置の製造方法

【課題】穴部の側壁を基板の表面に対して垂直に形成するとともに、高速にシリコン層をエッチングするプラズマエッチング方法を提供する。

【解決手段】レジスト層をマスクとしてシリコン層をプラズマエッチングする方法であって、前記プラズマエッチング工程が、所定の比率で混合した堆積性ガスおよびエッチング性ガスの混合ガスを処理容器内に導入し、該混合ガス雰囲気で前記被処理基板をプラズマエッチングする第1のエッチングステップと、前記処理容器内に前記堆積性ガスを導入し、前記第1のエッチングステップによりプラズマエッチングされた被処理基板を該堆積性ガスが主体の雰囲気で堆積処理する堆積ステップ、および、前記処理容器内に前記エッチング性ガスを導入し、前記堆積ステップにより堆積処理された被処理基板を該エッチング性ガスが主体の雰囲気でプラズマエッチングする第2のエッチングステップを、複数回繰り返す。

(もっと読む)

半導体基板、電子デバイス及びその製造方法

【課題】シリコン基板、半導体回路素子または絶縁層にクラックが発生することのない高信頼度のTSVを有する半導体基板、電子デバイス及びその製造方法を提供する。

【解決手段】貫通電極を囲む環状の溝に形成された絶縁層3は、シリカ微粒子311と、シリカ微粒子311−311間に生じる隙間に浸透してこれを埋めるナノ結晶またはナノアモルファスのシリカ320とからなるナノコンポジット構造である。

(もっと読む)

半導体装置及びその製造方法

【課題】外部からの不純物等に対する耐性を向上することができる半導体装置及びその製造方法を得る。

【解決手段】GaAs基板1上に下層配線2が設けられている。GaAs基板1及び下層配線2上に樹脂膜4が設けられている。樹脂膜4は、下層配線2上に開口5を有する。下層配線2及び樹脂膜4上にSiN膜6が設けられている。SiN膜6は、開口5内に開口7を有する。下層配線2及び樹脂膜4の一部上に上層配線8が設けられている。上層配線8は、開口5,7を介して下層配線2に接続されたTi膜8aと、Ti膜8a上に設けられたAu膜8bとを有する。上層配線8及び樹脂膜4上にSiN膜9が設けられている。SiN膜9は、樹脂膜4上においてSiN膜6に付着している。SiN膜6,9はTi膜8aの周囲を保護する。

(もっと読む)

半導体装置

【課題】 貫通ビアを用い積層した半導体装置においては、信号を伝送する貫通ビアがオープンやショートした場合に、その貫通ビアを回避して積層チップ全体を正常動作させるために、複雑な回路を構成が必要であった。

【解決手段】 信号を伝送する貫通ビアにおいて、ビアの内壁を構成するシリコンに高い不純物の領域を形成して貫通導体とシリコン基板が接触したときに基板に接続されているVSSなどの基準電位に誘導する。故障モードを固定できるため、冗長化/復号化回路が簡単になるうえ、必要な冗長貫通ビアの本数を削減することができる。

(もっと読む)

半導体装置の製造方法、及び、半導体装置

【課題】 より一層、製品の歩留まりを向上させることのできる半導体装置の製造方法を提供する。

【解決手段】 本開示の半導体装置の製造方法では、まず、第1半導体部及び第2半導体部を貼り合わせた半導体部材の一方の面上に形成された絶縁膜30上に、所定の薬液で処理された際に該所定の薬液が絶縁膜に浸透しないような耐性を有するストッパー膜31を形成する。次いで、半導体部材のストッパー膜31側に、第1半導体部及び第2半導体部を電気的に接続するためのCu配線接合部34を形成する。次いで、Cu配線接合部34上にCu拡散防止膜34を形成する。次いで、Cu配線接合部34の形成領域以外の領域のCu拡散防止膜33を除去して該領域に存在する不要なCu部210,211を露出させる。そして、所定の薬液を用いて、不要なCu部210,211を除去する。

(もっと読む)

21 - 40 / 1,122

[ Back to top ]