Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

761 - 780 / 2,805

半導体装置及びその製造方法

【課題】比誘電率の低い層間絶縁膜を用いた半導体装置において、プラズマ処理時の層間絶縁膜へのダメージを軽減でき、ダメージ層を除去する際に形成されるアンダーカットを抑制する。

【解決手段】基板上に比誘電率の低い材料からなる絶縁膜4を形成する。次に、前記絶縁膜上にチャンバ内でSiOCH膜5を形成し、前記チャンバ内にプラズマを発生させた状態で徐々に膜中のカーボン濃度を減らし、前記SiOCH膜上に連続的にSiO2膜6を形成する。前記SiOCH膜と前記SiO2膜をハードマスクに用いて前記絶縁膜をプラズマ処理し、前記絶縁膜に溝7,8を形成する。その後、前記絶縁膜に形成した溝のエッチング表面をウェットエッチングし、プラズマ処理によるダメージ層と加工残渣物を除去する。

(もっと読む)

半導体装置の製造方法

【課題】工程数の増加を抑えながら、ビア間の耐圧の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】配線2上に低誘電率膜5及び6を形成した後、低誘電率膜5及び6上にハードマスク7、8及び9を形成する。ハードマスク7〜9上にレジストマスクを形成する。レジストマスクを用いて低誘電率膜5及び6にビアホール11を形成する。レジストマスクをアッシングする。このとき、レジストマスクから生じる飛散物をビアホール11の少なくとも側面に付着させて保護膜12を形成する。その後、ビアホール11を配線2まで到達させ、ビアホール11内に導電材を埋め込む。

(もっと読む)

半導体装置及びその製造方法

【課題】 銅配線上に銅ワイヤがワイヤボンディングされて構成される半導体装置において、配線剥がれや銅ワイヤ下の絶縁膜にクラックが入るといった不具合を抑止する。

【解決手段】 本発明の半導体装置は、半導体基板1上に形成された銅配線8と、前記銅配線8の表面及び側面を覆うように形成されたメッキ層10と、前記メッキ層10を介して前記銅配線8上にワイヤボンディングされた銅ワイヤ11とを具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】相異なる膜質領域を有する層間絶縁膜において、膜界面における膜剥れや隣接配線間リークの発生を抑制する。

【解決手段】単層構造の層間絶縁膜である第3の絶縁膜107は複数の空孔120を有している。第3の絶縁膜107における単位体積当たりの空孔占有率は膜厚方向に変化している。

(もっと読む)

半導体装置とその製造方法

【課題】

メタルゲートを有するpチャネルMISトランジスタとメタルゲートを有するnチャネルMISトランジスタとを、少ない工程数で形成する。

【解決手段】

半導体装置は、シリコン層を有する半導体基板と、半導体基板に画定されたn型活性領域とp型活性領域と、n型活性領域の上方に形成され、酸化シリコンより高い誘電率を有し、表面にAlを含有する第1高誘電率ゲート絶縁膜と、p型活性領域の上方に形成され、酸化シリコンより高い誘電率を有する第2高誘電率ゲート絶縁膜と、第1高誘電率ゲート絶縁膜および第2高誘電率ゲート絶縁膜の各々の上に形成され、nチャネルトランジスタに適した仕事関数を有する金属又は金属化合物を含む材料で形成された、第1ゲート電極および第2ゲート電極と、を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】幅の狭い溝状領域への層間絶縁膜の形成にポリシラザンを用いた場合のシリコン酸化膜への改質が良好に行われる半導体装置及びその製造方法を提供する。

【解決手段】上面及び側面をキャップ絶縁膜107及びサイドウォール絶縁膜108で覆われた複数のビット線106間に形成された溝状領域109と、N(窒素)よりもO(酸素)を多く含み溝状領域109の内表面を連続的に覆うSiON膜10と、SiON膜10を介して溝状領域109内に埋め込まれ、ポリシラザンを改質することによって形成されたシリコン酸化膜11とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】コンタクト抵抗を低くし、かつ半導体装置が大型化することを抑制する。

【解決手段】能動素子は、第1電極210(ゲート電極)及び第2電極220(拡散層領域)を有している。ゲート電極210の表面には第1金属化合物層212(シリサイド層)が形成されており、拡散層領域220の表面には第2金属化合物層222(シリサイド層)が形成されている。ゲート電極210には第1コンタクト310が接続しており、拡散層領域220には第2コンタクト320が接続している。第1コンタクト310は、基板200に平行な方向の断面形状が長方形又は楕円であり、かつ下端が第1金属化合物層212に入り込んでいるが、突き抜けていない。第2コンタクト320は、基板200に平行な方向の断面形状が円である。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とコンタクト配線のショート不良を防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板32上にゲートハードマスク、ゲート電極34及びゲート絶縁膜33を形成する。ゲートハードマスクの線幅をゲート電極よりも狭くした後、S/Dエクステンション36を形成する。全面にシリコン酸化膜を堆積形成し、エッチバックしてゲート電極の側壁から上面の一部上に渡って連続的に残存させた絶縁部材37を形成する。ゲートハードマスクを除去した後、ゲート電極と絶縁部材をマスクにしてコンタクトジャンクション38を形成する。金属シリサイド膜を形成後、シリコン窒化膜40と層間絶縁膜41を順次堆積形成する。層間絶縁膜にコンタクトホールを形成し、続いてシリコン酸化膜との選択比が高い異方性エッチングによってシリコン窒化膜を除去することでコンタクトホールを開孔し、コンタクト配線43を形成する。

(もっと読む)

半導体装置の製造方法

【課題】例えばエアギャップ構造の形成に好適な、半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に第1の絶縁膜を形成する工程と、第1の絶縁膜に溝を形成する工程と、第1の絶縁膜上面及び溝の内面を覆うように、Ruを含む第1の金属層を形成する工程と、第1の金属層上に、銅を含む第2の金属層を形成する工程と、第1の絶縁膜上の第2の金属層及び第1の金属層を研磨し除去して、第1の絶縁膜を露出させ、溝内に形成された第1の金属層及び第2の金属層を残す工程と、研磨によって露出した第1の絶縁膜を上面から少なくとも一部除去する工程と、第1の絶縁膜の上方に、第1及び第2の金属層の少なくとも上面を覆う第2の絶縁膜を形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】平坦性に優れ、リーク電流低減効果の高いコバルトシリサイドを提供する。

【解決手段】半導体基板上のトランジスタの拡散層上にコバルトシリサイドを形成する工程を含む半導体装置の製造方法であって、少なくとも拡散層上に基板加熱を行うことなく第1のコバルト膜9をスパッタ成膜した後、200〜350℃で第2のコバルト膜10を積層し、シリサイド化を行う。

(もっと読む)

低k誘電体ライナーを有するシリコン貫通ビア

【課題】 シリコン貫通ビアを有する半導体デバイスを提供する。

【解決手段】 回路面と前記回路面とは逆の背面を有する半導体基板、前記半導体基板を穿通して延伸するシリコン貫通ビア、及び前記シリコン貫通ビアと前記半導体基板の間に設置され、前記半導体基板の前記背面の表面の少なくとも一部の上に延伸する誘電体層を含む半導体デバイス。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】、配線層とその下層のプラグ層との配線抵抗を抑えながら下層のプラグの埋め込み性を向上させることが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Cu配線10と、Cu配線10の下層側でCu配線10と接触して接続されるCuプラグ20と、Cuプラグ20の底面側及び側面側に配置された、Cuに対してバリア性を有するBM膜240と、Cu配線10とCuプラグ20との内Cuプラグ20側に選択的に、かつCuプラグ20とBM膜240との間に介在するように配置された、BM膜240よりも前記導電性材料に対して濡れ性が高いRu膜242と、Cu配線10とCuプラグ20とが接触する箇所を少なくとも除くCu配線10の底面側と、Cu配線10の側面側とに配置された、Cuに対してバリア性を有するBM膜244と、を備えたことを特徴とする。

(もっと読む)

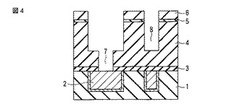

半導体装置の製造方法

【課題】多層配線構造において、下層金属配線への接続用スルーホール内にボイドが発生することを防止する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に金属配線3を形成し、全面に層間絶縁膜4を形成する。絶縁膜内にスルーホールを形成する。スパッタエッチングにより、スルーホール開口部に傾斜部を設け断面を大きくするとともに金属配線の表面の酸化Alを除去する。半導体基板を冷却し、基板温度20℃〜40℃で、スルーホールの内面を含む全面に第1のチタン膜6、窒化チタン膜7、第2のチタン膜8、第1のAl層9aを形成する。続いて基板を加熱して第2のAl層9bをリフローしながら形成した後、第3のAl層9cを形成する。

(もっと読む)

半導体装置とその製造方法

【課題】ダマシン配線構造を有する半導体装置に形成される配線表面の酸化物部を選択的に除去する。

【解決手段】ダマシン配線構造を有する半導体装置を製造するに際し、配線表面を、Xeのプラズマで逆スパッタリングする。本発明によれば、Xeのプラズマガスで逆スパッタリングすることにより、配線表面の酸化物部等を選択的に効率よく除去でき、ダマシン配線構造において、上下配線間のコンタクト抵抗の増大を回避できる。また、配線の上に形成されたCFなどの絶縁膜へのダメージを抑制でき、絶縁膜の誘電率変動も抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】配線材料の拡散を抑えながら、金属配線の微細化を図ることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に層間絶縁膜を形成する工程(a)と、層間絶縁膜に配線を形成する工程(b)と、配線の上面及び層間絶縁膜の上面に有機溶液を塗布する工程(c)と、工程(c)の後に、配線の上面及び層間絶縁膜の上面にシリル化溶液を塗布する工程(d)と、工程(d)の後に、基板を加熱する工程(e)と、少なくとも配線の上面上に第1のライナー絶縁膜を形成する工程(f)とを備えている。

(もっと読む)

半導体集積回路およびその半導体集積回路のフューズ素子

【課題】電気フューズでの切り離しが不十分となるような不具合が生じるのを抑制する。

【解決手段】第1配線(2)と、層間膜(6)を介して第1配線(2)の上に設けられた第2配線(3)と、層間膜(6)を貫通して第1配線(2)と第2配線(3)とを接続し、第2配線(3)から供給される電力に応答して第1配線(2)と第2配線(3)との接続を遮断するフューズ素子(1)とを具備する半導体集積回路を構成する。そして、フューズ素子(1)の本体部分(4)は、第1側面(14)と、第1側面(14)の反対の位置に対応する第2側面(15)とを含むものとする。第1側面(14)を含む面と下側界面との角度は、直角以上の第1角度(θ1)であり、第2側面(15)を含む面と下側界面との角度は、第1角度(θ1)より大きい第2角度(θ2)であることが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通孔(接続孔)内に形成された絶縁膜上に設けられる配線層と半導体基板との間の電気的絶縁性の不良の発生が低減された半導体装置の製造方法を提供する。

【解決手段】半導体基板11の一方の面上に第1の絶縁層12を介して位置する第1の配線層13と、半導体基板の他方の面から第1の配線層に至る接続孔19を形成する。接続孔の側面から他方の面に亘って半導体基板上に位置し、接続孔内で第1の配線層に接する第2の絶縁層14を形成する。接続孔の側面上から他方の面上に亘って第2の絶縁層上に位置し、接続孔内で第1の配線層に接する第2の配線層16を形成する。この形成において、第2の絶縁層を、膜質の異なる2種の絶縁膜14a、14b又はそれ以上の絶縁膜の積層体から構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状構造体の形成の際のリソグラフィの合わせずれの許容度を拡大し、デバイス特性の劣化を抑制する半導体装置及びその製造方法を提供する。

【解決手段】第1層と、前記第1層の主面の上に設けられた第2層と、前記主面を貫通し、前記第1層と前記第2層とに延在する導電性の柱状構造体と、前記主面の前記第2層の側において前記柱状構造体の側壁に付設された側部と、を備えたことを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲルマニウムを高濃度に含む界面を形成することができ、従来に比べてコンタクト抵抗を低下させることのできる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】p型拡散層5が形成されたシリコン基板1上に層間絶縁膜7を形成する。次に、層間絶縁膜7に、シリコン基板1のp型拡散層5が形成された部位に達するコンタクトホール10を形成する。次に、コンタクトホール10の底部にあるシリコン基板1に、ホウ素とゲルマニウムを含むクラスターイオンビーム20を照射して、シリコン基板1中にホウ素とゲルマニウムとを含むシリコン層11を形成する。次に、ホウ素とゲルマニウムを含むクラスターイオンビームを照射20して、ホウ素とゲルマニウムを含む層12をシリコン基板1の表面よりも上に形成する。

(もっと読む)

761 - 780 / 2,805

[ Back to top ]