Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

841 - 860 / 2,805

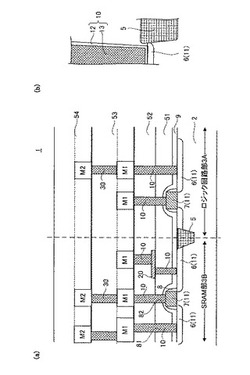

半導体装置

【課題】信頼性が高く、特性の改善された半導体装置を提供すること。

【解決手段】本発明の一態様に係る半導体装置1は、ワンチップに規則性を有するレイアウト領域と、規則性のないレイアウト領域を備える半導体装置であって、下層導電層11と、下層導電層11上に形成された層間絶縁膜と、その上に形成された上層配線層M1と、下層導電層11と上層配線層M1とを、実質的に最短距離で電気的に接続するように配設した接続プラグ10とを備える。そして、規則性を有するレイアウト領域における少なくとも一部の領域において、下層導電層11と上層配線層M1との電気的接続が、下層導電層11の直上から延在する直上位置、当該直上位置から離間したシフト位置に配設した少なくとも2つの接続プラグ10と、これらを電気的に接続するための中間接続層20により行われている。

(もっと読む)

有機表面パッシベーションでめっきの進行に差を付けて遅らせることによるボトムアップめっき

本発明の実施形態は、概して、半導体基板を処理するための装置及び方法に関するものである。一実施形態は基板を処理する方法を提供し、この方法は、基板に形成されたトレンチ構造又はビア構造を有する基板を覆うようにシード層を形成することと、シード層の一部を有機パッシベーション膜で被覆することと、前記トレンチ構造又はビア構造をめっき液に浸漬して、前記有機パッシベーション膜で被覆されないシード層の上に導電材料を堆積させることとを含む。  (もっと読む)

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106は、面積重み付けした平均結晶粒径が13μm以上の金属材料を少なくとも含む。また、導通部106は、結晶粒径が29μm以上の金属材料を含む。

(もっと読む)

トレンチ及びビアの断面形状を変形させる方法及び装置

本発明の実施形態は、概して、半導体基板を処理する装置及び方法に関するものである。具体的には、本発明の実施形態は、トレンチ及びビアの断面形状を、トレンチ及びビアへの充填を行なう前に変形させる方法及び装置に関するものである。本発明の一実施形態では、トレンチ構造をエッチング液に曝すことにより、犠牲層を形成してトレンチ構造の上部開口部を閉塞する。一実施形態では、エッチング液は、第1材料と反応して犠牲層を形成する副生成物を生成することにより、第1材料を除去するように調製される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半田バンプが採用された半導体装置において、隣接する半田バンプ同士の接触の抑制が図られた半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、第1主表面を有する半導体チップ120と、第1主表面に形成された複数の電極123と、電極123ごとに複数形成されたランド部127と、半導体チップ120の第1主表面と対向する第2主表面を有するパッケージ基板160と、第2主表面に形成された複数の電極162と、電極162に形成されたランド部170と、ランド部127およびランド部170とを接続する半田バンプ125とを備える。

(もっと読む)

半導体装置

【課題】対向、近接する拡散層と導体との間の漏れ電流を抑制し、効率を向上が図られた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、半導体基板1を貫通する貫通電極7と、半導体基板1の上部であって、貫通電極7の側方に位置する領域に設けられた拡散層24と、拡散層24の上部に設けられた拡散層22とを備えている。貫通電極7の側面のうち拡散層24に対向する部分は湾曲しており、拡散層24の表面のうち貫通電極7に対向する部分は湾曲している。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】表示デバイスに用いられる薄膜トランジスタ基板の配線構造において、Al合金膜と透明画素電極を直接コンタクトさせることができるとともに、薄膜トランジスタの製造プロセス中に用いられるアミン系剥離液に対する腐食性を改善できるAl合金膜を開発し、それを備えた表示デバイスを提供する。

【解決手段】Geを0.2〜2.0原子%、および元素群X(Ag、In、Sn、Ni、Co、Cu)より選択される少なくとも1種の元素を含むと共に、希土類元素と高融点金属群(Ti、Ta、V、Nb、Mo、W、Cr、Zr、Hf)からなる元素群Qより選択される少なくとも1種の元素を0.02〜1原子%含み、かつ、粒径が100nmを超える析出物が10−6cm2あたり1個以下であるところに特徴を有するAl合金膜と、該Al合金膜を備えた表示装置。

(もっと読む)

積層半導体装置および積層半導体装置の製造方法

【課題】TSVを有するSOI基板を積層する場合に余分な圧力を加えることなく、少ない圧力で確実にバンプ間を接合する。

【解決手段】絶縁層および絶縁層に接して形成されたSOI層を有する基板と、基板の表面および裏面の間を貫通する貫通孔と、表面または裏面と実質的に同一な平面に端面を有する、貫通孔に形成された貫通結合部と、を有する半導体装置を複数備え、一の半導体装置の貫通結合部の端面と、他の半導体装置の貫通結合部の端面とを接合することにより、一の半導体装置と他の半導体装置とを積層して形成した積層半導体装置を提供する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】貫通電極を有する3次元構造の半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間で、第1バンプ電極50が形成されていない領域に、スペーサ49と第2バンプ電極50aとを積層した支持部を形成することによって、ウエハW3のたわみを防いで、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔をウエハ面内で均一に保つ。これにより、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間の接着剤51の未充填箇所の生成を防ぐ。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】上層配線の幅によらずにコンタクトプラグの底面がアンカー構造となり、下層配線との接続抵抗を低減できる半導体装置とその製造方法を提供する。

【解決手段】基板に下層配線W1となる第1導電層を形成し、絶縁膜を形成し、上層配線用溝とこれに連通するようにコンタクトホールCHを形成する。次に、コンタクトホール及び上層配線用溝の内壁面を被覆してバリアメタル層を形成し、その上層にコンタクトホール及び上層配線用溝に埋め込んで第2導電層を形成する。ここで、上層配線用溝及びコンタクトホールを形成する工程において、上層配線W2と下層配線W1の交差する領域に、上層配線にスリットSL1,SL2または切り欠きを設けて幅が狭くなった部分NPが設けられるように上層配線用溝を形成し、この幅が狭くなった部分NPにおいてコンタクトホールCHを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】パッケージサイズの拡大や製造プロセスを変更せずにSOI基板のシリコン基板層の電位固定を行うことができる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体基板層11の表面からSOI基板10をエッチングし、電極パッド16に達する第1のトレンチおよび半導体基板層11内部で終端している第2のトレンチを形成する工程と、半導体基板層の表面および各トレンチを覆うように絶縁膜19を形成する工程と、各トレンチ底面の絶縁膜19を除去して電極パッド16および半導体基板層11を露出させる工程と、半導体基板層11の表面上と各トレンチの側壁および底面に導電膜31〜33を形成して貫通電極30を形成するとともに、コンタクト部50を形成する工程と、半導体基板層11上の導電膜にパターニングを施して外部電極43およびコンタクト部50に電気的に接続された電位固定用の外部電極43aを形成する工程と、を含む。

(もっと読む)

Ti膜の成膜方法および成膜装置、ならびに記憶媒体

【課題】CVDによりTi膜を成膜する際に、より低抵抗でかつ抵抗のばらつきが小さいTi膜を成膜することができ、プラズマダメージを小さくすることができるTi膜の成膜方法を提供すること。

【解決手段】チャンバ内にシリコンウエハを配置し、TiCl4ガスおよびH2ガスを含む処理ガスを導入しつつチャンバ内にプラズマを生成し、そのプラズマにより処理ガスの反応を促進してシリコンウエハ上にTi膜を成膜するにあたり、チャンバ内にシリコンウエハが配置された状態でTiCl4ガスを導入した後、チャンバ内にプラズマを生成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】素子特性を劣化させることなく、貫通電極を有する3次元構造の半導体装置を実現することのできる技術を提供する。

【解決手段】半導体基板1Sの主裏面間を貫通する貫通電極8と、その貫通電極8を分離する貫通分離部10とが同一位置に設けられており、半導体基板1Sに、貫通分離部形成用の絶縁トレンチ部を形成した後、活性領域に半導体素子(MIS・FET(Q))を形成し、さらにその後、貫通電極形成用の導通トレンチ部を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜として低誘電率膜を用いて配線溝を形成する際のダメージ層の形成による配線間容量の増加を抑制する。

【解決手段】低誘電率膜114の側壁に形成されたダメージ層130を除去する工程(図3(a)、3(b))と、化学気相成長法により第2の保護絶縁膜134を形成し、第1の保護絶縁膜116および低誘電率膜114の側壁を第2の保護絶縁膜134で覆って第2の凹部136cを形成する工程(図3(c))と、配線溝136dが低誘電率膜114の表面に選択的に第2の保護絶縁膜134が形成された側壁を有するように、第2の保護絶縁膜134をエッチバックして成形する工程(図3(d))とにより配線溝136dを形成する。

(もっと読む)

窒化チタン障壁層の形成方法及び窒化チタン障壁層を含む半導体デバイス

【課題】追従性が高く良好なステップ・カバレージ及び低い抵抗率を有する窒化チタン障壁層を形成する方法を提供する。

【解決手段】部分的に製作された電子デバイスに窒化チタン障壁層を形成する方法であって、前記部分的に製作された電子デバイスの上に第1の温度で、第1の抵抗率を有する第1の窒化チタンサブレーヤ40を堆積させる工程と、前記第1の窒化チタンサブレーヤの上に第2の温度で、第2の抵抗率を有する第2の窒化チタンサブレーヤ42を堆積させる工程とを備えており、前記第2の温度は前記第1の温度よりも高く、第2の抵抗率は第1の抵抗率よりも低いことを特徴とする窒化チタン障壁層の形成方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられる金属半導体化合物電極の界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板と、半導体基板上に形成され、Sを1×1020atoms/cm3以上含有する界面層と、界面層上に形成され、略全域にSを1×1020atoms/cm3以上含有する金属半導体化合物層と、金属半導体化合物層上の金属電極を有することを特徴とする半導体装置。半導体基板上に金属膜を堆積し、第1の熱処理により、金属膜を半導体基板と反応させて、金属半導体化合物層を形成し、金属半導体化合物層に、飛程が金属半導体化合物層の膜厚未満となる条件でSをイオン注入し、第2の熱処理により、Sを再配置することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来のエアギャップ構造より、さらに容量及び容量ばらつきを低減することができる。

【解決手段】 基板上の絶縁膜17上に、銅を主成分として含む配線26を形成する。それから、リザーバーパターン用絶縁膜21、22及びバリア絶縁膜29を形成し、配線26の上面および側面上と絶縁膜17及び絶縁膜29上に銅の拡散を抑制または防止する機能を有する絶縁膜31を形成する。このとき、狭い配線間スペース底部の絶縁膜17の膜厚保は、配線26上の絶縁膜31の膜厚より、薄く成膜することで細線ピッチの配線容量を効率良く低減する。その後、低誘電率からなる絶縁膜36及び絶縁膜37を成膜する。その際、配線26の隣接配線間において、対向する配線側面の上方での堆積速度が下方での堆積速度より大きくなるように絶縁膜36を形成し、エアギャップを形成する。最後に、層間CMPによって、絶縁膜37を平坦化する。

(もっと読む)

半導体装置およびその製造方法

【課題】ビアホール下方でのスペーサ膜の閉塞を回避するとともに、ビアプラグの上方で隣接する配線層との間の余裕距離を確保することができる半導体装置を提供する。

【解決手段】シリコン基板1上に設けられた上面から下面まで貫通するコンタクトプラグ32を有する第1の層間絶縁膜30と、第1の層間絶縁膜30上に形成され、コンタクトプラグ32の形成位置に対応する位置の上面から下面まで貫通するビアホール41を有する第2の層間絶縁膜40と、ビアホール41内にコンタクトプラグ32と電気的に接触するように導電性材料が埋め込まれたビアプラグ43と、を備え、ビアホール41を形成する側壁は、第2の層間絶縁膜40の上面から下面に向かって、基板面に平行な方向の断面積が徐々に減少する順テーパ状を有し、ビアホールの上端部から所定の深さまでの側壁に、第2の層間絶縁膜40とは異なる絶縁性材料からなるスペーサ膜42が埋め込まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】金属配線部から、金属が層間絶縁膜に拡散することを抑制するためのシリコン窒化膜等から窒素や水素が拡散することによる影響を軽減した信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上に形成された半導体素子部100と、半導体素子部100の上部に形成された銅配線225と、半導体素子部100と銅配線225とを電気的に接続するプラグ電極216と、このプラグ電極216が酸化しないようにするシリコン酸化膜223と、半導体素子部100の上部に形成されたアモルファスシリコン膜217と、アモルファスシリコン膜217の上部に形成されたCu拡散防止膜218と、を有した半導体装置1とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】TDDB寿命を長くすることが可能な半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に、ポアが形成されるキャップ膜を形成する工程(S106)と、前記キャップ膜と前記絶縁膜に開口部を形成する工程(S110)と、前記開口部内に導電性材料を堆積させる工程(S116)と、前記開口部内に前記導電性材料が堆積させられた後に、前記ポアの一部を残しながら一部が前記キャップ膜中に食い込むように、前記キャップ膜上に前記導電性材料の拡散を防止する拡散防止膜を形成する工程(S122)と、を備えたことを特徴とする。

(もっと読む)

841 - 860 / 2,805

[ Back to top ]