Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

861 - 880 / 2,805

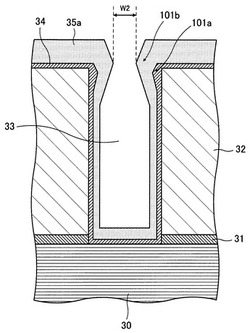

半導体装置の製造方法

【課題】パターン内のボイドの発生を抑制する。

【解決手段】下層配線30に達するビアホール33を形成し、バリアメタル層34及びシード層35aを形成した後、電解めっき法により、ビアホール33内をめっき層で埋め込む。その際、シード層35a形成後に、ビアホール33の間口にオーバーハング101bが形成されることを想定し、例えば開口径70nm以下のビアホール33であれば、シード層35a形成後のビアホール33の開口径W2を20nm以上にする。これにより、そのシード層35aを用いた電解めっき時に、ビアホール33内がめっき層で埋まる前にその間口が塞がってボイドが発生するのを回避する。

(もっと読む)

半導体装置及びその製造方法

【課題】金属配線部から、金属が層間絶縁膜に拡散することを抑制するためのシリコン窒化膜等から窒素や水素が拡散することによる影響を軽減した信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上に形成された半導体素子部100と、半導体素子部100の上部に形成された銅配線225と、半導体素子部100と銅配線225とを電気的に接続するプラグ電極216と、このプラグ電極216が酸化しないようにするシリコン酸化膜223と、半導体素子部100の上部に形成されたアモルファスシリコン膜217と、アモルファスシリコン膜217の上部に形成されたCu拡散防止膜218と、を有した半導体装置1とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】TDDB寿命を長くすることが可能な半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に、ポアが形成されるキャップ膜を形成する工程(S106)と、前記キャップ膜と前記絶縁膜に開口部を形成する工程(S110)と、前記開口部内に導電性材料を堆積させる工程(S116)と、前記開口部内に前記導電性材料が堆積させられた後に、前記ポアの一部を残しながら一部が前記キャップ膜中に食い込むように、前記キャップ膜上に前記導電性材料の拡散を防止する拡散防止膜を形成する工程(S122)と、を備えたことを特徴とする。

(もっと読む)

配線構造及び配線構造の製造方法

【課題】シリコンへのオーミック接合が得られると共に、シリコン中への元素の拡散を抑制できる配線構造及び配線構造の製造方法を提供する。

【解決手段】本発明に係る配線構造1aは、シリコン層10と、シリコン層10上に設けられ、ニッケル(Ni)が添加された銅合金からなる下地層20と、下地層20上に設けられる銅層30とを備え、シリコン層10と下地層20との界面を含む領域でNiが濃化することにより、電気導電性を有する拡散バリア層25が形成される。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電流損失を低減した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の金属材料は、結晶粒径が29μm以上の結晶粒を含む。また、導通部106の金属材料は、面積重み付けした平均結晶粒径が13μm以上である。

(もっと読む)

マイクロ電子構造体、マルチチップモジュール及びそれを含むメモリカードとシステム並びに集積回路素子の製造方法

【課題】ビア電極を効果的に配しうるマイクロ電子構造体、マルチチップモジュール、メモリカード及び集積回路素子の製造方法を提供する。

【解決手段】基板110と、前記基板上に提供され、貫通して延長される第1及び第2開口を含む導電性パッド130と、前記導電性パッド上に提供され、前記導電性パッド内の前記第1開口を貫通して前記基板内に延長される第1導電性ビア電極150と、前記導電性パッド上に前記第1導電性ビア電極に隣接するように提供され、前記導電性パッド内の前記第2開口を貫通して前記基板内に延長される第2導電性ビア電極160とを有する。

(もっと読む)

半導体装置

【課題】製造バラツキに関わらず、切断箇所を制御できる構成の電気ヒューズを得る。

【解決手段】半導体装置200は、基板(不図示)上に形成された上層ヒューズ配線112、下層ヒューズ配線122、および上層ヒューズ配線112の一端と接続され、上層ヒューズ配線112と下層ヒューズ配線122とを接続するビア130から構成される電気ヒューズ100を含む。上層ヒューズ配線112には、一端側で配線幅が狭くなった幅変動領域118が設けられている。

(もっと読む)

半導体装置、パターン形成方法および半導体装置の製造方法

【課題】開口部の間口部分の拡大を抑制しつつ、開口部内に埋め込み導体を埋め込みやすくする。

【解決手段】半導体ウェハW1の中心から左側に離れたチップ領域C1a、C1bでは、開口部13a、13b内の左右の壁面のうち右側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心から右側に離れたチップ領域C1d、C1eでは、開口部13d、13e内の左右の壁面のうち左側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心の近傍のチップ領域C1cでは、開口部13c内の左右の壁面には傾斜面を設けないようにする。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置の製造装置

【課題】本願発明者らによると、VLSI(Very Large Scale Integration)のウエハ・プロセスにおいて、以下のような問題があることが明らかとなった。すなわち、プリ・メタル(Premetal)工程のタングステン・プラグ形成の準備工程としてのバリア・メタル・スパッタリング成膜時や第1層メタル配線層のスパッタリング成膜時に、ウエハからの脱ガスによる水分に起因する異物の発生がみられる。

【解決手段】本願発明は半導体集積回路装置の製造工程におけるプラズマ・プロセスで、プロセス・チャンバ外に設けられたアンテナにより、プラズマから発生する電磁波を受信することで、同チャンバ内の水分をインサイチュー・モニタ(In Situ Monitor)するものである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低誘電率膜を用いた層間絶縁膜SiOCH膜をCMPプロセスにおけるダメージから保護しつつ、配線間層間絶縁膜SiOCH膜の実効誘電率を低減する。

【解決手段】半導体装置100は、SiOCH膜10の表層が改質されることにより形成された、SiOCH膜10よりも炭素濃度が低くかつSiOCH膜10よりも酸素濃度が高い表面改質層20が設けられるとともに、Cu配線50の表面及び表面改質層20の表面に接するキャップ絶縁膜60を有している。このため、SiOCH膜10全体の誘電率の上昇を低減しつつ、CMPプロセスにおいて親水性の表面改質層20が露出することによって水滴が残りにくくなり、CMPプロセス後のパーティクルの残留やウォーターマークの発生を低減できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置及びその製造方法について、ホウ素含有タングステン層を核形成層とする場合に、コンタクト抵抗値の増大を抑制する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1絶縁膜103と、第1絶縁膜103に埋め込まれた導電膜109を含み且つ半導体基板101に達するコンタクト110と、半導体基板101及び第1絶縁膜103のそれぞれと、導電膜109との間に形成され、高融点金属を含む第1バリア層107とを備える。更に、第1バリア層107と導電膜109との間に形成され、第1バリア層107よりも水分透過性の低い第2バリア層118を備える。

(もっと読む)

半導体装置の製造方法

【課題】銅を主成分とするコンタクトプラグを有する半導体装置において、コンタクトプラグに隆起が発生することを防止する。

【解決手段】第1の層間絶縁膜102に、金属シリサイド層101に到達するコンタクトホール103を形成する工程(c)と、コンタクトホールの底面及び側壁に、高融点金属膜104を形成する工程(d)と、高融点金属膜上に、銅を主成分とする金属膜106Aを形成し、コンタクトホール内に、高融点金属膜を介して、金属膜が埋め込まれてなるコンタクトプラグ107を形成する工程(e)と、第1の層間絶縁膜及びコンタクトプラグの上に、第2の層間絶縁膜108を形成する工程(f)とを備え、工程(f)は、コンタクトプラグの表面に存在する酸素ガスを除去する工程(f1)と、工程(f1)の後に、コンタクトプラグの表面に存在する酸素ガスが除去された状態で、第2の層間絶縁膜を形成する工程(f2)とを含む。

(もっと読む)

一体型ビア及びビア端子を有する半導体回路基板、並びに関連するシステム及び方法

一体型ビア及びビア端子を有する半導体回路基板と、関連のシステム及び方法とが開示されている。特定の実施例に従う代表的な方法は、半導体回路基板に非貫通ビア(140)を形成することと、ビアの側壁面に保護層(122)を塗布することと、保護層が塗布された回路基板材料の除去から保護している間に、ビアの端面から回路基板材料を選択的に除去することにより端子穴(111)を形成することと、を含む。この方法は、ビア内の導電性材料が単一である導電性端子を形成するためにビア及び端子穴の双方に導電性材料を配置することをさらに含むことができる。端子に隣接する回路基板材料は、その後、回路基板の外部の導電性構造体に接続することができる端子を露出させるために除去することができる。 (もっと読む)

半導体装置の製造方法

【課題】生産性を極端に落とすことなく、開口の形状悪化を抑止するエッチング方法を提供する。

【解決手段】半導体基板1上に絶縁層2を介して形成されたパッド電極3を被覆するように前記半導体基板1の表面に支持体5を接着する工程と、前記半導体基板1の裏面から前記パッド電極3の表面に到達するようにビアホールを形成する工程とを有するものにおいて、前記半導体基板1に対して前記絶縁層2が露出しない位置まで第1の開口を形成する第1のエッチング工程と、前記半導体基板1に対して前記絶縁層2が露出する位置まで第2の開口8を形成する第2のエッチング工程とを、全ての開口に対して行うと共に、前記第2のエッチング工程は前記第1のエッチング工程よりも前記半導体基板に印加される交流電圧の周波数を低くする。

(もっと読む)

半導体装置

【課題】金属パッドの下方に位置する層間絶縁膜にクラックが発生し、クラック内に水分が進入することがあっても、金属パッドの近傍の配線の信頼性が低下することを防止する。

【解決手段】半導体基板10上に形成された層間絶縁膜18と、層間絶縁膜18を貫通して設けられたリング用金属配線20Aと、層間絶縁膜18を貫通して設けられたコンタクト用金属配線20Bと、層間絶縁膜18上及びリング用金属配線20Aの全上面上に形成された第1の保護絶縁膜21と、第1の保護絶縁膜21上に形成された金属パッド23とを備え、リング用金属配線20Aは、層間絶縁膜18のうち金属パッド23の下方に位置する領域にリング状に設けられており、金属パッド23は、第1の保護絶縁膜21に形成された第1の開口部21aを通じてコンタクト用金属配線20Bに接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線とバリア膜との密着性の低下、エレクトロマイグレーション耐性の低下、及び工程数の増加を抑制しつつ、めっき膜の膜厚がウェハ中心部とウェハ周辺部で異なることを抑制できる半導体装置の製造方法を提供する。

【解決手段】絶縁膜100に形成された溝102の側面及び底面に、添加元素を含む金属バリア膜120を形成する。次いで、金属バリア膜120上にシード膜142を形成し、さらにシード膜142をシードとしてめっき層(Cu膜144)を形成することにより、溝102内に金属膜140を埋め込む。次いで、金属バリア膜120及び金属膜140を熱処理することにより、金属バリア膜120と金属膜140の間に、金属バリア膜120を構成する金属、添加元素、及び金属膜140を構成する金属を含む合金層を形成し、かつ添加元素を金属膜140中に拡散させる工程とを備える。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61と、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に第1の保護膜70を形成する工程と、第1の保護膜70に、上部電極63に達する第1の開口70aを形成する工程と、第1の開口70aを形成した後に、第1の保護膜70及び第1の開口70aから露出する上部電極63の上方に層間絶縁膜71を形成する工程と、層間絶縁膜71に、第1の開口70aの内側で上部電極63に達する第1のホール71aを形成する工程と、第1のホール71aに第1の導体プラグ77aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】Cu配線パターンとキャップ層との界面を伝うCuの拡散を抑制し、同時にCu配線パターンの抵抗の増大を抑制するCuダマシン配線の製造法を提供する。

【解決手段】基板41上に側壁面と底面とにより画成された凹部を有する絶縁膜45を形成する。側壁面のうち、上端部を含む上側の第1の部分Dを覆い、凹部の底面と下側の第2の部分においては前記絶縁膜が露出するように覆う、金属膜47を形成する。凹部の側壁面と底面とを連続的に覆う導電性拡散障壁膜48を形成する。銅を充填し銅配線パターン49A、49B、49Cとする。絶縁膜上と銅配線パターンの表面を覆う絶縁性拡散障壁膜49を形成する。熱処理により、銅配線パターンと絶縁性拡散障壁膜との界面に、金属元素の濃集領域49Dを形成する。金属元素の濃集領域では、金属膜を構成する金属元素の濃度が、銅配線パターン中よりも高い。

(もっと読む)

半導体装置の製造方法

【課題】電気特性を高い精度で予測し、かつその予測式を用いて電気特性を一定化制御する、半導体装置の製造方法を提供する。

【解決手段】まず、半導体装置の製造途中で、半導体装置の拡散パラメータの値が取得される。次いで、後続の工程において実施される所定処理により決定される拡散パラメータのターゲット値が算出される。当該拡散パラメータは、予め取得された電気特性予測式に、取得された拡散パラメータの値と所望の電気特性値とを代入することにより算出される。電気特性予測式とは、半導体装置の電気特性と複数種の拡散パラメータとの対応関係を示す式である。続いて、当該ターゲット値を実現する、後続工程の所定処理の処理条件が決定される。そして、決定された処理条件で、後続工程の所定処理が実施される。

(もっと読む)

半導体装置およびその製造方法

【課題】電極上に膜(水素バリア膜、バリアメタル)が形成される場合に、電極上での膜のカバレッジ不良の発生を防止することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1では、強誘電体膜13上に、強誘電体膜13に接する電極下層15とこの電極下層15上に積層される電極上層16との積層構造を有する上部電極14が積層されている。そして、電極上層16の上面は、平坦化により、強誘電体膜13の表面モホロジーと無関係な平坦面となっている。したがって、電極上層16上で水素バリア膜17およびバリアメタル28をほぼ均一な厚さに形成することができ、上部電極14上での膜のカバレッジ不良の発生を防止することができる。

(もっと読む)

861 - 880 / 2,805

[ Back to top ]