Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

881 - 900 / 2,805

半導体装置及びその製造方法

【課題】貫通ビアと電極パッドとの接合強度を増大させることにより、3次元配線構造を有する半導体装置の機械的強度を増大させる。

【解決手段】第1の半導体チップ100と第2の半導体チップ200とが貼り合わされている。第1の半導体チップ100の表面部に電極パッド104が形成されている。第2の半導体チップ200中に貫通ビア114が形成されている。電極パッド104には掘り込み部111が形成されており、当該掘り込み部111内に貫通ビア114の底部が埋め込まれている。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18上に、SiおよびOを含む絶縁材料からなる犠牲層41が積層される。犠牲層41の積層後、熱処理が行われる。第2絶縁層6および犠牲層41にSiおよびOが含まれるので、熱処理が行われると、第2絶縁層6と合金膜18との界面および合金膜18と犠牲層41との界面において、Si、OおよびMnが結合し、それぞれMnSiOからなる第2バリア膜13および反応生成膜42が形成される。合金膜18に含まれるMnが反応生成膜42の形成に使用されることにより、第2バリア膜13の形成後、その第2バリア膜13の形成に寄与せずに合金膜18に残留するMnの量が減少する。そのため、合金膜18上に積層されるCu層20に拡散するMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】プリ・メタル層間絶縁膜の構成法としては、オゾンTEOSによる酸化シリコン膜の埋め込み特性の良好なCVD酸化シリコン系絶縁膜を成膜後、高温リフローさせて平坦化した後、CMPスクラッチ耐性が良好なプラズマTEOSによる酸化シリコン膜を積層し、更にCMPで平坦化することが考えられる。しかし、コンタクト・ホール形成プロセスにおいて、プリ・メタル層間絶縁膜中のクラックがコンタクト・ホール内に露出し、そこにバリア・メタルが入り込み、ショート不良の原因となることが明らかとなった。

【解決手段】本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

(もっと読む)

半導体装置

【課題】CMPによる平坦化時にディッシングや配線パターン剥離の発生を抑制して安定生産が可能で、ダミーパターン内における渦電流の発生に伴うインダクタンス素子のQ値の低下を抑制可能な半導体装置を提供。

【解決手段】半導体装置10は、基板と、この基板上に形成され化学的機械的研磨工程(以下CMPと称する)を制御するためのダミーパターン16と、基板上に螺旋状に形成されたインダクタンス素子15と、を有し、ダミーパターン16Pが、それぞれ先端が鋭角の突起Apを八つ有する多角形状の平面視形状を有するように形成されている。突起の先端を挟む両側の縁部に沿ってそれぞれ発生する渦電流は、向きが互い逆方向であるため相殺されて打ち消され、大きな渦電流とならない。また、縁部に沿って流れる渦電流の経路が長くなることにより抵抗が増加し、渦電流が流れる面積も減少するので、渦電流を抑制する。

(もっと読む)

半導体装置

【課題】半導体基板(半導体ウエハ)上に比較的大きな厚さの層間絶縁膜が形成される構成において、半導体基板に反り変形が生じることを抑制できる、半導体装置およびその製造方法を提供する。

【解決手段】半導体基板2上に形成される層間絶縁膜12は、複数の第1絶縁膜13の積層構造を有している。また、半導体基板2上には、トランスを構成する第1コイル10および第2コイル22が層間絶縁膜12を挟んで対向して設けられている。そして、各第1絶縁膜13には、第1絶縁膜13を貫通するビアホール24が形成され、各ビアホール24には、ビア23が埋設されている。

(もっと読む)

半導体装置

【課題】ボンディングパッドなどの開口内金属膜と層間絶縁膜上の表面金属膜との導通を確保することができる、半導体装置を提供する。

【解決手段】第2配線13上の層間絶縁膜21には、その表面から第2配線13に達するパッド開口22が形成されている。第2配線13におけるパッド開口22に臨む部分上には、AlCu合金からなるボンディングパッド25が形成されている。また、層間絶縁膜21上には、AlCu合金からなる電磁波シールド膜27が形成されている。そして、パッド開口22の側面上には、ボンディングパッド25と電磁波シールド膜27との導通を確保するための導通確保膜24が形成されている。ボンディングパッド25と電磁波シールド膜27とが直接に接続されなくても、導通確保膜24により、ボンディングパッド25と電磁波シールド膜27との導通を確保することができる。

(もっと読む)

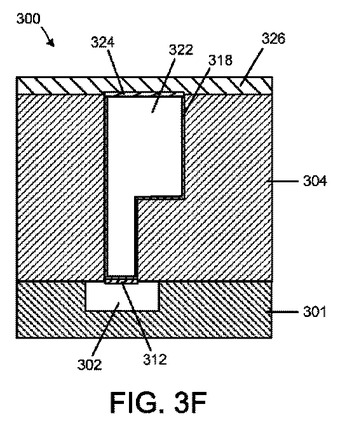

ダメージフリー被覆刻設堆積法

【課題】周辺表面を汚染もしくは乱さずに、スパッタリングした銅シード層を堆積させて、所望の形状に刻設する方法を提供する。

【解決手段】底部516と、側壁514と、上側開口526とを有する複数の凹状のデバイス特徴を含む基板上に銅シード層を堆積させる方法であって、a)基板表面からのスパッタリングを引き起こす態様において前記凹状のデバイス特徴の基板表面に衝突することなく前記銅シード層の第1の部分を前記基板上にスパッタ堆積するステップと、b)前記銅シード層の第2の部分を前記基板上にスパッタ堆積すると同時に、銅シード層の前記第1の部分の少なくとも一部を、前記複数の凹状のデバイス特徴のそれぞれの底部から対応する側壁へと再配分するステップと、を備える。

(もっと読む)

半導体装置

【課題】半導体装置の製造歩留まりを向上できる。

【解決手段】本発明の例に関わる半導体装置は、ウェハ1内に設けられる第1及び第2半導体チップエリア21,22と、第1及び第2半導体チップエリア21,22内の各々に設けられ、トランジスタが形成される第1素子領域51,52と、第1及び第2半導体チップ51,52間に設けられるダイシングエリア3Aと、ダイシングエリア3A内に設けられ、アライメントマークが形成されるアライメント領域35と、第1素子領域51,52とアライメント領域35との間に設けられ、ウェハ1表面に対して垂直方向に突出した凸部91,92を有する凸部形成領域71,72とを具備し、凸部91,92の上端は、ウェハ1表面より高い位置にあり、トランジスタのゲート電極12上端よりも低い位置にある。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】ワード線間に空隙を有する不揮発性半導体記憶装置で、従来に比してワード線間の容量の増大を抑えることができる不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板1上にゲート絶縁膜11、多結晶シリコン膜12、電極間絶縁膜13および多結晶シリコン膜14が順に積層された積層ゲート構造MGと、積層ゲート構造MGの下部のチャネル領域を挟んで形成されるソース/ドレイン領域と、を有するメモリセルトランジスタが複数隣接して配置され、隣接する積層ゲート構造MG間に空隙AG1,AG2ができるように連続したシリコン酸化膜がメモリセルトランジスタ上に形成され、電極間絶縁膜13の形成位置よりも高い位置での基板面に平行な空隙AG1,AG2の開口面積が、その位置よりも低い位置での基板面に平行な空隙AG1,AG2の開口面積よりも狭くなるように、積層ゲート構造MGの側面にシリコン酸化膜20,21が形成される。

(もっと読む)

ハードマスク及び二重露光により形成される半導体デバイスのコンタクト及びビア

【解決手段】

コンタクト要素がハードマスク(233)に基いて形成されてよく、ハードマスク(233)は、第1のレジストマスク(210)に基いて及び第2のレジストマスク(211)に基いて、コンタクト要素の最終的な設計寸法を代表し得る適切な交差区域(234)を画定するようにパターニングされてよい。その結果、横方向寸法の少なくとも一方は2つのレジストマスクの各々における非臨界的寸法として選択され得るので、それほど制限的ではない制約を伴うフォトリソグラフィプロセスに基いてレジストマスクの各々を形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】Cu層20の形成後、Cu層20上に、高純度Cuからなる犠牲層31が積層される。そして、犠牲層31の形成後、熱処理により、Cu層20と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。このとき、第2バリア膜13の形成に寄与しない余剰のMnは、Cu層20中に拡散する。Cu層20上に高純度Cuからなる犠牲層31が積層されているので、Cu層20に拡散したMnの一部は、Cu層20中を犠牲層31に引き寄せられるように移動し、犠牲層31に拡散する。この犠牲層31へのMnの拡散により、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

電子デバイス及びその製造方法

【課題】電子デバイス及びその製造において、直接的に最適なアライメント位置を検出する。

【解決手段】

電子デバイス100は、第1基板Wf1と、第1基板Wf1を搭載し且つ少なくとも一つの所定領域において第1基板Wf1と電気的に接続された第2基板Wf2とを備える。所定領域は、第1基板Wf1を貫通する少なくとも一つの貫通ビア110と、第1基板Wf1に、所定領域の一部を囲み且つ両端が接するのを避けて設けられた第1の配線111と、第1基板Wf1上に設けられ、第1の配線の両端にそれぞれ電気的に接続する一対の端子パッドと、第2基板Wf2上に設けられ、貫通ビア110と接続された少なくとも一つの導電部223とを有する。

(もっと読む)

半導体装置の製造方法

【課題】凹部の側壁部側からのめっきの成長を抑制して、ボイドの発生を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有するウェハWの少なくとも凹部1aの底部1bおよび側壁部1cに、シード膜3を形成する工程と、シード膜3上に、少なくとも凹部1aの底部1bに位置するシード膜3の部分3aが露出しかつ凹部1aの側壁部1cに位置するシード膜3の部分3bを覆うようにめっき抑制膜4を形成する工程と、シード膜3に電流を供給して、めっき抑制膜4の形成された凹部1aに埋め込まれるように電解めっき法によりめっき膜5を形成する工程と、めっき膜5に熱処理を施す工程とを備え、めっき抑制膜4が、シード膜3の構成材料より抵抗率が高くかつめっき膜5の構成材料と異なる材料から構成されることを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置

【課題】半導体基板(半導体ウエハ)上に比較的大きな厚さの層間絶縁膜が形成される構成において、半導体基板に反り変形が生じることを抑制できる、半導体装置およびその製造方法を提供する。

【解決手段】半導体基板2上に形成される層間絶縁膜12は、2つの第1絶縁膜13間に第2絶縁膜14を介在させた3層構造を有している。SiO2からなる第1絶縁膜13は、圧縮応力膜である。一方、SiNからなる第2絶縁膜14は、引張応力膜である。すなわち、層間絶縁膜12は、圧縮応力膜と引張応力膜との積層構造を有している。そのため、半導体基板2上において、圧縮応力膜の圧縮応力と引張応力膜の引張応力とが相互に打ち消し合う。したがって、層間絶縁膜12が比較的大きな厚さに形成されても、半導体基板2に反り変形が生じることを抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い微細化された配線構造を有する半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体基板上に形成された被接続部と、前記被接続部の上層に形成された所定の開口パターンを有する絶縁膜と、前記絶縁膜上に形成された所定の配線パターンを有する配線と、前記所定の開口パターンと前記所定の配線パターンとの論理積からなるパターンに含まれるパターンを有し、前記被接続部と前記配線とを接続するビアと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】第2バリア膜13の形成後に、SiH4を含むガスを用いたPECVD法により、Cu層20上にSiおよびOを含む絶縁材料からなる犠牲層21が積層される。犠牲層21にSiおよびOが含まれるので、犠牲層21の積層過程で、Cu層20と犠牲層21との界面にMnSiOからなる反応生成膜22が生じる。この反応生成膜22の生成にMnが使用されることにより、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート間のピッチが狭い場合における短チャネル効果の劣化を抑制する。

【解決手段】基板上に、第1ゲートと、第1ゲートに隣接する第2ゲートを形成する工程、第1ゲートの側壁に第1サイドウォールを、第2ゲートの側壁に第2サイドウォールを形成する工程、第1ゲート、第1サイドウォール、第2ゲート、第2サイドウォールをマスクとして、基板に第1不純物の注入を行う工程、全面に絶縁膜を堆積した後、絶縁膜をエッチングして、第1サイドウォールの側面に第3サイドウォールを、第2サイドウォールの側面に第4サイドウォールを、第1ゲートと第2ゲートの間において第3サイドウォールと第4サイドウォールとが接触するように形成する工程、第1ゲート、第1及び第3サイドウォール、第2ゲート、第2及び第4サイドウォールをマスクとして、基板に第2不純物の注入を行う工程、第3及び第4サイドウォールを除去する工程、を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】

誘電率を低減したSiC膜を銅拡散防止膜として用いることのできる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、−CH2−結合が環状にSiの2つの結合手を接続し、残り2つのSiの結合手に官能基R1,R2がそれぞれ結合され、官能基R1、R2は酸素を含まず2重結合を含む、原料を用いて、半導体基板上方に、酸素を含まない第1のSiC膜を成膜し、第1のSiC膜上に第1絶縁膜を成膜して、第1のSiC膜及び第1絶縁膜を含む層間絶縁膜を形成し、層間絶縁膜に銅配線を埋め込み、銅配線を覆って、層間絶縁膜上に、第1のSiC膜と同じ原料を用いて第2のSiC膜を成膜する。

(もっと読む)

半導体装置

【課題】 貫通電極を有する半導体装置において、半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 半導体基板10をエッチングして、半導体基板10の裏面からパッド電極12に到達するビアホール16を形成する。ここで、上記エッチングは、ビアホール16の底部の開口径Aが、パッド電極12の平面的な幅Cよりも大きく、また前記ビアホール16の深さの途中における開口径Bが、前記幅C及び前記開口径Aよりも小さくなるようなエッチング条件により行われる。次に、ビアホール16の底部でパッド電極12を露出する第2の絶縁膜17を、当該ビアホール16を含む半導体基板10の裏面上に形成する。次に、ビアホール16の底部で露出されたパッド電極12と電気的に接続された貫通電極20及び配線層21を形成する。さらに、保護層22、導電端子23を形成する。最後に、ダイシングにより半導体基板10を半導体チップ10Aに切断分離する。

(もっと読む)

ルテニウム金属キャップ層を形成する方法

ルテニウム(Ru)金属の堆積を半導体デバイスの製造に統合することで、銅(Cu)金属のエレクトロマイグレーション及びストレスマイグレーションを改善する方法が供される。本発明の実施例は、NHx(x≦3)ラジカル及びHラジカルによって、金属層及びlow-k誘電材料を含むパターニングされた基板を処理することで、前記low-k誘電材料に対する前記金属層上でのRu金属キャップ層の選択形成を改善する方法を有する。  (もっと読む)

(もっと読む)

881 - 900 / 2,805

[ Back to top ]