Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

821 - 840 / 2,805

半導体装置およびその製造方法

【課題】絶縁信頼性の劣化を低減し、銅配線の信頼性を改善する。

【解決手段】本発明の半導体装置は、半導体基板10と、シリコン(Si)と炭素(C)と酸素(O)とを含み、半導体基板10に形成された第一の多孔質絶縁膜11a及び第二の多孔質絶縁膜11bと、第一の多孔質絶縁膜11a中に埋め込まれた第一の銅配線12aと、第二の多孔質絶縁膜11b中に、それぞれ、埋め込まれた第二の銅配線12b及び銅ビア22と、第二の銅配線12a上に形成された第一のメタルキャップ膜13aと、第二の銅配線12b上に形成された第二のメタルキャップ膜13bと、を有する。第一、第二の多孔質絶縁膜11a、11bは、少なくとも上層のC/Si比が1.5以上であり、かつ、第一、第二の多孔質絶縁膜11a、11bの少なくとも上層に含有される空孔の最大径が1.3nm以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】エレクトロマイグレーションの抑制が図られた半導体装置を提供する。

【解決手段】半導体装置は、半導体素子の形成された半導体基板と、半導体基板の上方に、水分を含み、凹部が形成された層間絶縁膜と、凹部の内面上に形成され、非晶質及び多結晶の一方の結晶性を有する第1のバリアメタル層と、第1のバリアメタル層上に形成され、非晶質及び多結晶の他方の結晶性を有する第2のバリアメタル層と、第2のバリアメタル層上に形成された銅配線と、銅配線を覆って前記層間絶縁膜上に形成された銅拡散防止絶縁膜と、銅配線と銅拡散防止絶縁膜との界面に形成された金属酸化物層とを有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 貫通電極を有する半導体装置及び製造方法において、半導体装置の信頼性及び歩留りの向上を図る。

【解決手段】 電極パッド12に対応した位置で半導体基板11を貫通する貫通孔2を形成する。次に、貫通孔2を含む半導体基板11の裏面上に絶縁膜1を形成する。次に、少なくとも貫通孔開口部の絶縁膜1の表面に金属もしくは無機絶縁膜から密着安定化層3を形成する。

密着安定化層3の上に、ボトムエッチングのマスクとなるレジスト層4を形成する。次に、ボトムエッチングを行い、電極パッド12を露出させる。次に、レジスト層4を剥離して、ボトムエッチング後であっても凹凸のない絶縁膜1を得る。その後、低温プロセスで、バリア層5、シード層6、導電層7を形成して、パターニングを行い、密着安定化層3を有する貫通電極8付半導体装置を作る。

(もっと読む)

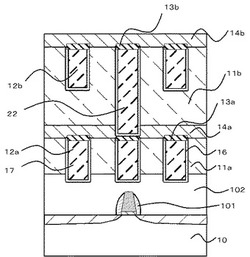

半導体装置

【課題】タングステン埋め込み配線に接続される信頼性の高いタングステンコンタクトを有する半導体装置を提供する。

【解決手段】半導体基板の主面上の第1層11に配設されるとともに、貫通孔を有し、タングステンを主成分とする第1配線12と、一端部13aが貫通孔を通って第1配線12の底面に至るとともに、バリアメタル14を介して貫通孔の側面12bに接触し、他端部13bが層間絶縁膜15を挟んで第1層11の上方の第2層16に配設された第2配線17に接続されたタングステンを主成分とする接続導体13と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】パッド電極の直下でのクラックの発生を抑制できるようにした半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成されたLOCOS膜3と、LOCOS膜3上に形成されたポリシリコン膜5と、LOCOS膜3上に形成されたILD膜7と、ILD膜7に形成され、ポリシリコン膜5を底面とする第1の開口部と、第1の開口部内に形成され、ポリシリコン膜5と接するパッド電極9と、を有する。ポリシリコン膜5は、ILD膜7よりも強度があり、衝撃に対する耐性が高いため、プローブ検査の際にクラックの発生を抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】消費電流及び抗折強度に優れる半導体装置を実現する。

【解決手段】半導体装置10は、半導体素子11と、半導体素子11の第1面の表面部に設けられた拡散領域12と、半導体素子11の第1面上に設けられた第1金属配線14と、半導体素子11を厚さ方向に貫通する貫通孔15と、貫通孔15内に設けられ、第1金属配線14bの裏面に接し且つ半導体素子11における第1面の反対側の第2面にまで延びる貫通電極16とを備える。更に、半導体素子11の第2面に設けられた凹部17と、凹部17内に設けられ、貫通電極16に電気的に接続された第2金属配線17とを備える。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線が形成された層間絶縁膜を有する半導体装置において、層間絶縁膜と、層間絶縁膜下に形成された下層との界面に、剥離が発生することを防止する。

【解決手段】半導体基板上に形成された第1の層間絶縁膜10と、第1の層間絶縁膜10上に形成された第2の層間絶縁膜14と、第2の層間絶縁膜14の上部領域に形成された第1の配線21とを備え、第2の層間絶縁膜14は、空孔14bを含有する多孔質領域14Bと、非多孔質領域14Aとで構成され、多孔質領域14Bは、第2の層間絶縁膜14のうち、第1の配線21の周囲に位置する領域に形成され、非多孔質領域14Aは、少なくとも第1の層間絶縁膜10と多孔質領域14Bとの間に介在して形成されている。

(もっと読む)

半導体装置の製造方法、および、それに用いる半導体ウェハ

【課題】多層配線層の検査工程を含む半導体装置の製造技術において、検査の迅速性を損なうことなく、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体ウェハの主面上に中間配線層(工程s03,s05)、ビア層(工程s04,s06)、最上配線層(工程s07)を形成する。中間配線層を形成した後の電位コントラスト観察工程vc01,vc02と、最上配線層を形成した後の電気的検査工程ec01とを有する。中間配線層は、平面積が大きい第1配線パターンと、面積が小さく、浮遊状態となる第2配線パターンとを有する。最上配線層は、第1配線パターンに導通する第1最上配線パターンと、第2配線パターンに導通する第2最上配線パターンとを有する。電気的検査では、第1最上配線パターンと第2最上配線パターンとの間に電位差を与えて導通状態を検査する。

(もっと読む)

半導体装置

【課題】窒化珪素膜でCu配線を挟み込むことによりCuによりTFTが汚染されるのを防ぐ。

【解決手段】結晶性半導体膜と、結晶性半導体膜上のゲート絶縁膜とゲート絶縁膜上のゲート電極と、結晶性半導体膜及びゲート電極上の第1の層間絶縁膜と、第1の層間絶縁膜に設けられた第1のコンタクト部を介して結晶性半導体膜に電気的に接続される第1の配線と、第1の層間絶縁膜及び第1の配線上の、第1の配線の一部を露出させた第2のコンタクト部が設けられた第1の窒化珪素膜及び第1の窒化珪素膜上の第2の層間絶縁膜と、第2のコンタクト部により露出させた第1の配線上に設けられたCuの拡散を防ぐバリア層と、第2のコンタクト部に設けられたバリア層上のCuでなる第2の配線と、第2の配線を被覆して設けられた第2の窒化珪素膜とを有する。

(もっと読む)

めっき装置、めっき方法および半導体装置の製造方法

【課題】めっき膜における膜厚の均一性を向上させることができるめっき装置およびめっき方法、ならびに配線不良を低減することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、基板Wの被めっき面W1が上向きとなるように基板Wを保持しつつ基板Wを回転させるホルダ3と、ホルダ3で保持された基板Wの周縁部W2に接触するカソード4と、ホルダ3で保持された基板Wの中央部W3に向けてめっき液Lを吐出し、かつアノードとしても機能するノズル6とを具備することを特徴とする、めっき装置1が提供される。

(もっと読む)

薄膜多層配線基板およびその製造方法

【課題】 剥離の発生の少ない薄膜多層配線基板とその製造方法を提案する。

【解決手段】 少なくとも一つの前記配線層が、下層の配線層上に形成された第一のSiO2薄膜と、前記第一のSiO2薄膜上に形成されたSiON薄膜と、前記SiON薄膜上に形成された第二のSiO2薄膜と、前記第二のSiO2薄膜に埋め込まれて形成された配線導体と、前記配線導体と接続しかつ前記第一のSiO2薄膜、前記SiON薄膜および前記第二のSiO2薄膜を貫通して前記下層の配線層の配線導体と電気的に接続するビア導体と、前記第二のSiO2薄膜上に形成されたSiN薄膜と、で構成されている。

(もっと読む)

半導体装置

【課題】ソース及びドレインとの接触抵抗のばらつきが少なく、ソース同士が容易に接続

可能なコンタクトプラグ構成の半導体装置を提供する。

【解決手段】ソース及びドレイン領域18、19を有する半導体基板11と、浮遊ゲート

膜22を有し、ソース及びドレイン領域18、19の間の表面に配設されたゲート電極膜

28と、ゲート電極膜28の上に上下を絶縁されたソース接続膜33と、ゲート電極膜2

8及びソース接続膜33を被うサイドウォール絶縁膜37及びバリア絶縁膜39と、バリ

ア絶縁膜39を埋め込む下部及び上部層間絶縁膜41、43と、ソース領域18に接続さ

れ、下部及び上部層間絶縁膜41、43を貫通し断面が楕円形の柱状体をなし、柱状体の

側面でソース接続膜33と接続されたソースコンタクト45と、ドレイン領域19に接続

され、下部及び上部層間絶縁膜41、43を貫通し断面が楕円形の柱状体をなすドレイン

コンタクト47とを備える。

(もっと読む)

積層半導体装置及び積層半導体装置の製造方法

【課題】動作の安定した積層半導体装置を提供する。

【解決手段】単結晶シリコンのベース部と、ベース部の上の絶縁層と、絶縁層の上の単結晶シリコン層と、単結晶シリコン層に形成され絶縁層に達する分離溝構造と、分離溝構造で囲まれた単結晶シリコン層のボディ領域と、ボディ領域に形成されるトランジスタと、少なくともベース部および絶縁層を貫通し、ボディ領域に電気的に結合する貫通結合部とを有する第1半導体装置と、貫通結合部に接する外部接続部を有する第2半導体装置と、を備え、第2半導体装置は、貫通結合部を介して第1半導体装置のボディ領域の電位を制御する。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】微細配線であっても、Cu配線の配線抵抗上昇の低減と信頼性向上とを両立する。

【解決手段】半導体装置は、絶縁膜2と、絶縁膜2に形成された溝5と、溝5の側壁及び底面に形成された、チタン(Ti)とタンタル(Ta)との合金からなるバリアメタル膜3と、バリアメタル膜3に積層され、溝5の中に位置する銅(Cu)配線4と、を有する。バリアメタル膜3のチタン濃度は、0.1at%以上14at%以下である。

(もっと読む)

低誘電率膜の堆積処理方法、基板処理システム、デュアルダマシン構造の形成方法、およびデュアルダマシン構造

【課題】集積回路製造工程において、ガスを化学的に反応させて化学気相成長又はCVDにより、低誘電率膜の堆積処理方法を提供する。

【解決手段】約10Wから約200Wの一定RFパワーレベルか、または約20Wから約500WのパルスRFパワーレベルで、1以上のシリコン化合物と酸化ガスからなるプロセスガスから、パターン化された金属層上にコンフォーマルライニング層を堆積する工程と、前記ライニング層上にギャップ充填層を堆積させる工程とを含む低誘電率膜の堆積処理方法。

【効果】シリコン酸化物は、配線間の静電結合を弱めて、1つの堆積チャンバで高信頼性のデュアルダマシン構造を製造する集積プロセスにおいてさらに有効である。

(もっと読む)

電子デバイスの製造方法及び設定装置

【課題】電子デバイスの更なる微細化及び高集積化が進んでも、リソグラフィー及びエッチングにより被加工対象の極めて高い寸法精度を達成し、信頼性の高い電子デバイスを実現する。

【解決手段】被加工対象上に形成されたレジスト膜を加工してレジストパターンを形成する工程と、レジストパターンをマスクとして、所定のエッチング条件で被加工対象をエッチングする工程とを実行する際に、形成されたレジストパターンの寸法及び形状(膜厚及びテーパ角度)を測定し、測定されたレジストパターンの寸法及び形状に基づいて前記エッチング条件を調整する。

(もっと読む)

半導体装置

【課題】PIDの影響を遮断することのできるレイアウト手法を用いてアンテナダイオードを配置することにより、PIDに起因する電界効果トランジスタの特性劣化を防止して、信頼度の高い半導体装置を実現する。

【解決手段】第1アンテナダイオードAD1とnMISのゲート電極16とを第1層目の配線M1を介して電気的に接続し、第2アンテナダイオードAD2と他の半導体素子とを第1層目の配線M1から第4層目の配線(アナログブロック内の最上層配線から1層下の配線)M4を介して電気的に接続する。さらに第1アンテナダイオードAD1と電気的に繋がる第4層目の配線M4と第2アンテナダイオードAD2と電気的に繋がる第4層目の配線M4とをアナログブロック内の最上層配線である第5層目の配線25によって結線する。

(もっと読む)

有機表面パッシベーションでめっきの進行に差を付けて遅らせることによるボトムアップめっき

本発明の実施形態は、概して、半導体基板を処理するための装置及び方法に関するものである。一実施形態は基板を処理する方法を提供し、この方法は、基板に形成されたトレンチ構造又はビア構造を有する基板を覆うようにシード層を形成することと、シード層の一部を有機パッシベーション膜で被覆することと、前記トレンチ構造又はビア構造をめっき液に浸漬して、前記有機パッシベーション膜で被覆されないシード層の上に導電材料を堆積させることとを含む。  (もっと読む)

(もっと読む)

821 - 840 / 2,805

[ Back to top ]