Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

781 - 800 / 2,805

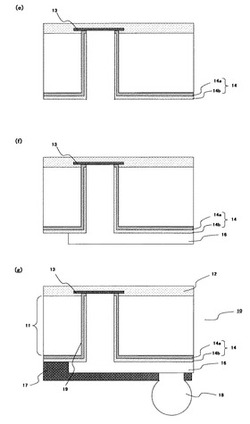

半導体装置及びその製造方法

【課題】貫通孔(接続孔)内に形成された絶縁膜上に設けられる配線層と半導体基板との間の電気的絶縁性の不良の発生が低減された半導体装置の製造方法を提供する。

【解決手段】半導体基板11の一方の面上に第1の絶縁層12を介して位置する第1の配線層13と、半導体基板の他方の面から第1の配線層に至る接続孔19を形成する。接続孔の側面から他方の面に亘って半導体基板上に位置し、接続孔内で第1の配線層に接する第2の絶縁層14を形成する。接続孔の側面上から他方の面上に亘って第2の絶縁層上に位置し、接続孔内で第1の配線層に接する第2の配線層16を形成する。この形成において、第2の絶縁層を、膜質の異なる2種の絶縁膜14a、14b又はそれ以上の絶縁膜の積層体から構成する。

(もっと読む)

スカロップ状側壁を有するシリコン貫通ビア

【課題】 スカロップ状側壁を有するシリコン貫通ビアを提供する。

【解決手段】 基板、前記基板を覆う、1つ以上の誘電体層、及び前記基板を穿通して延伸し、スカロップ状の表面の側壁を有し、前記側壁に沿ったスカロップは約0.01μmより大きい深さを有するシリコン貫通ビア(TSV)を含む半導体デバイス。

(もっと読む)

エレクトロマイグレーション耐性を有するビア・ライン相互接続体

【課題】 エレクトロマイグレーション耐性を有するビア・ライン間相互接続構造体及びその製造方法を提供する。

【解決手段】 導電性ビアの上層金属ライナと、下方の金属ラインの下層金属ライナとの間に、ライナ・ライナ間接触を形成する。ライナ・ライナ間接触は、急激なエレクトロマイグレーションによる故障を抑制し、金属相互接続構造体のエレクトロマイグレーション耐性を強化する。少なくとも1つの誘電体材料部分は、上層金属ライナと下層金属ライナの間の直接接触を保証するように配置された複数の誘電体材料部分を含むことができる。代替的に、少なくとも1つの誘電体材料部分は、リソグラフィ・オーバーレイ変動の許容範囲内でライナ・ライナ間直接接触が形成されるのを保証するのに十分な、導電性ビア領域との横方向の重なりを有する領域の単一の誘電体部分を含むことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】前記従来のエアーギャップを有するMISトランジスタ及びその製造方法では、ゲート電極の周囲にエアーギャップを設けるため、ゲート電極に近接して応力絶縁膜を形成することができない。

【解決手段】半導体装置は、ゲート絶縁膜13と、ゲート電極14と、ソースドレイン領域19と、コンタクトプラグ22と、応力絶縁膜23とを備えている。ゲート電極14の側方のうちゲート電極14とコンタクトプラグ22との間に位置する領域のみに空洞24が形成されており、応力絶縁膜23は半導体基板10上にゲート電極14を覆うように形成されており、半導体基板10におけるゲート電極14の直下に位置するチャネル領域に対して応力を生じさせる。

(もっと読む)

導電層形成方法及び半導体装置

【課題】 貫通電極内部に導電層を形成する方法及び半導体装置において、貫通孔内の均一なメッキ付き周り性を向上させ、タクトタイムの短い導電層形成方法及び半導体装置を提供する。

【解決手段】 前記貫通孔の内部に第一のメッキ層を形成する第一のメッキ工程と、

前記第一のメッキ工程の後、前記貫通孔の開口部に前記第一のメッキ層とは異なる材料から成るメッキ抑制層を形成するメッキ抑制層形成工程と

前記メッキ抑制層形成工程の後、前記貫通孔の内部にメッキにより第二のメッキ層を形成する第二のメッキ工程を有する。

(もっと読む)

半導体素子の製造方法

【課題】タングステン等のCMP(化学機械研磨)後、エロージョン量をモニタリングできるパターンを提示する。

【解決手段】ホールアレイサイズスプリットaと配列間スペースの長さスプリットbを一定に規定したモニタリングパターンを利用して、プラグCMP時に発生するエロージョンレベルを評価する。前記ホールアレイサイズによる影響はホールアレイサイズに応じて増加するため、エロージョン量は特定のサイズにおいて飽和になるのかをモニタリングする。また前記配列の間で影響を受けるスペースの長さをモニタリングする。

(もっと読む)

半導体集積回路装置

【課題】車載用等の半導体集積回路装置においては、一般に、実装上の都合で、金線等によるワイヤ・ボンディングによって半導体チップ上のアルミニウム・パッドと外部とが相互接続されることがある。しかし、これらの半導体集積回路装置は、比較的高温(摂氏150度前後)で長時間使用されるため、アルミニウムと金の相互作用によって、接続不良が発生する。

【解決手段】本願発明は、半導体集積回路装置(半導体装置または電子回路装置)の一部である半導体チップ上のアルミニウム系ボンディング・パッド上に、バリア・メタル膜を介して、電解金メッキ表面膜(金系金属メッキ膜)を設け、それと配線基板等(配線基体)の上に設けられた外部リード間を金ボンディング・ワイヤ(金系ボンディング・ワイヤ)で相互接続したものである。

(もっと読む)

半導体装置およびその製造方法

【課題】配線に含まれる金属の拡散を効果的に抑制することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体基板上に形成された絶縁層と、前記絶縁層中に形成された金属を含む配線と、前記配線の上面に接し、前記配線の上面の幅とほぼ等しい幅を有する第1の領域と、前記第1の領域上に位置する前記第1の領域の幅よりも広い幅を有する第2の領域を含む第1のバリアメタルと、前記配線の下面および側面、前記第1の領域の側面、ならびに前記第2の領域の下面に接する第2のバリアメタルと、を有する。

(もっと読む)

半導体装置の製造方法

【課題】低抵抗の導電部を備える、信頼性の高い半導体装置を提供する。

【解決手段】ビアホール36a内及び配線溝36b内に、バリア層37を介して、CnMnを含有する第1導電層38、及びCuを主成分とする第2導電層39を形成し、清浄化後、低温酸化を行い、第1,第2導電層38,39表面にCu酸化物層40を形成する。その後、キャップ層の形成を行い、その状態で高温条件の熱処理を行うことで、第1,第2導電層38,39内のMnをCu酸化物層40に拡散させ、キャップ層との界面に、Cu酸化物層40にMnが含有された化合物層を形成する。これにより、第1,第2導電層38,39内のMnを減少させることが可能になり、さらに、キャップ層の密着性を向上させることが可能になる。

(もっと読む)

CMOSイメージセンサの製造方法及びCMOSイメージセンサ

【課題】CMP(化学機会研磨)による、酸化膜界面の界面準位発生による画質低下を低減する。

【解決手段】層間絶縁膜30を貫通する窓に埋め込まれて化学機械研磨により平坦化されたプラグ層50と、前記層間絶縁膜30上から前記プラグ層50上に延在するように堆積されたTi(チタン)膜と、前記Ti膜上に堆積されたAl(アルミニウム)乃至Cu(銅)を含む配線層70と、前記層間絶縁膜30と前記Ti膜との間に形成され、水素を透過しない下敷膜55とを備えることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】酸素ガスを主に含有したガスでエッチングを行う必要がある金属材料を用いてピラー型電極を形成する際に、ピラー型電極のアスペクト比が高くなると製造が困難になるという課題があった。

【解決手段】層間絶縁膜上に第1〜第6の絶縁膜を積層した後、第1のフォトレジスト膜を形成する工程と、前記第1のフォトレジスト膜をマスクとして第1の溝部を形成する工程と、前記第1の溝部を充填するように電極材料を堆積する工程と、前記第4の絶縁膜上に第7〜第9の絶縁膜を形成した後、第2のフォトレジスト膜を形成する工程と、前記第2のフォトレジスト膜をマスクとして第2の溝部を形成すると共に、前記電極材料をピラー型に残存させる工程と、前記第8、前記第7、前記第4および前記第2の絶縁膜を除去して、前記電極材料からなるピラー型電極を露出する工程と、を有する半導体装置101の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

集積回路用相互接続構造の製造方法

【課題】化学機械研磨(CMP)を用いて過剰なバリアと導電材料を除去して、これにより堆積における不均一性を補償するより広いプロセスウインドウを形成する半導体デバイスの製造方法を提供する。

【解決手段】基板1の表面上に、誘電体材料のトップ層2を堆積する工程と、第1開口部7をエッチングし、第1導電性材料8を用いて第1開口部を充填し、第1CMP工程を行って、第1導電性構造3を形成する工程と、1つの第2開口部13をエッチングし、第2導電性材料10を用いて第2開口部を充填し、第2CMP工程を行って、第2導電性構造4を形成する工程と、を含み、第1開口部をエッチングし充填する工程の前に、誘電体トップ層の上に共通のCMPストップ層5を堆積して、第1開口部の充填後のCMPプロセスと第2開口部の充填後のCMPプロセスとを停止するために使用する工程とを含む。

(もっと読む)

特別に先細りされた遷移ビアを備えた半導体デバイスのメタライゼーションシステム

【解決手段】

半導体デバイスのメタライゼーションシステムにおいて、対応するエッチングシーケンスを修正することによって、増大された程度の先細りを伴う遷移ビアを設けることができる。例えば、ビア開口を形成するためのレジストマスクが、対応するマスク開口の横方向サイズを増大するために、1回又は数回侵食されてよい。明白な程度の先細りにより、ビア開口及びそれに接続される幅広の溝を共通的に充填するための後続の電気化学的堆積プロセスの間、強化された堆積条件が達成され得る。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の寄生容量を低減させて、配線の微細化させた半導体装置を効率よく製造できる方法を提供する。

【解決手段】有機材料からなる低誘電率絶縁膜3を形成した後、電子ビームを照射して低誘電率絶縁膜3の表面側にメチル基の濃度が相対的に低く、親水性を有する改質層31を形成する。さらに、エッチングによって低誘電率絶縁膜3に配線やコンタクトホールなどの溝パターン6を形成し、Cuからなるめっき層10を析出させる。CMP法による研磨で改質層31の少なくとも一部を研磨し、Cuからなる配線や導電性プラグといった導電性パターン11を形成する。

(もっと読む)

半導体装置の製造方法

【課題】レジストポイズニングによる微細パターンの解像不良を低減して高品質な半導体装置を歩留まり良く提供することである。

【解決手段】 下層絶縁層を設ける工程と、前記下層絶縁層上に上層絶縁層を設ける工程と、前記上層絶縁層上にレジスト層を設ける工程と、前記レジスト層を所定パターンに形成し、該所定パターンのレジスト層を用いて絶縁層を所定パターンに形成する工程とを有する半導体装置の製造方法において、

前記下層絶縁層と前記上層絶縁層との境界領域に、N−H結合を有する物質とC−H結合を有する物質とを共に有することは無い中間層が形成される工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ誘電体膜の劣化を防止しながら、金属配線間を絶縁膜で所望に埋め込むことができる半導体装置の製造方法を提供すること。

【解決手段】シリコン基板(半導体基板)1の上方に下地絶縁膜9を形成する工程と、キャパシタQ1、Q2を下地絶縁膜9の上に形成する工程と、キャパシタQ1、Q2を覆う第1層間絶縁膜68を形成する工程と、第1、第2配線溝30、33と、該配線溝30、33の底部から下に延びる第1、第2コンタクトホール31、34とを第1層間絶縁膜68に形成する工程と、第1、第2配線溝30、33と第1、第2コンタクトホール31、34とに第1拡散防止膜35と第1銅膜36(第1導電体)とを埋め込む工程と、水素を含まない還元性ガス中において第1銅膜36をアニールする工程とを有することを特徴とする半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

空隙を充填するべく低抵抗率のタングステン膜を堆積させる方法

【課題】抵抗率が低く、表面粗度が低く反射率が高いタングステンを、CVD法により基板上の間隙または凹状特徴部分に充填する方法を提供する。

【解決手段】基板に設けられた凹状部分を部分的に充填するタングステンバルクを堆積した後で、堆積されたタングステンの上部分を除去する。上部分の除去は、活性化されたフッ素種に基板を暴露することによって行われる。堆積されたタングステン粒子のうち急峻で突出している突起の頂点を選択的に除去することによって、除去処理は、凹状部分の側壁に沿ってタングステンを研磨することになる。堆積−除去のサイクルを複数回実行して、凹状部分を埋める。このようにして凹状部分が充填されると、CMPにおいてコアリング(coring)が発生しにくくなる。

(もっと読む)

誘電ライン・バイアのエレクトロマイグレーション耐性が向上した界面層を有する相互接続構造およびその製造方法

【課題】 相互接続構造内にガウジング・フィーチャを導入することなくエレクトロマイグレーション耐性を向上させる相互接続構造を提供する。

【解決手段】 この構造は、バイア開口の底部に存在する金属界面層(または金属合金層)を含む。バイア開口は、第1の導電材料が埋め込まれた第1の誘電材料の上に位置する第2の誘電材料内に位置する。バイア開口の底部に存在する金属界面層(または金属合金層)は、第1の誘電体内に埋め込まれた下にある第1の導電材料と第2の誘電材料内に埋め込まれた第2の導電材料との間に位置する。また、エレクトロマイグレーション耐性が向上した相互接続構造を製造する方法も提供する。

(もっと読む)

電子装置、電子装置の製造方法、電子機器

【課題】端子間の接合性に優れ高い信頼性を備えたものにするとともに、端子の狭ピッチ化も容易に対応できる電子装置、電子装置の製造方法、電子機器を提供する。

【解決手段】本発明の半導体装置1は、半導体基板10と、半導体基板10に形成された貫通孔7内に設けられるとともに半導体基板10の能動面10A側に部分的に突出する貫通電極5と、を有し、貫通電極5は、樹脂コア9と、樹脂コア9の少なくとも一部を覆う導電膜15と、を有する。

(もっと読む)

781 - 800 / 2,805

[ Back to top ]