Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

661 - 680 / 2,805

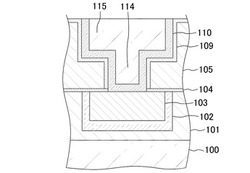

半導体装置及びその製造方法

【課題】配線の埋め込み不良及び配線抵抗の上昇を抑えると共に、信頼性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板101の上に形成された絶縁膜105と、絶縁膜105中に形成された、銅を含む材料からなる埋め込み配線115とを備えている。絶縁膜105と埋め込み配線115との間には、白金族元素を含む材料からなるバリア膜110が形成されている。絶縁膜105とバリア膜110との間には、絶縁膜105よりも密度が高い高密度絶縁膜109が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法における新規な平坦化処理を提供する。

【解決手段】半導体装置の製造方法は、半導体基板を有する半導体装置の製造方法であって、前記半導体基板の上に絶縁膜を形成する第1の工程と、前記絶縁膜に第1の穴を形成する第2の工程と、前記絶縁膜に前記第1の穴より浅い第2の穴を形成する第3の工程と、前記第1の穴に導電部材を埋め込むことにより導電部を形成するとともに、前記第2の穴に前記導電部材を埋め込むことにより平坦化補助部を形成する第4の工程と、前記導電部、前記絶縁膜、及び前記平坦化補助部を前記平坦化補助部が除去されるまで研磨することにより、前記導電部及び前記絶縁膜のそれぞれの上面を平坦化する第5の工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体装置の製造方法

【課題】保護素子としてSBDを搭載したMOSFETにおいては、SBDの特性を確保するためアルミニウム・ソース電極下のアルミニウム拡散バリア・メタル膜として、TiW(タングステンを主要な成分とする合金)膜が使用される。しかし、本願発明者らが検討したところによると、タングステン系バリア・メタル膜はTiN等のチタン系バリア・メタル膜と比べて、バリア性が低い柱状粒塊を呈するため、比較的容易にシリコン基板中にアルミニウム・スパイクが発生することが明らかとなった。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜をスパッタリング成膜によって形成する際、その下層をウエハ側にバイアスを印加したイオン化スパッタにより成膜し、上層をウエハ側にバイアスを印加しないスパッタにより成膜するものである。

(もっと読む)

半導体装置

【課題】電極部と貫通電極層の間の抵抗値ばらつきに依存しない信頼性に優れた半導体装置を提供する。

【解決手段】半導体基板表面2aの第1絶縁膜8の中に、外部接続端子を有する電極部18が形成され、基板をビアホール10が貫通し、ビアホール側壁10a及び基板裏面の第2絶縁膜12とビアホール底面の第1絶縁膜とに貫通電極層11が形成され、電極部と貫通電極層との間にシリサイド層9を接続形成し、ビアホール中心軸を含む平面で切断された断面において、シリサイド層の幅A≦ビアホール底部の幅Bである。

(もっと読む)

半導体構造体及びその形成方法

【課題】 相互接続構造の信頼性及び拡張性を改善する相互接続構造のための冗長金属拡散バリア層を提供する。

【解決手段】 冗長金属拡散バリア層は、誘電体材料内に設けられた開口内に配置され、且つ開口内に存在する拡散バリア層及び導電性材料の間に配置される。冗長拡散バリア層は、Ru並びに純粋なCo若しくはN,B及びPのうちの少なくとも1つを含むCo合金からなる単層若しくは多層構造である。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線の微細構造の維持、TDDB寿命の確保および低抵抗を実現する。

【解決手段】半導体装置100は、基板102と、基板102上に形成された層間絶縁膜104と、層間絶縁膜104中に形成された配線120と、を含み、配線120は、断面視において、最上面から下方にかけて幅が広くなる領域を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】平坦な表面を有する層間絶縁膜を短時間で形成することができ、また、層間絶縁膜の厚さの増大を招くことなく、金属イオンによる半導体基板の汚染に対する長期信頼性を保証することができる、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板2と、半導体基板2上に形成された層間絶縁膜8とを備えている。そして、層間絶縁膜8は、半導体基板2側から順に、HDP膜10、ゲッタリング層12およびNSG膜11が積層された構造を有している。ゲッタリング層12は、金属イオン、とくに可動イオンを捕獲する性質を有している。

(もっと読む)

スパッタリングターゲット及びこれを利用して製造される半導体素子

【課題】スパッタリングターゲット及びこれを利用して製造される半導体素子を提供する。

【解決手段】重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成されるスパッタリングターゲットであり、また、バリア層と、バリア層上のシード層と、シード層上の導電層と、を備え、導電層は、重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成される、タングステンとニッケルとの合金薄膜を備える半導体素子である。

(もっと読む)

半導体装置の製造方法

【課題】複数の絶縁膜を有する積層膜を形成する場合のスループットの向上等を実現し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上に、少なくともトリメチルシリルアセチレンを原料ガスとして用いて、組成の異なる複数の絶縁膜34、36、38、40を有する積層膜及び組成の異なる複数の絶縁膜56,58,60,62を有する積層膜64を、同一の反応室内において大気開放することなく連続的に形成する工程を有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

気相成長装置と半導体装置の製造方法

【課題】シランとアンモニアの混合ガスソークによる銅拡散防止絶縁膜形成前の銅配線表面処理を改善できる気相成長装置、および表面状態がよく、抵抗が低い銅配線を有する半導体装置の製造方法を提供する。

【解決手段】シランを供給できるガス供給系1aと反応室を接続する、2つ以上のバルブを含む連続バルブの1つをノーマリオープンとし、ガス供給系と排気系を接続する捨てガスライン3のノーマリクローズのバルブV14と連動させることにより、反応室内の残留ガスの影響を抑制する。

(もっと読む)

半導体装置の製造方法

【課題】複数の同種の製造装置を用いて半導体装置を製造する場合に、製品間での寸法のばらつきの発生を抑制できる技術を提供する。

【解決手段】制御機器CDをそれぞれの露光機に対して個別に配置する。露光処理が完了した各ロットは、どの露光機で露光処理がなされたかによって分類され、露光機毎に、露光機を調整するためのパラメータが製品情報収集部CD1に収集され、最適製造条件計算部CD2にて処理条件が計算され、計算された処理条件が設定される。すべてのロットは、露光処理を行う露光機が予め割り当てられ、露光処理が済んでいないロットは、分類機CMによって割り当てられた露光機へ振り分けられ、制御機器CDによって求められた処理条件で露光処理が行われる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート配線に達するコンタクトホールを確実に形成し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38を形成する工程と、第1応力膜とエッチング特性が異なる絶縁膜40を形成する工程と、第1領域2を覆う第1マスク60を用いて、第2領域内の絶縁膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の絶縁膜をサイドエッチングする工程と、第1マスクを用いて第2領域内の第1応力膜をエッチングする工程と、絶縁膜とエッチング特性が異なる第2応力膜を形成する工程と、第2領域を覆い、第1領域側の端面が絶縁膜上に位置する第2マスクを用いて、第2応力膜の一部が第1応力膜の一部及び絶縁膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】第2絶縁層にビアとなる接続孔を形成するときにビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。エッチングストッパー膜200は、第1絶縁層120上、エアギャップ128上、及び配線162上に形成されている。第2絶縁層220はエッチングストッパー膜200上に形成されている。ビア262は第2絶縁層220に埋め込まれており、配線162に接続している。そしてエッチングストッパー膜200は、エアギャップ128上に位置する部分202が、配線162上に位置する部分より厚い。

(もっと読む)

半導体装置及びその製造方法

【課題】 貫通電極を有する半導体装置の信頼性及び歩留まりの向上を図る。

【解決手段】 本発明の半導体装置は、半導体チップ10Aと、前記半導体チップ10Aの表面上に第1の絶縁膜11を介して形成されたパッド電極12と、前記パッド電極12の一部上及び前記第1の絶縁膜11上に形成され、かつ前記パッド電極12を露出する開口部14を有した第2の絶縁膜13と、前記開口部14を通して前記パッド電極12と電気的に接続されて前記第2の絶縁膜11の一部上に延びる第1の配線層15と、前記パッド電極12を介して前記開口部14に対峙し、前記半導体チップ10Aの裏面から当該パッド電極12に到達し、かつ前記開口部14と実質的に同等の開口径を有するビアホール16と、前記ビアホール16内に形成され、かつ当該ビアホール16を通して前記パッド電極12と電気的に接続された貫通電極20と、を備えることを特徴とする。

(もっと読む)

小臨界次元の接点装置及び相互接続子用の超薄低抵抗タングステンフィルムの堆積方法

【課題】高縦横比の特徴部のボイドなしの充填方法を提供する。

【解決手段】種々の実施例に於いて、この方法は低温化学蒸着工程によるタングステンでの特徴部の充填に関する。或る実施例に於いて、工程温度は特徴部充填の化学蒸着の間約350°C以下に維持される。この低温化学蒸着タングステン充填により、標準の化学蒸着充填と同様は薄膜抵抗を達成する一方、高縦横比の特徴部への向上された充填と下地層へとのフッ素移動への向上されたバリヤが得られる。発明は更に低抵抗を有するタングステンフィルムの堆積方法に関する。種々の実施例に於いて、この方法ではタングステンバルク層の堆積及び/或は低温化学蒸着によるバルク層の堆積の前に堆積された核形成層に低温低抵抗処理を実施し、その後高温化学蒸着を実施する。

(もっと読む)

配線剥離防止構造を有する半導体集積回路

【課題】 半導体集積回路のチップ面積を増大させることなく、配線層の剥離防止構造を作製し、チップへの応力による配線の切断を防止する。

【解決手段】

多層配線構造の半導体集積回路チップ周辺部の金属配線層202〜205上に、当該金属配線層同士を接続するためのスルーホール、或いは最下層の金属配線層と基板上に形成された素子とを電気的に接続するためのコンタクトホールを、夫々、当該金属配線層の直上にスルーホールが形成される領域101と、当該金属配線層の直下にスルーホール或いはコンタクトホールが形成される領域102とが基板面内で重なり合わないように、金属配線層上に複数、集中して配置する。

(もっと読む)

基板を含む半導体ウェハの一部分内にビアを形成するための方法および基板を含む半導体ウェハの一部分内に形成されるビア構造体

【課題】 貫通ビアを形成するための方法および装置を提供する。

【解決手段】 たとえば、基板を含む半導体ウェハの一部分内にビアを形成するための方法である。この方法は、基板の第1の部分が基板の第2の部分から分離されるように第1の部分を取り囲むトレンチを形成するステップと、第1の部分内で基板を貫通する穴を形成するステップと、穴の内部に第1の金属を形成するステップとを含む。トレンチは基板を貫通して延びる。第1の金属は基板の表面から基板の裏面に延びる。ビアは穴と第1の金属とを含む。

(もっと読む)

半導体装置

【課題】高価な露光装置や高価なマスクを用いることなく、配線等のピッチを狭くすることができる半導体装置を提供する。

【解決手段】第1の導電パターン42と、第1の導電パターンに隣接して形成された第2の導電パターン42と、第1の導電パターンの所定領域下に形成された第1の導体プラグと、第1の導電パターンの所定領域上に形成された第2の導体プラグ62nと、第2の導電パターンのうちの、第1の導電パターンの所定領域に隣接する所定領域下に形成された第3の導体プラグと、第2の導電パターンの所定領域上に形成された第4の導体プラグ62n+1と、第1の導電パターン42の上方に形成され、第2の導体プラグに接続された第3の導電パターン62と、第2の導電パターンの上方に形成され、第4の導体プラグに接続された第4の導電パターン64とを有し、第4の導体プラグは、第2の導体プラグに対して、ずれた位置に配されている。

(もっと読む)

661 - 680 / 2,805

[ Back to top ]