Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

641 - 660 / 2,805

半導体装置及びその製造方法

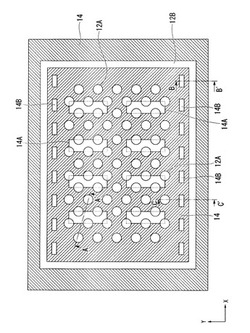

【課題】キャパシタの下部電極のダメージを抑制することができる半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置は、立設する複数の電極と、前記電極の立設を保持する第1の絶縁膜と、前記電極が貫通するように前記第1の絶縁膜に形成され、各々の前記電極の外周側面の少なくとも一部に接触する複数の孔部と、前記第1の絶縁膜に形成され、前記複数の孔部のうちその一部の孔部に連結する第1の開口と、前記第1の絶縁膜に形成され、前記複数の孔部のいずれの孔部に対してよりも前記溝部に近接する位置に配置すると共に前記複数の孔部のいずれにも連結しない第2の開口とを、備えたことを特徴とすることを特徴とする。

(もっと読む)

半導体装置の製造方法

【目的】キャップ成膜時に起因するlow−k膜の絶縁性劣化を低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に絶縁材料を用いたキャップ膜を形成する工程(S106)と、前記キャップ膜を形成した後に、前記キャップ膜を介して前記前記キャップ膜の下層のシリル化処理を行なう工程(S108)と、前記シリル化処理の後、エッチング法を用いて、前記キャップ膜上から前記絶縁膜内へと続く開口部を形成する工程(S114)と、前記開口部に導電性材料を堆積させる工程(S124)と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

アモルファスなタンタル−イリジウム拡散バリアを用いた銅相互接続構造、その形成方法、および該方法による半導体デバイス製造方法

【課題】ライナ/銅界面のボイド生成部位の排除により、高い信頼性および生産歩留まりが得られる半導体デバイス製造方法を提供する。

【解決手段】半導体デバイス製造に用いる拡散バリアを形成する方法は、物理蒸着(PVD)工程によって、パターン形成された中間誘電体(ILD)層の上に、イリジウム・ドープされたタンタル・ベースのバリア層を堆積するステップを含み、該バリア層は、原子量で少なくとも60%のイリジウム濃度で、バリア層が結果としてアモルファス構造を有するように堆積される。

(もっと読む)

配線を形成する方法及びプラズマスパッタリアクタ

【課題】アスペクト比の高いホール内に、被覆性の良好な、コンタクト抵抗の低いバリア層を形成する半導体装置の製造方法を提供する。

【解決手段】タンタルまたはタンタルナイトライド等のライナー材料をホール内にスパッタ堆積する。ロングスロースパッタリング、自己イオン化プラズマ(SIP)スパッタリング、誘導結合プラズマ(ICP)再スパッタリング及びコイルスパッタリングを1つのチャンバ内で組み合わせたリアクタ150を使う。ロングスローSIPスパッタリングは、ホール被覆を促進する。ICP再スパッタリングは、ホール底部のライナー膜の厚さを低減して、第1のメタル層との接触抵抗を低減する。ICPコイルスパッタリングは、ICP再スパッタリングの間、再スパッタリングによる薄膜化は好ましくないホール開口部に隣接しているような領域上に、保護層を堆積する。

(もっと読む)

半導体装置及びその製造方法

【課題】自己整合的にバリア膜を形成する配線構造の信頼性を向上できるようにする。

【解決手段】半導体基板の上に酸素及び炭素を含む層間絶縁膜11を形成し、該層間絶縁膜11に溝部13を形成し、溝部13の底面上及び側壁上に所定の第1の金属元素及び第2の金属元素を含む補助膜14を形成し、熱処理を行い、銅を主成分とする配線本体層19を、溝部13の内部を埋め込むように形成する。熱処理を行うことにより、補助膜14中の第1の金属元素を補助膜14と対向する層間絶縁膜11に拡散させ、溝部13の底面及び側壁における層間絶縁膜11の上において、第1の金属元素と層間絶縁膜11の酸素元素との化合物を主成分とする第1のバリア膜15を形成させた後、補助膜14中の第2の金属元素が補助膜14と対向する層間絶縁膜11に拡散させ、第2の金属元素と層間絶縁膜11の炭素元素との化合物を主成分とする第2のバリア膜17を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】新たな工程を追加することなく信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体素子を表面側に有する基板11と、半導体素子を覆うように基板11に積層された第1絶縁膜12と、第1絶縁膜12を厚さ方向に貫通する貫通孔の内面に積層されたバリア導電層13を介して貫通孔内に埋め込まれたコンタクトプラグ14と、第1絶縁膜12の表面に形成されてコンタクトプラグ14を介して半導体素子と電気的に接続された1種類以上の機能層とを備え、前記機能層は、バリア導電層13の材料と同じ材料からなり第1絶縁膜12の表面の所定領域に積層された第1バリア導電層13と、第1バリア導電層13上に、直接積層されるか、または第2絶縁膜15を介して積層されるか、またはそれらの両方の形態で積層された第2バリア導電層16と、第2バリア導電層16に積層された導電層17とを有してなることを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高い半導体装置を実現する構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板(半導体基板1)上に、シラン化合物およびポロジェンを含む膜(有機シリコンポリマー膜2)を設ける工程と、選択的エッチングにより有機シリコンポリマー膜2に孔(配線溝3)を設けるとともに、配線溝3の内部に金属膜(バリア膜4および銅配線5)を設ける工程と、還元ガス雰囲気中で、上記ポロジェンの沸点または分解温度以上の温度で加熱しつつ、有機シリコンポリマー膜2に紫外線6を照射して、多孔質膜7を得る工程と、を含むものである。

(もっと読む)

半導体装置の製造方法

【課題】付加的な洗浄工程を追加することなくバリア膜の洗浄を行なうことができ、生産コストの上昇が抑えられる半導体装置の製造方法を提供する。

【解決手段】Low−k膜の開口部に、バリア膜を介在させて銅めっき膜が形成される。次に、バリア膜のルテニウムを除去するための所定の洗浄処理が施される。このとき、半導体基板の裏面に、塩酸と過酸化水素水とをそれぞれ所定時間吐出させる。次に、所定の時間待機することにより、塩酸と過酸化水素水とを反応させる。次に、反応した薬液を、半導体基板を回転させることによってその裏面に均一に広げる。この一連のステップを1サイクルとして、これを少なくとも1回、必要に応じて2回以上繰り返す。塩酸と過酸化水素水とが反応してより濃度の高い塩素イオンが発生することにより、ルテニウムが溶解して除去される。

(もっと読む)

半導体装置及びその製造方法

【課題】電極パッドの損傷を抑制することができる半導体装置を提供する。

【解決手段】半導体基板11と、半導体基板11の上方に形成された電極パッド30とを有し、電極パッド30は、第1の融点温度を有する材料からなる第1の層32と、第1の層32上に位置するとともに外に向けて表出し、第1の融点温度よりも高い第2の融点温度を有する材料からなる第2の層33とを含むことを特徴とする。これにより、外部から電極パッド30への圧力により第1の層32に達する傷ができても、必要に応じて第1の融点以上の温度で加熱することにより電極パッド表面の平坦性を修復することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に素子と貫通電極とが形成された半導体装置の製造方法において、貫通電極からの銅による素子の汚染を防止できる方法を提供する。

【解決手段】半導体基板10と、それに形成された素子ZDと、半導体基板10を貫通するスルーホールTHと、半導体基板10の両面側及びスルーホールTHの内面に形成されて、素子ZDを被覆する絶縁層12とを備えた構造体を用意する工程と、スルーホールTH内に貫通電極20を形成する工程と、貫通電極20を被覆する第1バリア金属層30aを形成する工程と、素子ZDの接続部に到達するコンタクトホールCH1を形成する工程と、コンタクトホールCH1内の素子ZDの接続部の自然酸化膜を除去する工程と、第1バリア金属層30aを利用して、貫通電極20に接続される第1配線層40と、コンタクトホールCH1を通して素子ZDの接続部に接続される第2配線層40aとを形成する工程とを含む。

(もっと読む)

貫通シリコンビアを有するめっき物及びその形成方法

【課題】貫通シリコンビア形成時におけるビア内側壁の銅シード層のカバレッジが良好で均一な銅配線層を有するめっき物を提供することを目的とする。

【解決手段】基材上にバリア層として形成された、タングステン及びタングステンと合金化した際に銅に対するバリア性を有する金属(A)との合金薄膜、その上に無電解置換銅めっきにより銅シード層、さらに前記無電解置換銅めっきを実施したのと同一のめっき液を用いた電気銅めっきにより銅配線層がこの順番で形成されてなる、貫通シリコンビアを有するめっき物。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バリアメタルの被覆性を向上させる。

【解決手段】本発明の半導体装置は、キャップ絶縁膜1d上に形成された絶縁膜と、絶縁膜に形成された配線溝と、配線溝の底面に形成されたビア孔と、少なくともビア孔の側壁を覆うバリアメタル膜と、を有する。ビア孔は、径が異なる複数の孔から構成されており、複数の孔は、下に向けて径が小さくなるように深さ方向に接続し、複数の孔の接続部にキャップ絶縁膜に対してほぼ平行な面を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 炭化珪素の半導体装置において、電極材料と、内部配線の材料とが異なるとき、これら異種金属の接触界面における不具合のおそれを無くして、長期間使用後にも高い信頼性を得ることができる、半導体装置等を提供する。

【解決手段】 炭化珪素14,18に接触する接触電極16と、該接触電極と導通する配線19とを備え、接触電極16が、チタン、アルミニウム、および珪素を含有する合金で形成され、配線19は、アルミニウムまたはアルミニウム合金で形成され、該配線は接触電極と接触することで該接触電極と導通をとることを特徴とする。

(もっと読む)

フレキシブル半導体デバイスを高温で提供する方法およびそのフレキシブル半導体デバイス

いくつかの実施例は、半導体デバイスを提供する方法を含む。当該方法は、

(a)フレキシブル基板を提供する段階、(b)フレキシブル基板上に少なくとも1つの材料層を堆積させる段階であって、そのフレキシブル基板上の少なくとも1つの材料層の堆積は、少なくとも180℃の温度で生じる、段階、および(c)金属層とa−Si層との間に拡散バリアを提供する段階を含む。他の実施例も本願において開示される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】パワーMOSFETにおいては、アルミニウム系ソース電極下のアルミニウム拡散バリア・メタル膜として、チタンおよび窒化チタンからなるチタン系バリア・メタル膜が広く使用されている。しかし、本願発明者らが検討したところによると、チタン系バリア・メタル膜を使用すると、ウエハの反りが増大して、ウエハ・ハンドリングが困難となり、ウエハ割れやウエハ欠け等の問題が不可避となることが明らかとなった。この傾向は、最小寸法が0.35マクロ・メートル以下の製品において特に顕著である。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜(TiW等のタングステンを主要な成分とする合金膜)をスパッタリング成膜によって形成する際、スパッタリング成膜チャンバの気圧を1.2パスカル以下とするものである。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の埋め込み不良及び配線抵抗の上昇を抑えると共に、信頼性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、基板101の上に形成された絶縁膜105と、絶縁膜105中に形成された、銅を含む材料からなる埋め込み配線115とを備えている。絶縁膜105と埋め込み配線115との間には、白金族元素を含む材料からなるバリア膜110が形成されている。絶縁膜105とバリア膜110との間には、絶縁膜105よりも密度が高い高密度絶縁膜109が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成に際して、半導体基板の表面の上方に設ける第1の突起電極が製造工程中に脱落することを防止する手段を提供する。

【解決手段】基板1、1aの第1の面側に金属シード膜7、7aを設けた状態で、基板の第1の面側の全面に接着層及び支持基板を設ける。基板の第1の面上に設けた接着層及び支持基板を除去した後に、金属シード膜の露出した部分を除去する。この後、複数の半導体チップS1、S2を積そうして、第1のリフローを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部からの水分がパッド上の開口部に浸入した場合でも、開口部の側面に露出している窒化チタン膜が酸化チタン膜に変化することを抑制することができ、半導体装置の信頼性を向上できる技術を提供する。また、パッドの表面保護膜にクラックが発生することを抑制し、半導体装置の信頼性を向上できる技術を提供する。

【解決手段】開口部OP2の径を開口部OP1の径よりも小さくし、かつ、開口部OP2を開口部OP1に内包されるように形成する。これにより、開口部OP1の側面に露出する反射防止膜ARの側面を、開口部OP2を形成している表面保護膜PAS2で覆うことができる。この結果、反射防止膜ARの側面を露出することなく、パッドPDを形成することができる。

(もっと読む)

641 - 660 / 2,805

[ Back to top ]