Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

601 - 620 / 2,805

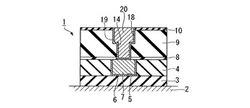

半導体装置の製造方法

【課題】露光によるフォトレジスト膜のパターニングに際し、下地層からの反射光を抑制することができ、かつ、製造コストが抑えられる半導体装置の製造方法を提供する。

【解決手段】半導体基板2上の第1層間絶縁膜3に第1導電層7を形成する工程と、第1導電層7上にストッパー膜8を形成する工程と、ストッパー膜8上にビアホール14が形成された第2層間絶縁膜9を形成する工程と、染料が含有されているフォトレジスト膜を、前記ビアホール内に埋め込むとともに、第2層間絶縁膜9上に形成する工程と、フォトレジスト膜に配線パターンを形成する工程と、配線パターンが形成されたフォトレジスト膜をマスクとして、第2層間絶縁膜9をエッチングして、第2溝部18を形成する工程と、ビアホール14内及び第2溝部18内に第2導電層20を形成する工程と、を備えることを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法においてSRAMのセルサイズを縮小することを目的とする。

【解決手段】メモリセルCの活性領域31a、31bが画定されたシリコン基板31と、素子分離絶縁膜32上に形成され、第1の方向に延在するゲート電極35と、シリコン基板31とゲート電極35の上に形成された第1の絶縁膜42と、第1の絶縁膜42を貫通し、ゲート電極35と第1の活性領域31aに重なり、第1の方向に直交する第2の方向に延在する第1の銅プラグ45aと、第2の活性領域35b上の第1の絶縁膜42を貫通する第2の銅プラグ45bと、第1の絶縁膜42上に形成された第2の絶縁膜44と、第2の絶縁膜44に埋め込まれ、第1の銅プラグ45aの側面45xから第2の延在方向に後退して形成され、第1の銅プラグ45aの上面の一部のみを覆う銅配線48aとを有する半導体装置による。

(もっと読む)

半導体装置の製造方法

【課題】銅を用いた多層配線を有する半導体装置を高性能化する。

【解決手段】シリコン基板上に第1配線層用絶縁膜Z1を形成し、第1配線層用絶縁膜Z1に第1配線用孔部H1を形成する。その後、第1配線用孔部H1の側壁および底面を覆うようにして、タンタルまたはチタンを含む下部バリア導体膜eb1と、ルテニウムを主体とする上部バリア導体膜et1とからなる第1配線用バリア導体膜EM1を形成する。続いて、上部バリア導体膜et1をシード層として、電気めっき法により、銅を主体とする第1配線用導体膜EC1を形成し、CMP法により第1配線用導体膜EC1を第1配線用孔部H1に埋め込む。特に、上部バリア導体膜et1として、1〜5%の濃度で炭素を含ませるようにして、ルテニウムを主体とする導体膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、シリサイドを構成する金属のサイドウォールの直下への潜り込みの影響を低減する。

【解決手段】 シリコン基板上にゲート電極を形成する工程と、ゲート電極の側壁に、第1絶縁膜による第1サイドウォールと、第1サイドウォール上にあって、第1絶縁膜とはエッチング特性の異なる第2絶縁膜による第2サイドウォールを形成する工程と、シリコン基板および第2サイドウォールを含む表面に金属をスパッタリングにより堆積させ、金属の一部をシリコン基板に侵入させる工程と、シリコン基板上に堆積した金属を除去する工程と、金属の除去工程の後に熱処理を行って、スパッタリングによってシリコン基板に侵入した金属とシリコン基板中のシリコン原子とを反応させてシリサイド層を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】多層配線を有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1上に第1配線用絶縁膜IM1を形成し、第1配線用絶縁膜IM1に配線溝TM1を形成する。その後、配線溝TM1に銅を主体とする導体膜を埋め込むことで配線MW1を形成する。続いて、配線MW1上にキャップ導体膜MC1を形成した後、キャップ導体膜MC1に表面研磨を施す。特に、キャップ導体膜MC1はALD法によって配線MW1上に選択的に形成する。

(もっと読む)

ビアがガウジングされた相互接続構造体及びその製造方法

【課題】 ビア開口部の底部にガウジング構造部を含む相互接続構造体、及びその形成方法を提供する。

【解決手段】 本発明の方法は、ビア開口部の上に配置されるライン開口部内の堆積されたトレンチ拡散バリアの被覆率に影響を与えず、及び/又は、ビア開口部及びライン開口部を含む相互接続誘電体材料内にスパッタリングを行なうことによりビア開口部の底部にガウジング構造部を生成することに起因する損傷を生じさせない。こうした相互接続構造体は、最初に相互接続誘電体内にライン開口部を形成し、その後、ビア開口部、次いでガウジング構造部を形成することによって、ビア開口部の底部内にガウジング構造部を提供することにより達成される。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上にトランジスタ34を形成する工程と、半導体基板上及びトランジスタ上に複数の部分膜36a、38a、40a、42を積層することにより、複数の部分膜を有する第1の絶縁層44を形成する工程と、第1の絶縁層上に、第1の絶縁層とエッチング特性が異なる第2の絶縁層46を形成する工程と、第1の絶縁層をエッチングストッパとして、第2の絶縁層をエッチングすることにより、第2の絶縁層にコンタクトホールを形成する工程と、コンタクトホール内に露出する第1の絶縁層をエッチングする工程とを有し、第1の絶縁層を形成する工程では、複数の部分膜のうちの最上層の部分膜以外の部分膜に対して膜を収縮させるキュア処理を行い、複数の部分膜のうちの最上層の部分膜に対してキュア処理を行わない。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

層間絶縁膜および配線構造と、それらの製造方法

【課題】 低誘電率で且つCFx、SiF4等のガスの発生がなく安定な半導体装置の層間絶縁膜とそれを備えた配線構造を提供する。

【解決手段】 下地層上に形成された絶縁膜を備えた層間絶縁膜において、前記層間絶縁膜は、実効誘電率が3以下である。配線構造は、層間絶縁膜と、層間絶縁膜に形成されたコンタクトホールと、前記コンタクトホール内に充填された金属とを備え、前記絶縁膜は、前記下地層上に形成され、表面が窒化されたフルオロカーボン膜を備えている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】複数の容量部が接続された容量プレート上面とロジック部とで配線層の高さを同じにするメモリ混載の半導体装置、および製造方法を提供する。

【解決手段】半導体装置の製造方法は、ロジック部の第1領域3の第1層間層43、53に配線34を形成する工程と、配線形成後にメモリ部の第2領域2の第1層間層43、53における表面領域をエッチングする工程と、エッチングした領域に容量12用の複数のシリンダ開口部を形成する工程と、複数のシリンダ開口部に下部電極層12C、誘電体層12B及び共通上部電極12A、13を形成して、複数の容量部12を形成する工程とを具備する。複数の容量部12を形成する工程は、第1層間層43、53の上面と共通上部電極12A、13の上面とが略同一平面上になるように共通上部電極12A、13を形成する工程を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】エロージョンの発生及び研磨残渣の発生がない金属からなる配線又はプラグを形成できるようにする。

【解決手段】半導体基板1上の層間絶縁膜3にコンタクトホール3aを形成する。続いて、層間絶縁膜3上に金属を含む化合物及び第1の還元性ガスを供給することにより、コンタクトホール3aを含む層間絶縁膜3の上に第1のシード層5を形成する。続いて、第1のシード層5上に金属を含む化合物及び第2の還元性ガスを供給することにより、第1のシード層5の上に第2のシード層6を形成する。続いて、第2のシード層6の上に、金属をコンタクトホール3aを埋め込むように形成する。続いて、CMP法により、層間絶縁膜3のコンタクトホール3aを除く上面に残存する金属、第2のシード層6及び第1のシード層5を除去することにより、コンタクトホール3aにプラグ7Aを形成する。

(もっと読む)

半導体装置

【課題】下層導電層の表面を十分保護することができ、信頼性が高く、配線容量が小さなデュアルダマシン配線を有する半導体装置の製造方法を提供する。

【解決手段】導電性領域11を有する下地と10、下地の表面を覆う絶縁性エッチストッパ膜12と、絶縁性エッチストッパ膜上に形成された層間絶縁膜と、層間絶縁膜表面から第1の深さで形成された配線用溝と、配線用溝底面から導電性領域に達する接続用孔と、配線用溝および接続用孔を埋め込んで形成されたデュアルダマシン配線である。層間絶縁膜が配線用溝の側面および底面を包む第1種の絶縁層15と、第1種の絶縁層よりも下に配置され、第1種の絶縁層とエッチング特性の異なる第2種の絶縁層56とを含む。接続用孔は、断面で見た時に第1種の絶縁層内で傾斜し、上方に向かって次第に開口が増大する部分を有する。

(もっと読む)

半導体装置、電子部品、半導体装置の製造方法

【課題】貫通電極の電気特性を効率よく検査する。

【解決手段】本発明の半導体装置2の製造方法は、シリコン基板20に半導体素子を含んだ電気回路を形成する工程と、シリコン基板20を貫通して設けられ、電気回路と電気的に接続される第1貫通電極22を形成する工程と、シリコン基板20を貫通して設けられ、シリコン基板20の表面20aで第1貫通電極22と短絡する第2貫通電極23を形成する工程と、シリコン基板20の裏面20bにおいて、第1貫通電極22と第2貫通電極23との間の電気特性を検査する工程と、を有する。

(もっと読む)

半導体装置

【課題】パッドに荷重がかかった場合でも、層間絶縁膜の膜剥がれやパッドの剥離の発生率を低くする。

【解決手段】ボンディングパッド72を含む半導体装置100において、ボンディングパッド72と平面視で重なる領域(94)に下部多層配線構造90、中間ビア用層間絶縁膜48、上部多層配線構造92をこの順で積層し、パッド配置領域94において、上部多層配線構造92の上部配線およびビアは、ボンディングパッド72と接続して形成し、中間ビア用層間絶縁膜48には、上部多層配線構造92の配線またはビアと下部多層配線構造90の配線またはビアとを接続する導電材料が形成されず、下部多層配線構造90に含まれるビア用層間絶縁膜中のビアが占める面積率が、上部多層配線構造92に含まれるビア用層間絶縁膜中のビアが占める面積率よりも小さい。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 絶縁膜に設けた凹部の側壁にシール絶縁膜を形成し、シール絶縁膜の内側に順にシール絶縁膜との密着性が優れている第1の導電性バリア層、Cu拡散阻止能力が高い第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設ける。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高いドレインコンタクトを有する半導体装置の製造方法を提供する。

【解決手段】第1ドレインコンタクト14を形成する工程と、第1ドレインコンタクト14に接続された第2ドレインコンタクト15を形成する工程と、第2ドレインコンタクト15に接続された配線16を形成する工程と、配線16をマスクとして自己整合的に、少なくとも第2ドレインコンタクト15の近傍の第2層間絶縁膜33に、第1層間絶縁膜13と第2層間絶縁膜33との界面34より深い位置まで不純物イオンを注入し、界面34に残置されている異物32をアモルファス化する工程と、不純物イオンが注入された第1および第2層間絶縁膜13、33をエッチングして異物32を露出させ、異物32を除去する工程と、第1絶縁膜13上に配線16を覆うように第3層間絶縁膜36を形成する工程と、を具備する。

(もっと読む)

配線形成方法、半導体装置及び回路基板

【課題】 半導体装置や回路基板の配線において、バリア膜の拡散バリアとしての機能を確保しながら、バリア膜による配線抵抗の増大を抑制する

【解決手段】 インプリント法に用いるスタンパ13のパターン面をバリア膜形成化合物14で被覆し、スタンパ13のパターン面を、基板11上に塗布された樹脂膜12に押し当てつつ、バリア膜形成化合物14の分解・転写処理を行う。これにより、スタンパ13のパターン面のパターンにより樹脂膜12内に配線溝16が形成され、配線溝16に沿ってバリア膜17が形成される。その後、配線溝16内にバリア膜17を介して配線材料を埋め込み、配線18を形成する。

(もっと読む)

半導体デバイスのための電力グリッド構造体及びその製造方法

【課題】 半導体デバイスに電力を提供する電力グリッド構造体及びその製造方法を提供する。

【解決手段】 本発明の一実施形態は、誘電体層の内部に形成された第1の導電性材料のスタッドと、底部及び側壁を有する第2の導電性材料のビアであって、底部及び側壁は導電性ライナで覆われ、底部はスタッドの直接上に形成され、かつ、導電性ライナを通してビアと接触した状態にある、ビアと、ビアの側壁において導電性ライナを通してビアに接続する第3の導電性材料の1つ又は複数の導電性パスとを含むことができる半導体構造体を提供する。半導体構造体を製造する方法も提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置において貫通電極の信頼性を向上させることができる半導体装置を提供する。

【解決手段】シリコン基板10の第1主面上に形成された絶縁膜25と、第1主面上の絶縁膜25内に形成され、導電膜からなりその導電膜の少なくとも1部に導電膜が存在しない空き領域を有する電極パッド26Bと、第1主面に対向する第2主面上に形成されたハンダボール18と、シリコン基板10の第2主面側から空けられ電極パッド26Bまで達した貫通孔内に形成され、電極パッド26Bとハンダボール18とを電気的に接続する貫通電極とを備える。電極パッド26Bが有する空き領域には絶縁膜25が存在し、空き領域に存在する絶縁膜25と電極パッド26Bとの貫通電極側の段差が電極パッド26Bの厚さ以下である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線絶縁膜としてSiOCH膜を用いる場合に、ビアホールの開口径に依らず、その加工制御性を十分に得て、下層Cu配線の表面の組成のバラツキを十分に抑制する。

【解決手段】下層Cu配線3上に形成されている積層構造20は、シリコンと炭素を含有するキャップ絶縁膜4と、キャップ絶縁膜4上に形成されている配線絶縁膜5としてのSiOCH膜を有する。積層構造20にビアホール8、9を形成する工程は、第1及び第2ドライエッチングを組み合わせて行う。第1ドライエッチングでは開口径が小さいビアホール9のエッチングレートが、開口径が大きいビアホール8のエッチングレートよりも大きくなるようにO2濃度が設定された第1混合ガスを用いる。第2ドライエッチングではビアホール8のエッチングレートがビアホール9のエッチングレートよりも大きくなるようにO2濃度が設定された第2混合ガスを用いる。

(もっと読む)

601 - 620 / 2,805

[ Back to top ]