Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

541 - 560 / 2,805

電子モジュールの製造方法、および、電子モジュール

半導体基板に集積された回路と、基板と、ヒートシンクとしての支持体と、基板および支持体をはんだ付けにより接続する熱伝導性接続部とを備えた電子モジュールを提案する。ここでは、基板で用いられる後面金属化部として、まず第1の厚いAu層(23)、ついでバリア層(24)、最後に第2の薄いAu層(25)が堆積される。バリア層の材料は、はんだ付け過程において、第2のAu層の領域のAuSn液相のSnないしAuSnが第1のAu層(23)へ浸入することを阻止するように選定される。また、基板の貫通孔にも、後面金属化部の積層体が堆積される。ここで、第2のAu層の表面は、バリア層から拡散する材料によって、はんだ付け材料に対する低減された濡れ性を有する。  (もっと読む)

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

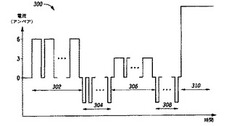

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

電極コンタクト構造、自己走査型発光素子アレイ

【課題】オーミック接触を実現する電極コンタクト構造を提供する。

【解決手段】電極コンタクト構造は、エピタキシャル層100と、エピタキシャル層100上に形成されたコンタクトメタル電極120と、コンタクトホールを有する層間絶縁膜140と、コンタクトメタル電極120上に形成された第1のAl配線160と、第1のAl配線160上に形成された拡散障壁層180と、拡散障壁層180上に形成された第2のAl配線200を有する。電極コンタクト構造は、自己走査型発光素子アレイのカソード電極やゲート電極の構造として用いられる。

(もっと読む)

Cu配線の形成方法

【課題】配線形成後に500℃以上の高温プロセスが存在する場合に適用可能なCu配線を形成すること。

【解決手段】500℃以上の温度の処理をともなう後工程が施されるCu配線の形成方法は、表面にトレンチおよび/またはホールを有する基板上の少なくともトレンチおよび/またはホールの底面と側面に、Cuの格子面間隔との差が10%以内の格子面間隔を有する金属からなる密着膜を形成する工程と、密着膜の上に前記トレンチおよび/またはホールを埋めるようにCu膜を形成する工程と、 Cu膜形成後の基板に350℃以上のアニール処理を行う工程と、Cu膜を研磨してCu膜のトレンチおよび/またはホールに対応する部分のみを残存させる工程と、研磨後のCu膜にキャップを形成してCu配線とする工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】保護膜の亀裂や膜剥がれを防止する。

【解決手段】化合物半導体基板1上に少なくとも一層からなる下層配線2を形成し、化合物半導体基板1上に有機材料からなる層間膜3を堆積し、層間膜3上に金からなる上層配線5を形成し、層間膜3中に下層配線2と上層配線5とを接続するヴィア4を形成し、上層配線5の表面および層間膜3の表面の上にシリコン窒化膜からなる密着性向上用膜6を形成し、密着性向上用膜6上にシリコン酸化膜からなる熱膨張抑制膜7を形成し、熱膨張抑制膜7上にシリコン窒化膜からなる保護膜8を形成する。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

電極コンタクト構造、自己走査型発光素子アレイ

【課題】不均一な結晶相の形成を抑制してオーミック接触を実現する電極コンタクト構造を提供する。

【解決手段】電極コンタクト構造は、エピタキシャル層100と、エピタキシャル層100上に形成されたコンタクトメタル電極120と、コンタクトホールを有する層間絶縁膜140と、コンタクトメタル電極120上に形成され、コンタクトメタル電極の結晶配向性と整合する結晶配向性を有する拡散障壁層200と、拡散障壁層200上に形成されたAl配線160を有する。電極コンタクト構造は、自己走査型発光素子アレイのカソード電極やゲート電極の構造として用いられる。

(もっと読む)

半導体基板の製造方法

【課題】半導体基板が厚い場合においても貫通電極を高生産性、高品質で低コストで実現できる半導体基板の製造方法を提供することを目的とする。

【解決手段】半導体基板(101)にアクティブ面が露出する開口部(104)を有する電極パッド(102)を形成し、開口部(104)からアクティブ面の反対側の面に向かって凹部(105a)を形成し、凹部(105a)の内側に絶縁膜(106)を形成し、絶縁膜(106)と電極パッド(102)の表面に導電経路(107)を形成し、アクティブ面の反対側の面から半導体基板(101)を薄型化して凹部(105a)の底部を貫通させる。

(もっと読む)

半導体装置

【課題】スルーホールの深さを正確に制御して、特定の配線層に選択的にエアギャップを形成した半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体素子を有する半導体基板1と、半導体基板1の上方に形成され、配線10a、10b、10c、10d、配線10c、10dの周囲のエアギャップ101、およびエアギャップ101に連続するスルーホール102含む配線構造と、スルーホール102下に形成されたスルーホールストッパー103と、を有する。

(もっと読む)

回路基板

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体基板上の回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む半導体基板1の一部表面が露出するようメタルマスク100を半導体基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、半導体基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、半導体基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

ハイブリッド誘電体を備えた高信頼低誘電率相互接続構造

【課題】ハイブリッド誘電体を有する拡張型バック・エンド・オブ・ライン(BEOL)相互接続構造を提供すること。

【解決手段】ビア・レベルでの層間誘電体(ILD)は、ライン・レベルでのILDとは異なることが好ましい。好ましい実施形態では、ビア・レベルのILDを低k SiCOH材料で形成し、ライン・レベルのILDを低kポリマー熱硬化性材料で形成する。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】薄膜であっても銅(Cu)原子の金属シリサイド膜などへの拡散を充分に安定して抑止でき、尚且つ、小さな接触抵抗をもたらす比抵抗の小さな銅(Cu)からコンタクトプラグを形成できるようにする。

【解決手段】 本発明のコンタクトプラグ100は、半導体装置の絶縁膜104に設けられたコンタクトホール105に形成され、コンタクトホール105の底部に形成された金属シリサイド膜103と、コンタクトホール105内で金属シリサイド膜103上に形成された酸化マンガン膜106と、酸化マンガン膜106上に、コンタクトホール105を埋め込むように形成された銅プラグ層107と、を備え、酸化マンガン膜は非晶質からなる膜である、ことを特徴としている。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスク膜による焦点深度のマージンの低下及びアライメントマークの視認性の低下を防ぎ、且つ、セルフアラインドビアの形成を可能とすることにより、配線同士のショートによる歩留まりの低下を防止すると共に、配線同士の絶縁性を高め、その信頼性を向上させるようにする。

【解決手段】半導体装置の製造方法は、基板10の上に、少なくとも1層の絶縁膜を含む層間絶縁膜12を形成し、層間絶縁膜12の上部に第1のマスク膜16を埋め込むように形成し、層間絶縁膜12及び第1のマスク膜16の上に第2のマスク膜17を形成し、第2のマスク膜17を用いて、層間絶縁膜12にビアホール19を形成し、第1のマスク膜16を用いて、層間絶縁膜12に配線溝20を形成し、ビアホール19及び配線溝20に導電性材料を埋め込むことにより、ビア及び配線を形成する。

(もっと読む)

半導体装置

【課題】一定の静電容量を確保すると同時に、小型化を図ることが可能なキャパシタを備える半導体装置を提供する。

【解決手段】半導体装置は、金属膜を含むキャパシタ下部電極3aと、キャパシタ下部電極3aの上部表面上に配置され、キャパシタ下部電極3aの厚みより薄い厚みを有する誘電体膜4aと、誘電体膜4a上に配置され、金属膜を含むキャパシタ上部電極6aと、キャパシタ上部電極6aと同一レベルの層により構成される下部配線部分6bと、下部配線部分6b上に配置される層間絶縁膜8と、層間絶縁膜8上に配置される上部配線部分12bとを備える。

(もっと読む)

半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

(もっと読む)

欠陥検査パターン回路、半導体ウェーハ及び欠陥検査方法

【課題】欠陥検査パターン回路に関し、p側コンタクト及びn側コンタクトのいずれのコンタクト不良も検出可能にする。

【解決手段】p型半導体基板1と、少なくとも2つのp型ウエル領域2,4と、少なくとも1つのn型ウエル領域3と、p型ウエル領域の一つに設けた第1のp+型活性領域6と、他のp型ウエル領域4に設けたn+型活性領域8と、n型ウエル領域3に設けた第2のp+型活性領域7と、第1のp+型活性領域6に設けたコンタクトプラグ10と、n+型活性領域8及び第2のp+型活性領域7に設けた各一対のコンタクトプラグ12,13と、各コンタクトプラグを、第1のp+型活性領域6に設けたコンタクトプラグ10から順に上下互いに接続してコンタクトチェーンを形成する配線15,16,17とを有する欠陥検査パターン回路におけるn型ウエル領域3の体積を第1のp+型活性領域6を形成したp型ウエル領域2の体積より小さくする。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】本発明の半導体素子の形成方法は、基板上に半導体構造物及び絶縁パターンを形成し、絶縁パターンの一面によって定義される側壁と半導体構造物の底によって定義される底を有するオープニングを形成し、オープニングを満たす第1金属膜を形成し、第1金属膜を湿式エッチングしてオープニングの側壁を少なくとも一部露出させ、第1金属膜上に第2金属膜を選択的に形成することを含む。

(もっと読む)

541 - 560 / 2,805

[ Back to top ]