Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

461 - 480 / 2,805

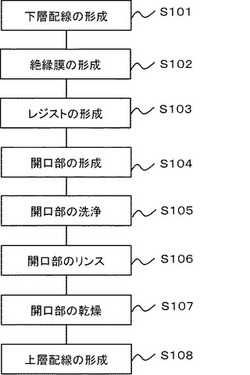

半導体装置の製造方法

【課題】微細配線を有する半導体装置を高信頼性及び高歩留まりで得る。

【解決手段】この半導体装置の製造方法は、下層配線を形成する工程(ステップS101)と、下層配線上に絶縁膜を形成する工程(ステップS102)と、絶縁膜上にレジストを形成する工程(ステップS103)と、レジストをマスクとしてドライエッチングにより下層配線を露出する開口部を形成する工程(ステップS104)と、開口部を洗浄液を用いて洗浄する工程(ステップS105)と、洗浄した開口部をリンスする工程(ステップS106)と、含む。ステップS106では、リンス液と還元性ガスとを二流体ノズルから吐出して、開口部の底部をリンスする。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、炭化シリコン薄膜の機械強度を高め、膜の消失や剥離を防止する。

【解決手段】 ポーラスな誘電率低誘電率絶縁膜上に−CH2−結合が環状になってSiと結合し且つ二重結合を含む官能基を有する原料を用いて炭化シリコン薄膜を形成する工程と、前記炭化シリコン薄膜を所定パターンにエッチングしてハードマスクを形成する工程と、前記ハードマスクをエッチングマスクとして前記低誘電率絶縁膜をエッチングして配線形成用溝或いはビアホールの少なくとも一方を形成する工程とを設ける。

(もっと読む)

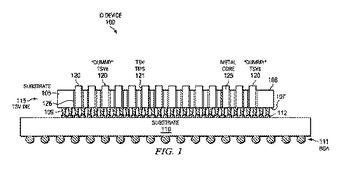

ICデバイスのエンハンストされた熱放散のための突出するTSV

集積回路デバイス(100)が、基板パッド(102)を含む上面を有する基板(110)、及び能動回路を含む上部半導体表面(107)と(底面)106とを含む半導体基板(105)を含む複数の基板貫通ビア(115)ダイを含む。上部半導体表面(107)は、基板の上面上の基板パッドに結合されるボンドコネクタ109を含む。複数の基板貫通ビア(TSV)が、底面から外に延びる突出するTSVティップ(121)に上側半導体表面から延びる内部金属コア(125)を含む。複数のTSVの少なくとも1つが、そこへの如何なる電気的接続もない、突出するTSVティップを有し、TSVダイの底面からの熱消散を可能にするための付加的な表面領域を提供するダミーTSV(120)である。

(もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】第1の領域中の層間絶縁膜を湿式エッチングにより除去する際に、使用する薬液が第2の領域に浸透することを防止する。これにより、第2の領域の特性の劣化がない、高性能の半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた第2の領域と、を有する半導体装置。第1の領域は、導電性を有する第1の膜によって構成された第1の電極を有する。第1の領域中の第1の電極の表面は、第2の膜で覆われていない。ガードリングは、凹状の溝の内壁を覆う第1の膜と、凹状の溝の内部において少なくとも第1の膜の表面の一部を覆う絶縁性の第2の膜を有する。

(もっと読む)

半導体装置製造方法及び積層半導体装置

【課題】複数の基板を貼り合わせる積層半導体装置を効率よく製造できる方法を提供する。

【解決手段】複数の基板を貼り合わせて積層半導体装置を製造する半導体装置製造方法であって、回路が形成された複数の基板のうちの一の基板に凹部を形成する凹部形成ステップと、一の基板を複数の基板のうちの他の基板に重ね合わせる重ね合わせステップと、重ね合わせステップの後に、一の基板の凹部に導電性材料を導入することにより、一の基板の回路と他の基板の回路との間の電気的な導通路を形成する導通形成ステップとを備える半導体装置製造方法が提供される。

(もっと読む)

半導体装置

【課題】電極パッドからの水分の拡散を防止できると共に、絶縁膜の薄膜化及び低誘電率化に対応できるようにする。

【解決手段】半導体装置は、半導体基板11の上方に形成され、外部との電気的な接続を取る接続部25である電極パッドと、半導体基板と接続部との間に積層された絶縁膜14等にそれぞれ形成され、上層の配線34が接続部と接続された複数の第1配線層及び該第1配線層同士を接続するビア31よりなる積層構造体27と、複数の絶縁膜に積層構造体の周囲を隙間なく囲むように形成され、複数の第2配線層40等及び該第2配線層同士を線状に接続するラインビア41よりなるリング構造体28と、接続部と内部回路とを電気的に接続する引き出し配線32Aとを有している。積層構造体とリング構造体とは複数の第1配線層の少なくとも1つによって互いに接続されており、引き出し配線はリング構造体と接続されている。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

ダマシンインターコネクトのエレクトロマイグレーション抵抗を向上させる界面層

【課題】、ダマシンインターコネクトのエレクトロマイグレーション特性を向上させるべく銅線内に保護キャップを形成する方法を提供する。

【解決手段】a)酸化物を含まない銅または銅合金107の露呈領域と誘電体の露呈領域とを含む基板100を、アルミニウムを含む化合物に、少なくとも約摂氏350度の基板温度で曝して、前記誘電体および前記銅または銅合金の層の両方の上にアルミニウムを含む第1の層を形成する工程と、(b)前記第1の層の少なくとも一部を化学的に修正して、アルミニウムを含むパッシベーション層109を形成する工程と、(c)前記パッシベーション層の上に誘電体層111.を堆積させる工程とを備える方法。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体製造装置

【課題】有機シリカ膜を成膜したのちのプラズマ反応室の内壁のクリーニング時間を短縮する。

【解決手段】まずプラズマ反応室内壁をプリコート膜で被覆する(プリコート工程)。次いで基板上に、シリコン炭素組成比(C/Si)が1以上である有機シリカ膜を成長させる(基板処理工程)。次いで、基板を取り出した後、プラズマ反応室内壁に付着した有機シリカ膜とプリコート膜とをプラズマを用いて除去する(クリーニング工程)。プリコート膜としては、基板上に成膜された有機シリカ膜よりも少なくとも炭素含有率が低い有機シリカ膜である高酸素含有プリコート膜を用いる。

(もっと読む)

半導体装置

【課題】デュアルダマシン構造の多層配線構造を有する半導体装置において、コンタクトのストレスマイグレーション耐性を向上させる。

【解決手段】デュアルダマシン構造を有する上層導体パターン47Aは延出部47Bに設けられたビアプラグ47Cを介して下層配線パターン43Aと接続している。この接続部でのストレスマイグレーションによる接続不良を防止するため延出部47Bより先端部の領域に下層配線層のダミーCuパターン43Bとダミービアプラグ47Dで接続する構造を追加する。ストレスマイグレーションは先端部の下層配線層のダミーCuパターン43Bとダミービアプラグ47Dの接続部で発生し、ビアプラグ47Cと下層配線パターン43Aの接続部ではストレスマイグレーションの発生は防止される。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の銅配線の信頼性をTDDB寿命とEM寿命との双方に関して向上させる。

【解決手段】 半導体装置の配線層30は、配線溝が形成された絶縁膜32、35と、配線溝の内面に形成されたバリアメタル層41と、バリアメタル層41を介して配線溝内に形成された銅配線膜43とを有する。バリアメタル層41は、配線溝の内壁面側から順に形成された第1乃至第3のバリアメタル膜41−1、2、3を有する。第2のバリアメタル膜41−2は、第3のバリアメタル膜41−3側の表面部分において、クラスタイオン照射によって形成された、その他の部分より高い密度の緻密層41−2aを有する。第3のバリアメタル膜41−3は、例えばルテニウム等、銅配線膜43との密着性に優れた材料を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線が形成される多孔質絶縁膜がプラズマダメージ等を受けるのを防ぐことにより、高歩留り且つ高信頼性な半導体装置を得られるようにする。

【解決手段】半導体基板の上に、化学気相成長法により、炭素濃度、空孔形成剤濃度及び酸素濃度がそれぞれ異なる複数の領域を有する空孔形成剤含有膜を形成する工程を備えている。この工程は、前駆体、空孔形成剤及び酸化剤を第1の流量で流す第1の期間と、第1の期間の後に、前駆体の流量に対する空孔形成剤の流量を減少させる第2の期間と、第2の期間の後に、前駆体の流量に対する空孔形成剤の流量の減少を停止し、前駆体、空孔形成剤及び酸化剤を第2の流量で流す第3の期間と、第3の期間の後に、前駆体の流量に対する酸化剤の流量を増大させる第4の期間と、第4の期間の後に、前駆体、空孔形成剤及び酸化剤を第3の流量で流す第5の期間とを含む。

(もっと読む)

半導体装置の製造方法

【課題】配線構造を形成する際に、ウェハ面内の配線溝の深さのばらつきを抑え、均一加工を実現する。

【解決手段】高炭素濃度絶縁膜114と、炭素を含まないまたは炭素濃度が低い低炭素濃度絶縁膜116との積層構造にドライエッチングで配線溝を形成する際、CHF系ガスを添加した第1のエッチングガスを用いた第1のエッチング条件で低炭素濃度絶縁膜116に配線溝を形成し、当該配線溝底部に高炭素濃度絶縁膜114を露出させる。第1のエッチング条件の第1のエッチングガス中のCHF系ガスの分圧は、第1のエッチングガスに当該CHF系ガスを添加していない場合の各膜へのエッチングレートを基準として、当該CHF系ガスを添加することにより、高炭素濃度絶縁膜114に対するエッチングレートが低下するとともに、低炭素濃度絶縁膜116に対するエッチングレートを変化させない範囲に設定されている。

(もっと読む)

半導体装置

【課題】本発明は、半導体基板とコンタクト部材との接触抵抗をより低減可能な半導体装置を提供する。

【解決手段】

第1の方向に延在し第1の方向と直交する第2の方向に所定の間隔で設けられた活性領域AAと、前記活性領域AAを分離する素子分離絶縁膜11とが設けられた半導体基板21aと、前記半導体基板21aの主表面上に形成された第2の層間絶縁膜24と、前記第2の層間絶縁膜24内に設けられ、前記半導体基板21a上方の配線と電気的に接続された第1の部分及び、前記第1の部分と接続され、上面視すると前記第1の部分から、はみ出した形状である第2の部分を有するコンタクト部材22とを備え、前記第1の方向における前記第2の部分最大幅は、前記第1の方向における前記第1の部分の幅よりも広く、前記第2の部分は、前記第1の部分を包囲する前記第2の層間絶縁膜24に接触していることを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】磁気素子を備えた半導体装置の製造で、磁気素子のダメージを抑止し、下部電極膜の加工に灰化処理を用いないことで下層に存する導電部材の酸化を防止する。

【解決手段】半導体基板10上で、上部電極膜43上に形成したレジストマスク44で上部電極膜43をエッチングして上部電極43aとし、上部電極43aをマスクとしてMTJ膜42をエッチングしてMTJ42aとし、上部電極43a及びMTJ42aを覆う保護膜45aを形成し、上部電極43a及びMTJ42aを保護膜45aを介して覆うように、保護膜45a上にレジスト46を形成し、レジストマスク46で保護膜45aをエッチングし、保護膜45aをマスクとして下部電極膜41エッチングして下部電極41aとし、上部電極43a、MTJ42a及び下部電極41aを覆うように保護膜45bを形成して、保護膜45b上に層間絶縁膜47を形成する。

(もっと読む)

半導体装置

【課題】低誘電率誘電体材料などからなる層間絶縁膜を用いた多層配線構造を有する半導体装置において、機械的ストレス又は熱的ストレスに起因する層間絶縁膜のクラック又は剥離等を確実に防止する。

【解決手段】半導体基板のチップ領域の外周部にシールリング4が設けられていると共に、当該チップ領域におけるシールリング4の近傍にチップ強度強化用構造体5が設けられている。チップ強度強化用構造体5は複数のダミー配線構造(例えばダミー配線構造5A〜5E等)から構成されている。各ダミー配線構造5A〜5E等はそれぞれ、最下層及び最上層の配線層のいずれか一方のみを含むか又はいずれも含まない2層以上の配線層に亘ってビア部を介して連続的に形成されている。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

半導体ウエハ、半導体ウエハの製造方法、および半導体装置

【課題】ヒューズ素子形成領域の配線を露出させることなく、クラックストップトレンチとボンディングパッド開口部を同時に形成する半導体ウエハ及びその製造方法を提供する。

【解決手段】半導体基板と多層配線構造とを少なくとも具備してなり、前記多層配線構造がチップ領域Aとヒューズ素子形成領域Bおよびダイシング領域Cとに渡って形成されてなる半導体ウエハにおいて、前記チップ領域に位置する前記多層配線構造上には、前記配線で構成されたボンディングパッド170が形成される一方、前記ダイシング領域には、前記多層配線構造が一部除去されることによって形成された二本以上が並行して並ぶダミーリングおよび、前記ダミーリング間に形成された、クラックストップトレンチ152となる溝部が設けられていることを特徴とする半導体ウエハを採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】研磨時にバリア膜が溶解することを抑制することができるような半導体装置及びその製造装置を提供する。

【解決手段】半導体基板上に形成された、溝109を有する絶縁膜107と、溝109に形成された第1のバリア膜111と第2のバリア膜112とを有する配線115とを備えている。第1のバリア膜111は、溝109の側壁及び底面上に形成され、第2のバリア膜112は、第1のバリア膜111を覆うように溝109に形成されている。さらに、第2のバリア膜112は、配線115の上面よりも下側に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 層間絶縁膜内の水分などによるバリアメタルの腐食を防止し、銅配線の信頼性の低下及び抵抗値の上昇を抑制し得る半導体装置、及びその製造方法を提供する。

【解決手段】 メチル基を含有する層間絶縁膜32内に配線溝37を形成する。配線溝37が形成された絶縁膜32に紫外線又は電子線を照射した後に、メチル基を有するガスを用いて絶縁膜の露出面を疎水化する。配線溝37の疎水化された内面に沿ってバリアメタル層41を形成し、該バリアメタル層41を介して配線溝37を銅配線43で充填する。一実施形態において、配線溝37はメタルハードマスク47を用いて絶縁膜32をエッチングすることにより形成され、絶縁膜32への紫外線又は電子線の照射は、メタルハードマスク47を残存させた状態で行われる。

(もっと読む)

461 - 480 / 2,805

[ Back to top ]