Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

481 - 500 / 2,805

半導体装置の製造方法

【課題】銅配線を有する半導体装置において、銅配線の配線抵抗やコンタクトと抵抗を増加することなく信頼性を向上しうる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に形成された開口部内に、銅に対して拡散防止作用を有する第1金属材料を含む第1の膜と、酸素を含有する銅膜を含む第2の膜と、銅と、酸素と結合することにより銅に対して拡散防止作用を有する第2金属材料とを含む第3の膜と、銅を主材料とする第4の膜とを含む配線層を形成した後、熱処理により、絶縁膜と第4の膜との間に、第1金属材料、第2金属材料及び酸素を含むバリア層を形成する。

(もっと読む)

電子デバイスの製造方法および該方法により製造された電子デバイス

GaAs半導体基板(HS)を備えた電子デバイスにおいて、基板前面には半導体素子(BE)が、基板背面には多層の背面金属化部(RM)が設けられている。このような電子デバイスのために、背面金属化部の有利な積層体構造が提案される。たとえば背面金属化部は固着層としてAu層を有している。  (もっと読む)

(もっと読む)

パターン形成方法及びパターン形成装置

【課題】生産性に優れたパターン形成方法及びパターン形成装置を提供することを目的とする。

【解決手段】被加工膜上の第1の領域に第1のパターン被覆率である第1のパターンを形成する工程と、第1の領域とは異なる被加工膜上の第2の領域に第2のパターン被覆率である第2のパターンを形成する工程と、を含む。第2のパターンを形成する工程は、ブロックコポリマー含有膜またはポリマー混合膜からなる第2の膜を被加工膜上に形成する工程と、第2の膜を自己組織化する工程と、自己組織化された第2の膜に含有される複数種のポリマーを、少なくとも1種類のポリマーを残すように選択的に除去することにより、第2のパターン被覆率を第1のパターン被覆率に近づけるように第2のパターンを第2の領域に形成する工程と、を有する。

(もっと読む)

不揮発性半導体記憶装置

【課題】複数の絶縁膜及び電極膜が交互に積層された信頼性が高い不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置において、メモリアレイ領域にメモリ積層体を設け、周辺回路領域にダミー積層体を設け、ダミー積層体にダミーホール31a,31bを形成し、その内部に絶縁部材を埋め込む。そして、絶縁部材内に複数本のコンタクト35a,35b,35c,35d,35eを形成する。コンタクト35a,35bはMOSFET40のソース層36に、コンタクト35c,35dはドレイン層37に、コンタクト35eはゲート電極38に接続される。そして、1つのダミーホール内に配置された複数本のコンタクトは、同じ電位が印加されるコンタクトとするか、ダミーホールの長手方向に延びる中心線41a,41c、41d、41f、41h、41j、41k、41lから外れた位置に配置する。

(もっと読む)

半導体素子の製造方法

【課題】簡単な工程設備を用いて短い工程時間内に半導体素子のビアを形成できる半導体素子の製造方法を提供すること。

【解決手段】基板101に絶縁膜107と拡散防止膜109で内壁を被覆したビアホール105を形成する。荷電された金属粒子113を、電気力又は磁気力を利用して移動させて、このホールを金属粒子で充填する。ビアホールの下部から上方へ充填されるので、内部に空隙が発生することを抑制できる。従来技術による銅電気メッキ方式と比較すると、非常に短時間内に大きくて深いビアホールを金属粒子で充填できるため、シリコン貫通ビア(TSV)の工程コスト、及び工程時間を短縮することが出来る。また、従来技術の樹脂成分が多く含まれているメタルペーストを用いる乾式充填方式と比較すると、荷電された金属粒子を用いることで、より密なTSV金属配線を形成できる。

(もっと読む)

導電性バリア膜形成材料、導電性バリア膜形成方法、及び配線膜形成方法

【課題】溝や穴の開口部と深さとの比(開口部/深さ)が1/5〜1/7のような条件を要求されても、又、厚さが10nm以下であっても成膜が可能で、かつ、銅の拡散防止(バリア性)に優れ、更には電気抵抗が小さく、銅膜との密着性にも優れた導電性バリア膜形成材料を提供する。

【解決手段】ケミカルベーパーデポジションにより銅膜の下地膜として導電性Ta−Zr系バリア膜を形成する為の材料であって、Taを持つ金属有機化合物と、Zrを持つ金属有機化合物とを含むことを特徴とする導電性バリア膜形成材料、および、前記Ta有機化合物、前記Zr有機化合物の一方または双方を溶解する溶媒とを含むことを特徴とする導電性バリア膜形成材料。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置の薄膜トランジスタ基板において、水素プラズマ処理時の水素による影響を低減する。

【解決手段】非晶質ケイ素の膜により形成された非晶質ケイ素層上に形成される銅配線において、第1添加元素として水素化物の生成エネルギーが負の元素、さらに第2添加元素を含む銅を主成分とする合金により形成された銅合金層107Aと、前記銅合金層の上に純銅により形成された純銅層107Bとを有する薄膜トランジスタ基板を備える。

(もっと読む)

半導体装置の製造方法

【課題】半導体製造プロセスにおけるガスの流量制御は、マスフローコントローラによって行われている。ここで使用される流量調整バルブは、流量を調整することに重点が置かれているため、閉鎖時にも微小ながらガスが流出する。このため、流量調整バルブの出力側に閉鎖特性の良好な開閉バルブが挿入されている。しかし、流量調整バルブと開閉バルブ間の流路系には、一定の容量を有するため、流量調整バルブが閉鎖されている間に、この流路系の圧力が流量調整バルブのリークを介して、上昇するという問題がある。このような出力側バルブ間空間の圧力上昇は、次に、開閉バルブが開いたときに、ガス被供給系への余剰のガス供給の原因となる。

【解決手段】本願発明は、マスフローコントローラのガス排出側の流量制御バルブと開閉バルブ間の圧力を計測することで、流量制御バルブの閉鎖時のリークガス流量を検知する半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜に形成する溝の寸法を制御しやすい半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、デュアルダマシンのビアが形成された下側絶縁膜と、ビアを埋め下側絶縁膜上に延在しレジスト材料でできた樹脂膜と、樹脂膜上に形成された酸化シリコン膜と、酸化シリコン膜上方に形成されたレジストパターンとを有するエッチング対象物に対し、レジストパターンをマスクとし、C4F6、CHF3、C4F8、及びCH3Fから選択されたガスの使用量、及び、O2及びArから選択されたガスの使用量を定めるレシピを複数含みエッチングチャンバの制御装置に記憶されたレシピ群から選択されたレシピで、酸化シリコン膜をエッチングして、ハードマスクを形成する工程と、ハードマスクを用い、樹脂膜及び下側絶縁膜をエッチングして、デュアルダマシンのトレンチを形成する工程とを有する。

(もっと読む)

貫通電極基板及び貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板は、表裏を貫通する貫通孔を有する基板と、前記貫通孔内に充填され、金属材料を含む導通部と、を備え、前記導通部は、結晶粒径が29μm以上の金属材料を少なくとも含み、前記導通部の一端は、前記導通部の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部は、面積重み付けした平均結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】設計基準を遵守しつつ容量値を向上しうる容量素子を有する半導体装置及びその製造方法を提供する。

【解決手段】複数の電極パターンをそれぞれ有し、積み重ねるように配置された複数の配線層と、複数の配線層の間にそれぞれ設けられ、隣接する配線層の複数の電極パターンのそれぞれを電気的に接続する複数のビア部と、複数の配線層及び複数のビア部の間隙に形成された絶縁膜とを有する容量素子を有し、ビア部は、電極パターンの中心に対して、電極パターンの延在方向と交差する方向にずらして配置されており、電極パターンは、ビア部が接続された部分において線幅が太くなっており、隣接する電極パターンとの間の間隔が狭まっている。

(もっと読む)

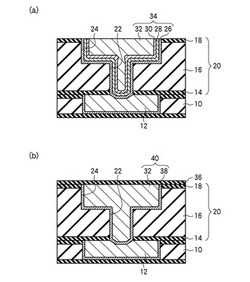

半導体装置およびその製造方法

【課題】放熱性が向上した半導体装置およびその製造方法の提供。

【解決手段】第1の辺を有する第1の面を有する半導体基板10と、前記半導体基板上に設けられた電極14と、前記電極の上に位置する第1の開口部24を有する第1の絶縁層16と、前記第1の絶縁層の上であって、前記電極の少なくとも一部を避けて設けられた樹脂層20と、前記樹脂層の上に設けられた第1の部分31と、前記第1の部分と前記電極とを電気的に接続する第2の部分32と、前記第1の部分または前記第2の部分と電気的に接続する第3の部分33と、を有する導電層と、前記導電層の前記第2の部分を覆うように設けられ、前記導電層の前記第1の部分の少なくとも一部の上に位置する第2の開口部41を有し、かつ、前記導電層の前記第3の部分を避けて設けられた第2の絶縁層40と、前記導電層の前記第3の部分は、前記第1の面の前記第1の辺と、前記第2の絶縁層との間に位置する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極とパッド電極との接続信頼性を高める。

【解決手段】一方の面と、前記一方の面と対向する他方の面とを有する半導体基板と、前記半導体基板の前記一方の面に設けられた絶縁膜と、前記半導体基板と前記絶縁膜とを貫通する貫通孔と、前記貫通孔の内壁に設けられ、平面視において前記貫通孔と重なる位置に接続孔を有する樹脂膜と、前記絶縁膜上に設けられ、平面視において前記貫通孔と重なる位置に第1凹部を有する配線層と、前記配線層に接続され、前記第1凹部内と前記樹脂膜を介して前記貫通孔内とに設けられた貫通電極とを含む半導体装置。

(もっと読む)

半導体集積回路装置の製造方法

【課題】信頼性の高い半導体集積回路装置の製造プロセスを提供する。

【解決手段】銅ダマシン配線プロセスのバリアメタル膜のタンタル系積層膜に関し、スパッタリング成膜チャンバ内のシールド内面に、比較的薄い窒化タンタル膜およびタンタル膜が交互に成膜されるが、この連続成膜プロセスを断続的に繰り返すと、膜の内部応力により剥がれて、異物やパーティクルの原因となる。この異物やパーティクルの防止のため、繰り返し、成膜するに際して、所定の間隔を置いて、厚い膜厚を有する異物防止用タンタル膜をチャンバの実質的な内壁に成膜する工程を設ける。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】エレクトロマイグレーションによる配線寿命の劣化を抑えると共に、配線間の抵抗が増加するのを抑えることができる半導体素子の製造方法及び半導体素子を提供する。

【解決手段】半導体素子は、半導体回路が形成された回路層10上に形成された絶縁膜20上に予め定めた配線パターンで形成された金属配線が、バックフロー効果を有する予め定めた長さに分割された複数の分割配線34A〜34Dから成り、かつ、各分割金属配線間にバリアメタル36が形成された構成となっている。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極とパッド電極との接続信頼性を高める。

【解決手段】一方の面と、前記一方の面と対向する他方の面を有する半導体基板と、前記半導体基板の前記一方の面に設けられた絶縁膜と、前記半導体基板と前記絶縁膜とを貫通する貫通孔と、前記絶縁膜上に設けられ、平面視において前記貫通孔と重なる位置に凹部を有する配線層と、前記貫通孔と前記凹部とで構成される溝の内壁および前記溝の底面に設けられ、且つ、平面視において前記配線層の前記凹部と重なる接続孔を有する樹脂膜と、前記配線層に接続され、前記樹脂膜を介して前記溝内に設けられた貫通電極とを含むことを特徴とする。

(もっと読む)

半導体装置のパッド構造

【課題】半導体装置のパッド構造を提供する。

【解決手段】半導体装置200は、半導体基板202、相互接続構造、複数のダミーメタルビア235及びパッド構造を備える。半導体基板202は、内部に複数の微小電子素子が設けられている。相互接続構造は、半導体基板202上に設けられ、複数の金属層210a〜210iと、金属層を隔離する複数のIMD層220とを有する。金属層210a〜210iは、最上金属層210iと、最下金属層210aと、最上金属層210iと最下金属層210aとの間に設けられた少なくとも2層の金属層とを含む。複数のダミーメタルビア235は、少なくとも2層の金属層間に設けられた1層又は2層以上のIMD層220内に形成される。パッド構造は、ダミーメタルビア235の上に直接設けられている。

(もっと読む)

半導体装置の製造方法

【課題】 埋め込み配線を形成する時に、埋め込み不良が生じにくい半導体装置の製造方法を提供する。

【解決手段】

(a)コンタクトプラグ25を有する第1層間絶縁膜24上に第2層間絶縁膜27を積層する工程と、(b)前記第2層間絶縁膜27に前記コンタクトプラグ25の上面を露出するトレンチ28aを形成する工程と、(c)前記トレンチ28a内で、開口端側に空間部を形成し、前記コンタクトプラグ側に、レジスト29cを埋め込む工程と、(d)等方性エッチングにより、前記第2層間絶縁膜27bのうち前記トレンチ28aの空間部で挟まれる前記第2層間絶縁膜27b部分の側壁を側方に後退させて、前記トレンチ28aの開口端側の幅よりも開口端側の幅が大きな加工トレンチ28bを形成する工程と、(e)前記レジスト29cを除去し、前記加工トレンチ28b内に配線金属層を埋め込む工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】配線及び半導体素子等を自由に配置できない領域を減少させる。

【解決手段】半導体装置は、半導体素子3が形成されている第1面及び第1面とは反対側の第2面を有する半導体基板1と、半導体基板1の上に形成され、且つ、第1のビア7を有する層間絶縁膜と、半導体基板1内に形成され、且つ、第1のビア7と接続する第2のビア13とを有し、第1のビア7の径は、第2のビア13の径よりも小さいことを特徴とする。

(もっと読む)

481 - 500 / 2,805

[ Back to top ]