Fターム[5F033PP27]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 塗布又は液体からの成膜 (5,037) | 電解メッキ (2,541)

Fターム[5F033PP27]に分類される特許

201 - 220 / 2,541

半導体装置および半導体装置の製造方法

【課題】本発明は、銅合金配線とビアとの接続面に、窒素を含むバリヤメタル膜が形成されている構造を有する半導体装置であって、銅合金配線とビアとの間における電気抵抗の上昇を抑制することができる半導体装置等を提供する。

【解決手段】本発明に係る半導体装置では、第一の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第一の銅合金配線と、第一の層間絶縁膜上に形成される第二の層間絶縁膜と、第二の層間絶縁膜内に配設されており、主成分であるCuにAlを添加した第二の銅合金配線とを、備えている。そして、第二の銅合金配線のAlの濃度は、第一の銅合金配線の前記Alの濃度未満である。

(もっと読む)

半導体装置及びその製造方法

【課題】銅又は銅合金からなる配線との密着性が高いバリアメタル層を備え、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置では、半導体基板100の上方に配置された絶縁膜106と、絶縁膜106中の溝に配置され、銅又は銅合金からなる配線115とを備え、絶縁膜106と配線115との間に、白金族元素、又は白金族元素の合金からなるバリアメタル層を有しており、バリアメタル層は、非晶質構造を有する第1のバリアメタル層109と第1のバリアメタル層109の上に配置された多結晶構造を有する第2のバリアメタル層110からなる積層構造であり、第2のバリアメタル層110には銅が含まれており、第2のバリアメタル層110中の金属に占める銅の割合は50at%以下である。

(もっと読む)

Cu配線の形成方法およびCu膜の成膜方法、ならびに成膜システム

【課題】微細なトレンチまたはホール等の凹部にボイドを発生させずに確実にCuを埋め込むことができ、かつ低抵抗のCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202において、トレンチ203の表面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上に、加熱しつつ、PVDによりCuがマイグレーションするようにCu膜206を形成してトレンチ203を埋める工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

(もっと読む)

金属層の結晶粒径及び粒径分布評価方法並びにそれを用いた半導体集積回路装置の製造方法

【課題】非破壊かつオンラインで金属層の結晶粒径及び粒径分布を評価する方法を実現する。

【解決手段】結晶組織を有し特定の面方位においてX線に対して回折ピークを持つ金属層にX線を照射して得られる回折ピークを入手するステップA、回折ピークに基づいて面積平均コラム長及び体積平均コラム長を求めるステップB、面積平均コラム長及び体積平均コラム長から結晶粒径の対数正規分布を求めるステップCを具備する。

(もっと読む)

表面被覆方法、並びに半導体装置、及び実装回路基板

【課題】配線及び絶縁膜へダメージを与えることなく、絶縁膜上の導電性の不純物によるめっきの異常成長を抑制することができる表面被覆方法、並びに該方法を用いて製造される半導体装置、及び実装回路基板の提供。

【解決手段】水溶性樹脂、有機溶剤、及び水を含有する表面被覆材料を、表面に露出した絶縁膜及び表面に露出したパターニングされた金属配線を有する積層体の少なくとも前記絶縁膜の表面を覆うように塗布し、前記絶縁膜の表面に被膜を形成する表面被覆方法である。

(もっと読む)

配線パターン及びその製造方法並びに半導体装置

【課題】配線パターンを覆う絶縁層をできる限り薄くする。

【解決手段】配線パターン1は、第一の一対の端子3,4及び該第一の一対の端子3,4間を接続する複数の第一の引き回し部5を有する第一の配線2と、第二の一対の端子7,8及び該第二の一対の端子7,8間を接続する少なくとも一つの第二の引き回し部9を有する第二の配線6とを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】孤立パターンに銅の化合物が析出するのを抑制する半導体装置の製造方法と、半導体装置とを提供する。

【解決手段】半導体装置では、素子・基板層ESLの低誘電率膜LOW1、ファイン層FLの極低誘電率膜ELK1等およびセミグローバル層SGLの低誘電率膜LOW2等のそれぞれの開口部に形成されるアライメントマークAMおよび重ね合わせ検査マークKMが、半導体基板SUBに形成された所定の導電型の不純物領域IRに電気的に接続されて、アライメントマークAMおよび重ね合わせ検査マークKMが接地電位に固定されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】nチャネル型MISFETQn1,Qn2を覆うように半導体基板1上に引張応力膜としての窒化シリコン膜5を形成する。窒化シリコン膜5は窒化シリコン膜5a,5b,5cの積層膜である。窒化シリコン膜5a,5bの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分よりも小さく、窒化シリコン膜5a,5bは、成膜後に紫外線照射処理を行って引張応力を増大させる。窒化シリコン膜5a,5b,5cの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分以上であり、窒化シリコン膜5cに対しては紫外線照射処理を行わない。

(もっと読む)

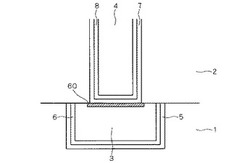

ヴィア構造およびその作製方法

【課題】より小さな径の基板貫通ヴィアが形成できるようにする。

【解決手段】基板101の回路が形成されている主表面101a側から所望の孔径の範囲で形成可能な深さに形成された第1孔部102と、基板101の裏面側から形成されて第1孔部102に接続する第2孔部103と、第1孔部102の内部に形成された第1孔部配線104と、第1孔部配線104に接続して基板101の主表面101a側に形成された表面配線層105と、第2孔部103の内部に第1孔部配線104に接続して形成された第2孔部配線106と、第2孔部配線106に接続して基板101の裏面側に形成された裏面配線層107とを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

(もっと読む)

半導体装置

【課題】封止される被対象物に段差部を備えているが、封止部を設けた際に該段差部に起因したボイドの発生が抑制され、ひいては優れた耐食性を備える半導体装置と、その製造方法を提供する。

【解決手段】本発明に係る半導体装置1は、導電性を有する剛体からなる基板2と、該基板の少なくとも一方の面に絶縁部3を介して配された導電部5と、該絶縁部及び該導電部を覆うように配された感光性樹脂からなるフィルム6と、を備えている。前記基板2は、一方の面に開口する凹部及び/又は貫通孔2aを備え、該凹部及び/又は該貫通孔はその内部が略全域にわたって、前記フィルム6により充填されている形態をなす。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、光電変換膜が半導体基板上に積層された積層型の半導体装置に関する。

【解決手段】半導体基板と、半導体基板上に形成され、交互に積層された層間絶縁膜と配線層とからなる多層配線層と、多層配線層内において、半導体基板の周縁に沿って環状に形成されたシールリングとを備え、シールリングは、各配線層に形成された環状のシール配線と、各層間絶縁膜に少なくとも1つ形成された環状のシールビアとが積層された構造であり、シールビアを介して積層方向に隣接する少なくとも1組のシール配線では、下方のシール配線の外周面の位置が、上方のシール配線の外周面の位置よりも外側にあることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】半導体装置の小型化、特に、狭ピッチ化に対する技術を提供する。

【解決手段】半導体チップ1C上に設けられたパッド2と、プローブ領域10Aおよび接続領域10Bのパッド2上に開口部11を有し、半導体チップ1C上に設けられたパッシベーション膜3と、接続領域10Bのパッド2上に開口部12を有し、パッド2上およびパッシベーション膜3上に設けられたパッシベーション膜5と、パッド2と電気的に接続され、接続領域10B上およびパッシベーション膜5上に設けられた再配線7とを備える。接続領域10Bより半導体チップ1Cの外周部側に設けられたプローブ領域10Aのパッド2にプローブ痕100が存在し、接続領域10Bから半導体チップ1Cの中央部側に延びて再配線7が存在している。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の金属配線を高信頼性化する。

【解決手段】一つの実施形態によれば、半導体装置は、第1の配線材、開口部、及び電極端子部が設けられる。第1の配線材は、半導体基板上の第1の層間絶縁膜上に設けられ、配線層として用いられる。開口部は、第1の配線材上に設けられた第2の層間絶縁膜をエッチングして形成される。電極端子部は、開口部及び開口部周囲の第2の層間絶縁膜上に設けられ、第1の配線材に接するバリアメタル膜、シードメタル膜、及び第2の配線材が開口部を覆うように積層形成され、第2の配線材の上部及び側面に被覆メタル膜が形成される。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン法による銅配線接続において、コンタクト抵抗の上昇を抑制する半導体装置の製造方法を提供する。

【解決手段】第1の配線25上に積層された第1の拡散防止膜27及び層間絶縁膜のうち、第1の層間絶縁膜28をエッチングすることで第1のホールを形成する。第1の拡散防止膜がエッチングされにくい条件で、第1のホールの下方に位置する第1の層間絶縁膜をエッチングして第2のホールを形成する。第2のホールを埋め込むように、第1の層間絶縁膜よりもエッチング速度の速い第2の層間絶縁膜を形成する。第1の層間絶縁膜の上面が露出するまで第2の層間絶縁膜をエッチングすることで、第2のホールと一体とされた配線形成用溝を形成する。第2のホール内に残存する第2の層間絶縁膜を選択的に除去し、第2のホールの下方に位置する第1の拡散防止膜を選択的に除去する。

(もっと読む)

半導体用銅合金配線及びスパッタリングターゲット並びに半導体用銅合金配線の形成方法

【課題】半導体用銅合金配線自体に自己拡散抑制機能を有せしめ、活性なCuの拡散による配線周囲の汚染を効果的に防止することができ、またエレクトロマイグレーション(EM)耐性、耐食性等を向上させ、バリア層が任意に形成可能かつ容易であり、さらに半導体用銅合金配線の成膜工程の簡素化が可能である半導体用銅合金配線及び同配線を形成するためのスパッタリングターゲット並びに半導体用銅合金配線の形成方法を提供する。

【解決手段】Mn0.05〜5wt%を含有し、Sb,Zr,Ti,Cr,Ag,Au,Cd,In,Asから選択した1又は2以上の元素の総量が10wtppm以下、残部Cuである自己拡散抑制機能を備えた半導体用銅合金配線。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び電子機器

【課題】センサ基板と回路基板とを電極間で張り合わせてなる構成において電極間の接合面積を確保することが可能な3次元構造の固体撮像素子を提供する。

【解決手段】光電変換部21が配列形成されたセンサ基板2と、光電変換部21を駆動する回路が形成されセンサ基板2に対して積層された回路基板7と、センサ基板2における回路基板7側の界面に引き出されたセンサ側電極45と、回路基板7におけるセンサ基板2側の界面に引き出された回路側電極65とを備え、センサ側電極45と回路側電極65とは、凹型電極に凸型電極を嵌め合わせた状態で接合されていることを特徴とする固体撮像素子1である。

(もっと読む)

半導体装置の製造方法及び製造装置

【課題】半導体装置のエッチングを精度良く行い、再生率を低減させる

【解決手段】基板にトランジスタを形成し、トランジスタを覆うように第1層間絶縁膜22を形成する。さらに、第1層間絶縁膜22の上方に形成したレジスト膜27を用いて第1層間絶縁膜22をエッチングし、トランジスタのソース/ドレイン領域に到達するコンタクトホール31を形成する。この際、レジスト膜27の開口部27Aの半径rと、開口部27Aが設計位置からずれている位置ずれ量ΔXとを測定し、コンタクトホール31に必要な半径Rxと、コンタクトホール31を形成可能な限界距離Sとから、r+ΔX−S<ES<r−Rxを満たす半径差ESを決定し、半径差ESからエッチング条件を決定する。

(もっと読む)

201 - 220 / 2,541

[ Back to top ]