Fターム[5F033QQ02]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971) | 反射防止に関するもの (535)

Fターム[5F033QQ02]の下位に属するFターム

導電膜の反射防止膜を用いるもの (97)

絶縁膜の反射防止膜を用いるもの (242)

Fターム[5F033QQ02]に分類される特許

101 - 120 / 196

半導体装置の製造方法

【課題】リソグラフィの解像限界以上で、かつ、寸法制御性に優れた超微細パターンを容易に形成する。

【解決手段】パターニングすべき第1の膜として、例えばアモルファスシリコン膜13を形成し、このアモルファスシリコン膜13上にラインとスペースの比率が略3:1のパターン14、17を形成し、次いで、パターン14、17をマスクとしてアモルファスシリコン膜13を加工し、次いで、パターン14、17を両側から幅が略1/3となるまでスリミングした後、このスリミングされたパターンの反転パターン層として、例えばBSG膜18を形成し、次いで、このBSG膜18をマスクとしてアモルファスシリコン膜13を再加工して、ラインとスペースの比率が略1:1で、かつ、ピッチが元の略半分のパターンを形成する。

(もっと読む)

メタルゲートのドライエッチング方法

【課題】メタルゲートのドライエッチング時に、下地HfSiON膜の突き抜けを防止しながら、p−n差の無いエッチング形状を得る。

【解決手段】シリコン基板の表面に形成された下地HfSiON膜16と、この上に形成されたTaSiN膜14とTiN膜15からなるメタルゲートと、この上に形成されたW膜13と、SiN膜12と、反射防止膜11と、レジスト膜10とを有するウェハのドライエッチング方法において、メタルゲート14、15のドライエッチング時に、下地HfSiON膜16に対する選択比が高い、CF系ガス(CHF3、CF4など)と塩素と窒素ガスとの混合ガスを用いて0.5Pa以下の圧力でエッチングを行う。

(もっと読む)

反射防止膜用重合体、これを含む反射防止膜組成物及びこれを利用したパターン形成方法

【課題】液浸リソグラフィ工程およびダマシン工程への適用できる反射防止膜用架橋重合体、これを含む反射防止膜用組成物、及びこれを利用したフォトレジストパターンの形成方法を提供する。

【解決手段】アクリレート及びアクロレインの共重合体をエタンチオールで変性して得られた(アクリレート/3,3ージチオエチルプロペン)高分子がイオウ元素を含む屈折率の高い反射防止膜用架橋剤重合体として優れていることを見いだした。さらに、反射防止膜用組成物に関するものであり、上記架橋重合体、光吸収用ベース樹脂、熱酸発生剤及び有機溶媒から構成される。該反射防止膜用組成物は半導体素子の製造工程中、特に193nmArF光源を利用した液浸リソグラフィ工程及びダマシン工程に非常に適切に用いられ得る。

(もっと読む)

半導体素子の微細パターン形成方法

【課題】オーバーレイによって臨界寸法が不良になる問題を除去すると共に、DEET方法で全形態の微細パターンを形成することが可能な半導体素子の微細パターン形成方法の提供。

【解決手段】半導体基板上にエッチング対象膜、第1補助膜、分離膜および第2補助膜を形成する段階と、第1補助膜に焦点を合わせて第1露光工程を行う段階と、第2補助膜に焦点を合わせて第2露光工程を行う段階と、第2補助膜を現像して第2補助パターンを形成する段階と、第2補助パターンをエッチングマスクとして用いるエッチング工程によって分離膜および第1補助膜をエッチングして第1補助パターンを形成する段階と、第1補助パターンを現像して第3補助パターンを形成する段階と、第3補助パターンを用いてエッチング対象膜をエッチングする段階とを含む、半導体素子の微細パターン形成方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】タングステン配線の断面形状を良好にすることにより、配線抵抗の増大及び配線信頼性の低下を防ぐ。

【解決手段】先ず、下地100を用意して、下地上に、バリア膜120、配線膜130及びマスク膜140を順次に積層する。バリア膜及びマスク膜が窒化チタンであり、配線膜がタングステンである。次に、マスク膜上に、反射防止膜150を塗布する。次に、反射防止膜上に、レジスト膜を形成した後、フォトリソグラフィによりパターニングして、レジストマスク160を形成する。レジストマスクは、配線形成領域105を覆い、かつ配線非形成領域107を露出する。次に、フッ素系ガスを用いたエッチングにより反射防止膜のパターニングを行う。次に、塩素系ガスを用いたエッチングによりマスク膜のパターニングを行う。次に、フッ素系ガスを用いたエッチングにより配線膜のパターニングを行う。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ダマシン法で多層配線構造を形成する際に、EM耐性およびSM耐性を高めつつ、接続不良を防いで配線の歩留まりを向上させる。

【解決手段】半導体装置は、半導体基板上に形成され、銅を主成分とする材料により構成された銅配線上にシリコン含有ガスを照射して、銅配線の表面にシリコン含有層を形成する工程(S102)と、銅配線上に、拡散防止膜を形成する工程(S104)と、拡散防止膜上に、Si、O、およびCを含む層間絶縁膜を形成する工程(S106)と、層間絶縁膜に、拡散防止膜に達する凹部を形成する工程(S108)と、凹部側壁に露出した層間絶縁膜表面に他の領域よりも酸素濃度が高い改質層を形成する工程(S110)と、拡散防止膜を除去して銅配線表面を露出させる工程(S112)と、凹部内に導電材料を埋め込み配線を形成する工程(S114)とにより形成される。

(もっと読む)

半導体装置の製造方法および制御システム

【課題】複数の絶縁膜にパターンの異なる配線溝またはビアホールを形成して多層配線構造を形成する際に、パターンの違いに関わらず、配線幅またはビア幅を均等にする。

【解決手段】層間絶縁膜上に反射防止膜と上層レジスト膜とをこの順で積層し、上層レジスト膜をマスクとして反射防止膜をエッチングする際に、上層レジスト膜に形成される開口部の寸法幅L1に対する層間絶縁膜に形成される凹部の寸法幅L2の寸法シフト量Δ(L2−L1)と相関関係を有するエッチング条件の値を、上層レジスト膜に形成される開口部の開口率が大きいほど寸法シフト量Δ(L2−L1)が小さくなるように開口率に応じて変動させて反射防止膜をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】プロセスコストを抑制しつつも、微細なパターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板1の主表面上に被加工層52を形成する工程と、被加工層52上に下地層53を形成する工程と、下地層53上に第1中間層54と第2中間層55とを順次形成する工程と、下地層53で被加工層52を覆った状態で、第2中間層55をパターニングする工程と、パターニングされた第2中間層55上に第1マスクパターンを形成する工程と、第1マスクパターンを用いて、第2中間層55をパターニングする工程と、パターニングされた第2中間層55を用いて、第1中間層54と下地層53をパターニングして、第2マスクパターンを形成する工程と、第2マスクパターンを用いて、被加工層52をパターニングする工程とを備える。

(もっと読む)

プラズマエッチング方法

【課題】シリコンと炭素とを含む被エッチング基板に対してプラズマエッチングを行ってホールを形成する場合、ホール同士の端部の間隔が例えば10μm以上に広い場合や0.1μm程度に狭い場合であっても、エッチングストップ膜を貫通することなく、更に途中でエッチングが停止することなくエッチングを行うこと。

【解決手段】メインエッチングの後のオーバーエッチングを行う際に、炭素とフッ素とを含む処理ガスをプラズマ化して、更に基板に対向するように設けられた上部電極に負の直流電圧を印加する。

(もっと読む)

微細パターンの形成方法、パターン保護材料と半導体装置

【課題】複数のパターンを合成して微細パターンを形成する方法において、プロセスを簡易化し、低コストで実施できる方法を提供する。

【解決手段】第1のパターンを形成する工程と、保護膜を形成する工程と、第2のパターンを保護膜上に形成する工程と、第2のパターンをマスクとして、保護膜と、保護膜により保護されたパターンをドライエッチングする工程と、保護膜を除去する工程とを備え、保護膜の形成工程から保護膜の除去工程までの工程を、単数回または複数回実施する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のインライン欠陥検査工程において、物理解析時に短時間で故障箇所の位置を確認することのできる技術を提供する。

【解決手段】テストパターンの基幹配線部、配線中央部および配線端部にそれぞれ基幹配線部セパレータ1、配線中央部セパレータ2および配線端部セパレータ3を配置し、テストパターンに搭載したこれら各種セパレータ1,2および3を、欠陥観察の際に欠陥の座標位置を確認する指標とする。例えば配線中央部セパレータ2は、セパレータ長Lの長さ分だけ第2配線層4を表面に露出させて、配線パターンとして観察される構造とし、その他の配線中央部は第1配線層5を経由して基幹配線部から配線端部へと電気的に接続することにより、配線パターンとして観察されない構造とする。

(もっと読む)

半導体素子製造方法及び半導体素子製造装置

【課題】半導体素子においてコンタクト孔の深さが異なるデュアルダマシン構造を形成する場合に、配線溝の深さが不均一となる。

【解決手段】コンタクト孔60が形成された層間絶縁膜54の表面に、2層のBARC膜62,64を順次形成し、コンタクト孔60を段階的に埋め、当該表面を平坦化する。BARC膜62は、BARC材をスピンコートしベークして形成する。BARC膜62のベーク後、間断なく、BARC膜64を形成するBARC材の塗布を行う。これにより、異なる深さのコンタクト孔60-1〜60-3の上に形成されるBARC膜62,64の厚みを均等とすることができ、エッチバックにてBARC膜62,64から層間絶縁膜54の上部まで掘り下げて形成される配線溝68の深さも均等とすることができる。

(もっと読む)

ランディングプラグコンタクトを備える半導体素子の製造方法

【課題】オートアライメントコンタクトを利用したコンタクト形成の際、高い縦横比によるエッチングターゲットの増加を防止でき、オートアライメントコンタクトエッチングに用いるハードマスクによる段差を克服し、後続のパターニングを容易に行い、かつ、処理を単純化させることができる半導体素子の製造方法を提供すること。

【解決手段】パターン22〜24が形成された半導体基板21上にエッチングバリア膜25を形成するステップ、エッチングバリア膜上に層間絶縁膜26Bを形成するステップ、層間絶縁膜を平坦化するステップ、層間絶縁膜をリセスさせるステップ、層間絶縁膜上にハードマスクパターン200Bを形成するステップ、層間絶縁膜をエッチングしてコンタクトホール201を形成するステップ、コンタクトホールの底のエッチングバリア膜をエッチングするステップ、及び、コンタクトホール内にプラグコンタクトを形成するステップを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の上に形成された構造体の配置密度や大きさに不均一性があっても、半導体基板を保護しながら所望の構造体を選択的にエッチングすることができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、(A)シリコン基板10に複数のゲート電極15を形成する工程と、(B)シリコン基板10の全面に、複数のゲート電極15を被覆する有機反射防止膜16を形成する工程と、(C)複数のゲート電極15のうち加工対象であるゲート電極15の上方に開口を有するレジスト17を形成する工程と、(D)前記開口の内側においてシリコン基板10が有機反射防止膜16で被覆された状態を維持しながらレジスト17をマスクとして有機反射防止膜16をエッチングし、加工対象であるゲート電極15を露出させる工程と、(E)前記開口の内側において有機反射防止膜16を残存させながら、加工対象であるゲート電極15をエッチングする工程と、(F)レジスト17と有機反射防止膜16とを除去する工程とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】ハードマスクを使用して金属膜、絶縁膜等の膜をパターニングする工程を含むFeRAM等の半導体装置の製造方法において、ハードマスクを用いて膜をパターニングした後の基板上の残渣、スカム等をさらに減らす製造方法を提供する。

【解決手段】パターニングの対象となるIrO2からなる第1の導電膜15の上に、アルミナ膜の犠牲膜16を介してTiNなどの窒化物のハードマスク17aを形成し、その後に、ハードマスク17aに覆われない領域の第1の導電膜15をパターニングし、その後に、犠牲膜16をフッ化アンモニウム、アミド、有機酸、有機酸塩類、水の混合液を使用したウェット処理により除去することにより、ハードマスク17aを第1の膜15のパターンの上から剥離してハードマスク17aの表面に付着した残渣、スカム等が再付着する防止工程を有している。

(もっと読む)

ウェットエッチングアンダカットを最小にし且つ超低K(K<2.5)誘電体をポアシーリングする方法

【課題】 基板上の膜を処理する方法の提供。

【解決手段】 一態様において、方法は、シリコンと、炭素とを含み、所望により酸素及び/又は窒素を含んでもよい薄層を膜上に堆積させることによりフォトレジストが膜から除去された後のパターン形成された低誘電率膜を処理するステップを含む。薄層は、パターン形成された低誘電率膜に炭素を多く含む疎水性表面を与える。薄層は、また、続いての湿式洗浄プロセスと、低誘電率膜上に続いて堆積される層の前駆物質による浸透から低誘電率膜を保護する。

(もっと読む)

半導体装置の製造方法

【課題】 パターン形成を簡略化した半導体装置の製造方法を提供することを目的とする。

【解決手段】 被加工膜100上に第一のパターン105を形成し、第一のパターン105が形成された領域を含む被加工膜100上に反射防止膜106及びレジスト膜107を順に形成し、レジスト膜107を加工してレジストパターン103を形成し、レジストパターン108下に露出した反射防止膜106をレジスト膜107の加工に使用した現像液と同一の現像液により加工して、被加工膜100の一部及び第一のパターン105の少なくとも一部を露出し、第一のパターン105及びレジストパターン108をマスクに被加工膜100を加工することにより、被加工膜100に配線パターン110等を形成する。

(もっと読む)

電子構造の製造方法

【課題】上部ダマシン銅配線と下部配線のダマシン・タングステンとの間の、信頼性ある、低抵抗な接続形成方法および構造の提供。

【解決手段】下部ダマシン・タングステン配線に接続するデュアル・ダマシン銅相互接続部を製造するための方法であり、半導体基板110上に第1の層を形成し、第1の層上に窒化ケイ素層、窒化ケイ素層上に二酸化ケイ素層150を形成する。第1の層は絶縁材料によって電気的に絶縁されたタングステン相互接続部を含む。二酸化ケイ素層と窒化ケイ素層とを通る2つの接続トラフをエッチングし、下部タングステン相互接続部を露出させ、2つの接続トラフ間の二酸化ケイ素層の最上部をエッチングすることによって、連続スペースを形成する。2つの接続トラフ間の二酸化ケイ素層の角部が低減される。連続スペースにダマシン銅を充填すれば、デュアル・ダマシン銅相互接続部が、露出した下部タングステン相互接続部と電気的に接続する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、配線の信頼性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に第1層配線溝1aを有するウェハW上に、少なくとも第1層配線溝1aに埋め込まれ、不純物濃度が下部4bより上部4aの方が高いめっき膜4を形成する工程と、めっき膜4に熱処理を施す工程と、めっき膜4を熱処理した後、第1層配線溝1aに埋め込まれた部分以外のめっき膜4を除去する工程とを具備することを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

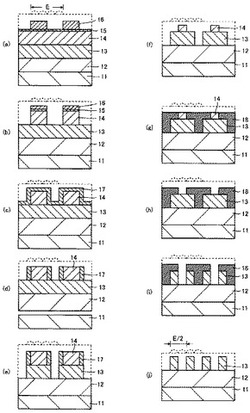

微細ピッチのハードマスクパターンの形成方法及びそれを用いた半導体素子の微細パターン形成方法

【課題】 フォトリソグラフィ工程での解像限界を超える微細ピッチのパターン形成を実現可能とする、微細ピッチのハードマスクパターンの形成方法を提供する。

【解決手段】基板上に第1ハードマスク層を形成する。第1ハードマスク層20上に複数の第1犠牲パターンを形成し、第1犠牲パターンのうち相互隣接した2個の第1犠牲パターン間にリセスの形成された上面を有する第2ハードマスク40層を形成し、リセス内に第2犠牲パターンを形成する。第1犠牲パターンの上面を露出させて第1及び第2犠牲パターンを除去する。第2ハードマスク層40の上部をエッチングマスクとして第2及び第1ハードマスク層40及び20をエッチングしハードマスクパターン60を形成する。ハードマスクパターン60をエッチングマスクとして利用し半導体素子の微細パターンを形成する。

(もっと読む)

101 - 120 / 196

[ Back to top ]