Fターム[5F033QQ02]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971) | 反射防止に関するもの (535)

Fターム[5F033QQ02]の下位に属するFターム

導電膜の反射防止膜を用いるもの (97)

絶縁膜の反射防止膜を用いるもの (242)

Fターム[5F033QQ02]に分類される特許

61 - 80 / 196

半導体装置の製造方法

【課題】多層マスクエッチングを用いたホール加工において、開口径及び深さの均一なホールを絶縁膜内に形成する。

【解決手段】窒化膜1上に、層間絶縁膜2とレジスト膜3とハードマスク膜4とを順に積層させた多層マスクを形成する工程と、層間絶縁膜2を露出させる開口を多層マスクに形成する工程と、フルオロカーボンを含むガスFRをエッチングガスとしてエッチングを行うことにより、開口内の層間絶縁膜2を除去しつつ、開口の周囲のハードマスク膜4を除去する工程(図3(b))と、開口の周囲にレジスト膜3が露出する前に、ガスFRをガスFRよりもC/F(炭素原子数とフッ素原子数との比率)が高いフルオロカーボンを含むガスFPに切り替えてエッチングを行うことにより、開口から窒化膜1が底面をなすコンタクトホールを形成する工程(図3(c))と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】リソグラフィの露光解像限界未満の寸法を有するパターンを形成するための工程数を削減し、また、歩留まりを向上させる半導体装置の製造方法を提供する。

【解決手段】被加工材上に第1のレジスト材からなる第1のレジストパターンを形成する工程と、前記第1のレジスト材が感光するエネルギー線を前記第1のレジストパターンに照射する工程と、前記エネルギー線を照射後に前記第1のレジストパターンのベーク処理を行う工程と、前記被加工材上に前記第1のレジストパターンを覆うように被覆膜を形成する工程と、前記ベーク処理後に前記被覆膜上に第2のレジスト材からなる第2のレジストパターンを形成する工程と、を含む半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

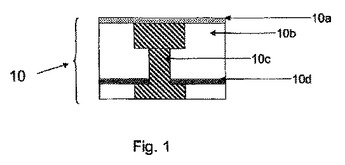

【課題】 反射防止膜を使用しなくてもアルミニウム配線パターンを高精度に形成できる半導体装置の製造方法を提供する。

【解決手段】 半導体基板10上にアルミニウム層もしくはアルミニウム合金層3をバリアメタル層2を介して形成し、アルミニウム合金層3の表面にドライエッチングガスを用いて均一な微細凹凸を有する表面層3aを形成する。そして、アルミニウム合金層上にフォトレジストを塗布し、フォトレジストを配線パターンを有するフォトマスクを用いて露光し、現像して配線パターンを形成し、フォトレジストをマスクにして、アルミニウム合金層をエッチングしアルミニウム配線5を形成する。表面層3aを窒素および酸素条件下でアッシング処理して表面層3aの凹凸より細かい凹凸を有する酸化膜を形成することによって反射率を大きく低下させることができる。

(もっと読む)

配線の形成方法

【課題】プロセスの自由度が大きい配線の形成方法を提供する。

【解決手段】配線層25上に絶縁層31を形成する工程と、絶縁層31上に第1マスク層32と第2マスク層33とを形成する工程と、第2マスク層33上にレジスト層42を形成する工程と、レジスト層42をパターニングする工程と、レジスト層42をマスクとして第2マスク層33をパターニングする工程と、レジスト層42及び第2マスク層33をマスクとして第1マスク層32を途中までエッチングする工程と、レジスト層42を取り除く工程と、第2マスク層32をマスクとして第1マスク層32の残りをエッチングして第1マスク層32をパターニングする工程と、パターニングされた第1マスク層33をマスクとして絶縁層31をエッチングして配線溝36を形成する工程と、配線溝36に導電体37を埋め込んで、配線層25に接続する埋め込み配線層38を形成する工程と、を有する。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体層と、酸化物半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層との順で積層されたゲート電極を含むゲート配線と、酸化物半導体層と、前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、酸化物半導体層と電気的に接続され、第3の導電層と第4の導電層との順で積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

半導体装置の製造方法

【課題】デュアルダマシン溝(接続孔)内への異物の残留を回避し、配線接続の信頼性および半導体装置性能の向上を図る。

【解決手段】第4配線層の配線33上に絶縁膜34〜38を順次形成し(絶縁膜34,36,38はシリコン窒化膜からなる。絶縁膜35,37はシリコン酸化膜からなる)、絶縁膜38に溝パターン40a、40bをフォトリソグラフィを用いて転写する。絶縁膜38の溝パターン40を埋め込む反射防止膜41を形成し、さらに孔パターン43を有するレジスト膜42を形成する。レジスト膜42の存在下でエッチング処理を施し、絶縁膜38,37,36および絶縁膜35の一部に孔パターン43を転写する。その後、レジスト膜42,反射防止膜41を除去し、絶縁膜38をマスクとして溝パターン40を絶縁膜37に、孔パターン43を絶縁膜35に転写する。

(もっと読む)

プラズマ処理装置

【課題】 低誘電率膜(Low-k膜、例えばSiOCH)において、膜ダメージを発生せず、高選択比で高精度なエッチングを実現可能な処理条件を提供する。

【解決手段】 BARCエッチングステップにてパターン寸法よりも溝又は孔を細く加工し、N2またはO2を含む高マスク選択比条件にてエッチングを行う。その後N2またはO2を含まず、ウエハに印加するバイアス出力を低下させて等方的なエッチングを行う、又はパターン寸法よりも溝又は孔をやや細く加工するN2またはO2を含む高マスク選択比条件と、N2またはO2を含まず、ウエハに印加するバイアス出力を低下させて等方的なエッチングを周期的に行う。

(もっと読む)

半導体装置の製造方法

【課題】 誘電率の増加を抑制しながら、しかも平滑な底面を有するトレンチを備えた半導体装置の製造方法を提供する。

【解決手段】 被処理基板上に第1の絶縁膜64を形成する工程と、第1の絶縁膜64上に有機薄膜65を形成する工程と、有機薄膜65上に第2の絶縁膜66を形成する工程と、第1の絶縁膜64と有機薄膜65と第2の絶縁膜66を貫通するビアホール71aを形成する工程と、第2の絶縁膜66上にビアホール71aが埋められように無機系材料からなる犠牲膜68を形成する工程と、犠牲膜68上に所定のパターンを有するレジスト膜69を形成する工程と、レジスト膜69のパターンにしたがって有機薄膜65の上面に達するトレンチ71bを形成する工程と、レジスト膜69および有機薄膜65のうちトレンチ71bに露出した部分を被処理基板から同時に除去する工程と、を有する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】多層配線構造の半導体装置のパッケージ工程や環境試験において、膜剥れが起き難い技術を提供する。

【解決手段】絶縁層中に配線層が構成された下層配線層、前記下層配線層上に設けられた層間絶縁層、前記層間絶縁層の上に設けられた絶縁層中に配線層が構成された上層配線層、及び前記層間絶縁層に構成された前記下層配線層の配線層と前記上層配線層の配線層とを電気的に接続する為の接続層とを具備する半導体装置において、

前記層間絶縁層A7に、該層間絶縁層A7の上層および/または下層に繋がる埋設層A15が構成され、前記埋設層A15および接続層A12を有する層間絶縁層A7の平均弾性率が10GPa以上であるよう構成されてなる半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造工程において大気中の水分による銅配線や層間絶縁膜への影響を抑えることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、金属層、層間絶縁膜を順次形成し、層間絶縁膜に、フッ素系エッチングガスを用いてエッチングを行い、金属層に到達する所定パターンの開口部を形成した後、大気に晒すことなく、半導体基板上に塩素系シランガスを供給して放電し、少なくとも開口部の内面にSi膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来のエアギャップ構造より、さらに容量及び容量ばらつきを低減することができる。

【解決手段】 基板上の絶縁膜17上に、銅を主成分として含む配線26を形成する。それから、リザーバーパターン用絶縁膜21、22及びバリア絶縁膜29を形成し、配線26の上面および側面上と絶縁膜17及び絶縁膜29上に銅の拡散を抑制または防止する機能を有する絶縁膜31を形成する。このとき、狭い配線間スペース底部の絶縁膜17の膜厚保は、配線26上の絶縁膜31の膜厚より、薄く成膜することで細線ピッチの配線容量を効率良く低減する。その後、低誘電率からなる絶縁膜36及び絶縁膜37を成膜する。その際、配線26の隣接配線間において、対向する配線側面の上方での堆積速度が下方での堆積速度より大きくなるように絶縁膜36を形成し、エアギャップを形成する。最後に、層間CMPによって、絶縁膜37を平坦化する。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】CO2プラズマに晒された低誘電率絶縁膜のダメージを回復させて、低誘電率絶縁膜を良好な状態にすることができ、半導体装置における性能の向上と信頼性の向上を図ることのできる半導体装置の製造方法及び半導体装置の製造装置を提供する。

【解決手段】基板に形成された低誘電率絶縁膜をエッチングするエッチング処理工程と、当該エッチング処理工程の後に基板をCO2プラズマに晒すCO2プラズマ処理工程と、CO2プラズマ処理工程の後に、低誘電率絶縁膜に紫外線を照射する紫外線処理工程とを有する半導体装置の製造方法。

(もっと読む)

半導体素子の微細パターンの形成方法

【課題】複数の物質層間の溶解度差を利用してダブルパターニングを具現する半導体素子の微細パターンの形成方法を提供する。

【解決手段】半導体素子の微細パターンの形成方法は、基板100上に、空間を介して相互に離隔されている複数の第1マスクパターン120を、基板100の主面と平行方向に形成するステップと、溶解剤に対して第1溶解度を有する第1物質からなる複数のキャッピング層130を、複数の第1マスクパターン120のそれぞれの側壁及び上面に形成するステップと、溶解剤に対して第1溶解度より低い第2溶解度を有する第2物質からなる第2マスク層を、空間内に形成するステップと、溶解剤を利用してキャッピング層130を除去し、かつ、第2マスク層の一部を除去した後、空間に残った第2マスク層の残留部分を、複数の第2マスクパターン140Aとして形成するステップと、を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】複数のライン状のパターンの端部におけるレジストパターン倒れ等の加工プロセスの問題を回避する。

【解決手段】 半導体基板上に被パターニング部材を形成した後に、被パターニング部材をパターニングして、複数のライン状のパターンを並列に形成するとともにライン状のパターンの端部から所定間隔をもってライン状のパターンの長手方向と垂直な方向にダミーパターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】低誘電率絶縁膜に形成される酸化層を薄膜化する技術を提供する。

【解決手段】半導体装置の製造方法は、基板上方に層間絶縁膜を形成する工程と、第1のエッチング工程及び第2のエッチング工程により層間絶縁膜にビアホールを形成する工程と、を備え、第2のエッチング工程は、層間絶縁膜のビアホールが形成される部分の側壁を平滑化するエッチング条件で実行される。

(もっと読む)

半導体装置の製造方法

【課題】配線間の層間絶縁膜に空洞を形成する場合における配線間の層間絶縁膜の高さの減少を抑制することを目的とする。

【解決手段】半導体装置の製造方法は、基板上方に第1の層間絶縁膜を形成する工程と、

第1の層間絶縁膜上に保護膜を形成する工程と、保護膜及び第1の層間絶縁膜に配線溝を形成する工程と、酸素を含む処理ガスを用いたプラズマ処理により、第1の層間絶縁膜の側面部分に酸化膜を形成する工程と、配線溝に金属膜を形成する工程と、研磨処理により、金属膜を部分的に除去することで配線溝に金属配線を形成する工程と、保護膜及び酸化膜の除去処理により、酸化膜を除去した部分に空間を形成する工程と、第1の層間絶縁膜、金属配線及び空間を覆うように第2の層間絶縁膜を形成する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】ポリマー残渣の発生と、エッチングプロセスの変動を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】Low−k膜II2の上面に、パターニングされたハードマスク層HMが形成される。ハードマスク層HMをマスクとしてLow−k膜II2にエッチングが施されてLow−k膜II2に配線用溝TRが形成される。配線用溝TR形成のためのエッチングを行なったチャンバーと同じチャンバー内でハードマスク層HMが除去されてLow−k膜II2の上面が露出される。

(もっと読む)

半導体装置の製造方法

【課題】Low−K膜へのダメージを抑制するとともに、フローが冗長化せずかつ微細化にも対応可能な半導体装置の製造方法を得ることを目的とする。

【解決手段】少なくとも1層以上の層間膜を備える半導体装置の製造方法であって、(a)層間膜であるLow−K膜102上に形成されたマスクを用いて層間膜にトレンチ開口部110を形成する工程と、(b)アッシングプロセスによりマスクを除去すると同時にビア開口部106およびトレンチ開口部110に側壁保護膜111を生成する工程を備える。さらに、(c)ビア開口部106およびトレンチ開口部110にCuを埋め込む工程を備えて構成される。

(もっと読む)

デュアルダマシンビア充填用組成物

デュアルダマシンプロセスに使用される組成物が開示される。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】製造効率を高めることができる半導体装置の製造方法等を提供する。

【解決手段】半導体装置1の製造方法は、絶縁層12のダイシング領域に溝部120を形成し、内部回路形成領域にビアホール126を形成する工程、絶縁層12上に第一のレジスト膜13を設ける工程、第一のレジスト膜13を覆う第二のレジスト膜14を設ける工程、第二のレジスト膜14の内部回路形成領域を覆う領域に配線用開口141を形成し第二のレジスト膜14のダイシング領域を覆う領域に位置合わせ用開口142を形成する工程、溝部120と位置合わせ用開口142との位置関係を検出し第二のレジスト膜14の配線用開口141が絶縁層12のビアホール126に対し所定の位置にあるかどうか検出する工程を含む。第二のレジスト膜14を選択的に除去する工程では、位置合わせ用開口142の領域が絶縁層12中の溝部120を覆うように位置合わせ用開口142を形成する。

(もっと読む)

61 - 80 / 196

[ Back to top ]