Fターム[5F033QQ02]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971) | 反射防止に関するもの (535)

Fターム[5F033QQ02]の下位に属するFターム

導電膜の反射防止膜を用いるもの (97)

絶縁膜の反射防止膜を用いるもの (242)

Fターム[5F033QQ02]に分類される特許

181 - 196 / 196

半導体装置及びその製造方法

【課題】 FSG膜と反射防止膜との界面で膜剥がれが生じない半導体装置及びその製造方法を提供する。

【解決手段】 基板上に酸化膜1を介してメタル膜2を形成する工程と、上記メタル膜上に反射防止膜3を形成する工程と、上記反射防止膜上にレジストパターン4を形成し、このレジストパターンをマスクとして上記反射防止膜及びメタル膜をエッチングし、複数個のメタル配線5を形成する工程と、上記メタル配線上及びメタル配線間にフッ素添加の酸化シリコン膜(FSG膜)からなる層間絶縁膜6を形成する工程と、上記層間絶縁膜の形成後に熱処理を行なう工程と、上記熱処理後に上記FSG膜上にTEOS膜7を形成する工程と、CMPにより上記TEOS膜またはTEOS膜及びFSG膜を研磨し上面を平坦化する工程と、平坦化された面にシリコン酸化膜8を形成する工程とを含むものである。

(もっと読む)

電子デバイス及び微細幅パターンの形成方法

【課題】 電子デバイス及び微細幅パターンの形成方法に関し、抜きパターンや残しパターンのいずれの場合もパターン分布の粗密に依存せずに所望の微細幅パターンを精度良く形成する。

【解決手段】 同じ線幅の孤立パターンの第1の凹部3と密パターンのn個の第2の凹部4とを設けた絶縁層2と、絶縁層2上に第1の凹部3及び第2の凹部4に対応する同じ線幅の第1の開口部6及び第2の開口部を有する第1の薄膜5と、第1の薄膜5上に、孤立パターンの第1の凹部3に対応する領域においては、第1の凹部3より広く且つ第2の凹部4のピッチの2倍と凹部の幅との差より狭い線幅の第3の開口部9を有するとともに、密パターンの第2の凹部4に対応する領域においては、第2の凹部4のピッチのn−1倍と凹部の幅との和より広く且つ第2の凹部4のピッチのn+1倍と凹部の幅との差より狭い線幅の第4の開口部10を有する第2の薄膜8とを備える。

(もっと読む)

デュアル・ダマシン配線及びその形成方法

【課題】 デュアル・ダマシン配線の形成方法を改善し、デュアル・ダマシン配線効率を向上させる新たなデュアル・ダマシン配線構造体を提供すること。

【解決手段】 デュアル・ダマシン相互接続構造体及び該構造体を形成する方法であり、該構造体はデュアル・ダマシン配線を誘電体層に含み、該デュアル・ダマシン配線は該誘電体層の厚さと比べて小さい距離にわたって該誘電体層内に延び、デュアル・ダマシン・ビア・バーは該デュアル・ダマシン配線の底面と一体になっており、かつ、該底面から該誘電体層の底面に向かって延びる。

(もっと読む)

配線の形成方法及び、電子デバイスの製造方法

【課題】 レジストパターンと反射防止膜との寸法変換差を小さくすることができるようにした配線の形成方法及び電子デバイスの製造方法を提供する。

【解決手段】

シリコン基板1上に形成されたポリシリコン膜13及びWS膜15を配線形状にパターニングして当該ポリシリコン膜13及びWS膜15からなるゲート配線10を形成する方法であって、ポリシリコン膜13及びWS膜15の上方にBARC膜21を形成し、このBARC膜21上にフォトレジストを塗布し、このフォトレジストを配線形状に露光し、現像処理してレジストパターン32を形成し、このレジストパターン32をマスクにBARC膜21をCHF3ガスとCF4ガスとO2ガスとからなる第1混合ガスでドライエッチングする。BARC膜21をドライエッチングする際に、BARC膜21のレジストパターン32で覆われた部分の側面にポリマー41を形成することができる。

(もっと読む)

ガス層形成材料

本発明は、アセナフチレンホモポリマー、アセナフチレンコポリマー、ポリ(アリーレンエーテル)、ポリアミド、B−ステージ多官能性アクリレート/メタクリレート、架橋スチレンジビニルベンゼンポリマー、およびスチレンとジビニルベンゼンとマレイミドまたはビス−マレイミドとのコポリマーから成る群から選択されるガス層形成材料を提供するものである。形成されたガス層はマイクロチップおよびマルチチップモジュールにおいて使用される。  (もっと読む)

(もっと読む)

アッシング処理方法及び基板処理方法

【課題】低誘電率材料からなる配線間絶縁膜が露出していても悪影響を及ぼすことなくアッシング処理を行うことを可能とし、近時の要請に対応した微細配線の実現に寄与する。

【解決手段】デュアルダマシン法により配線構造13を形成するに際して、配線間絶縁膜4を非熱揮発的絶縁材料である無機系ポーラス絶縁材料から形成する。レジストパターン10及び有機反射防止膜9をアッシング処理して除去する際に、配線間絶縁膜4の一部が露出していても、水の単独ガス又は水を含有する混合ガスをアッシングガスとして用いることでダメージを抑止する。

(もっと読む)

半導体装置の製造方法

【課題】上層配線に被覆されない接続孔を選択的に縮小させることにより、隣接する異電位配線とのショート不良を防止することを可能とする。

【解決手段】基板上に第1、第2絶縁膜18、19を形成する工程と、その上に有機犠牲層30と第1、第2マスク層31、32を順に形成する工程と、第2マスク層32に配線溝パターン33を形成する工程と、第2、第1マスク層32、31および有機犠牲層30に接続孔を形成するための接続孔パターン34を形成する工程と、第2、第1マスク層31、32をエッチングマスクに用いたエッチングにより第1マスク層31、有機犠牲層30に配線溝パターン33を形成し、第2絶縁膜19に接続孔35を形成する工程と、第1マスク層31、有機犠牲層30をマスクに用いて、第2絶縁膜19に配線溝36を形成し、第2、第1絶縁膜19、18に接続孔35を形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】 セルフアライン形成技術によりセルフアライン形成領域の絶縁膜に形成されたコンタクトホールの径に比較してさらに開孔幅の大きな穴部を絶縁膜の上部に形成するためセルフアライン形成領域を再度エッチング処理する必要があったとしても、セルフアライン形成領域内のセルフアラインマスク膜に悪影響が及ぼされることなく、さらにセルフアライン形成領域に対して複数回に分けて接続配線を埋込み形成する必要をなくす。

【解決手段】 領域CB2に対して第1のコンタクトホール16を形成した後、フォトレジスト38、塗布型酸化膜39、フォトレジスト40の3層構造の多層レジスト構造41を形成し、第5のシリコン酸化膜23の上部に穴部24および25を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 層間絶縁膜に低誘電率絶縁膜を用いた半導体作製の時、ハードマスクを用いて微細加工を行う製造方法を提供する。

【解決手段】 半導体に低誘電率絶縁膜13を適用して低誘電率絶縁膜13とその下層のエッチングストッパー膜12を加工する時、まずレジスト15aをマスクとしたハードマスク膜14のエッチングを行い、続いてレジスト15aをH2とHeの混合ガスで200℃より高い高温、1Torr付近の圧力の条件でアッシングを行う。このようにすればレジスト除去においてハードマスク膜14aにダメージを与えることなく続く低誘電率絶縁膜13のエッチングにおいてファセットの少ないハードマスクによる微細加工が可能となる。

(もっと読む)

感光性誘電体層を分解することによる相互接続構造の形成

本発明は、感光性材料の層が直接にパターン化される方法を提供する。その後、感光性材料は、少なくとも部分的に分解され、層内にボイドまたは空隙を残し、低減された抵抗キャパシタンス遅延特性を有する低誘電率の層を提供する。  (もっと読む)

(もっと読む)

アモルファス炭素膜のCVD堆積用の液体前駆体

アモルファス炭素材料を堆積するための方法が提供される。一態様では、本発明は、処理チャンバに基板を位置決めするステップと、該処理チャンバに処理ガスを導入するステップであって、該処理ガスがキャリアガス、水素および1つ以上の前駆体化合物を含むステップと、二重周波数RF源から電力を印加することによって該処理ガスのプラズマを生成するステップと、該基板上にアモルファス炭素層を堆積するステップとを含む基板処理方法を提供する。 (もっと読む)

アモルファスカーボン膜を含む構造およびその形成方法。

【課題】 アモルファスカーボン膜を有する構造およびその形成方法を提供することである。

【解決手段】 半導体デバイスは、半導体基板と、半導体基板上に形成され、被処理膜を有する膜スタックとを含む。膜スタックに含まれるデュアルハードマスクは、アモルファスカーボン層、およびアモルファスカーボン層と被処理膜との間に配置される下層のハードマスク層を有し、ハードマスク層は、アモルファスカーボン層を含まない。金属配線のためのダマシン構造は、膜スタックに形成されている。アモルファスカーボン膜は、例えば、シングルダマシン構造またはデュアルダマシン構造の中で取り入れられることができる。アモルファスカーボン膜は、配線構造を形成するためのリソグラフィマスクの一部として役に立つことができ、または、それは、CMPの間、デュアルハードマスク、ケミカルメカニカルポリシング(CMP)ストップ層または犠牲層の上部層として役立つことになる。

(もっと読む)

無定形炭素層を含むマスキング構造

多数層を有するマスキング構造が形成される。そのマスキング構造は、無定形炭素層と該無定形炭素層上に形成されたキャップ層とを含む。無定形炭素層は透明無定形炭素を含む。キャップ層は非酸化物材料を含む。マスキング構造は、半導体装置の製作中、エッチング・プロセスにおけるマスクとして使用可能である。 (もっと読む)

ビア・ファースト・デュアルダマシン相互接続配線形成のための構造体充填方法

厚さが溶剤により容易に制御できる間隙充填底部反射防止膜を用いたビア・ファースト・デュアルダマシン相互接続構造体を形成する方法である。基板に塗布後、底部反射防止膜は低温焼成により部分硬化される。次に皮膜したウェハ上に溶剤を施し、膜と一定時間接触させて置く。底部反射防止膜の焼成温度と溶剤との接触時間により制御できる速さで溶剤が底部反射防止膜を除去しつつも、薄い底部反射防止膜を作り誘電体積層上に最適の光吸収特性は維持される。本方法の別の実施例では底部反射防止膜を充分除去し、ビアを単に部分充填し、続く処理工程でビア底部が保護されるようにしてもよい。溶剤はウェハから除去され、底部反射防止膜は高温焼成処理により完全に硬化される。次にウェハはフォトレジストにより被覆されトレンチパターンが露出する。使用される底部反射防止膜材によりトレンチパターン形成上、より平坦な表面形状が維持され、誘電体積層上に無機光吸収材層を設ける必要がなくなり、トレンチのエッチング工程時ビアの底部を保護し、溶剤を用いてビアの厚さを制御することにより境界問題の発生を防止する。 (もっと読む)

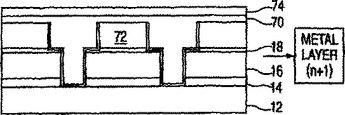

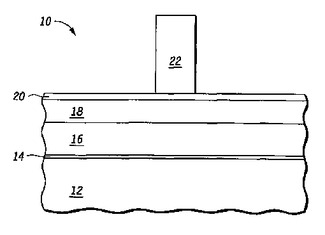

有機反射防止膜(ARC)を有する半導体装置及びその方法

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

デュアルダマシンによる半導体装置の製造方法

【課題】 放熱性が良好で、製造コストが低く、微細加工に好適なデュアルダマシンによる半導体装置の製造方法を提供する。

【解決手段】 基板1上に無機層間膜5、有機層間膜6、シリコン酸化膜からなる下部マスク7、シリコン窒化膜からなる上部マスク8を形成し、上部マスク8上にシリコン酸化窒化膜からなり膜厚が20乃至100nmであるカバーマスク10を形成する。そして、反射防止膜11及びレジスト膜12を形成する。次に、レジスト膜12をマスクとして、反射防止膜11、カバーマスク10、下部マスク7をエッチングする。そして、カバーマスク10をマスクとして、有機層間膜6及び無機層間膜5をエッチングしてビアホールを形成する。次に、上部マスク8をマスクとして有機層間膜6をエッチングして配線溝を形成する。

(もっと読む)

181 - 196 / 196

[ Back to top ]