Fターム[5F033QQ02]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971) | 反射防止に関するもの (535)

Fターム[5F033QQ02]の下位に属するFターム

導電膜の反射防止膜を用いるもの (97)

絶縁膜の反射防止膜を用いるもの (242)

Fターム[5F033QQ02]に分類される特許

21 - 40 / 196

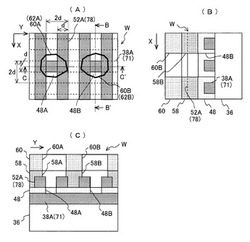

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

微細パターンの形成方法

【課題】側壁部の形成の基礎となるパターンをレジストにより形成する場合であっても、側壁部の傾きを抑制できる微細パターンの形成方法を提供する。

【解決手段】基板上に形成されたエッチング対象層の上に有機膜を形成する有機膜形成ステップと、有機膜上にレジスト膜を形成し、このレジスト膜をパターニングするパターニングステップと、パターニングされたレジスト膜から露出する有機膜と、パターニングされたレジスト膜とを覆うように酸化シリコン膜を常温にて堆積する堆積ステップと、基板を加熱して酸化シリコン膜に引っ張り応力を生じさせる加熱ステップと、処理ステップの後に、パターニングされたレジスト膜の側壁に酸化シリコン膜が残るように当該酸化シリコン膜をエッチングする第1のエッチングステップと、パターニングされたレジスト膜を除去する除去ステップとを含む、微細パターンの形成方法が開示される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】歩留まりに優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、基板内の記憶回路領域に形成されており、多層配線層内に埋め込まれた少なくとも1以上の容量素子および周辺回路を有する記憶回路と、平面視において、基板内の憶回路領域とは異なる領域である論理回路領域に形成された論理回路と、を備え、容量素子は、下部電極、容量絶縁膜、上部電極、埋設電極および、上部接続配線で構成されており、上部接続配線と埋設電極とは、同一の材料かつ一体に構成されており、上部接続配線と下部電極との間には、論理回路を構成する前記配線が少なくとも1以上設けられており、上部接続配線の上面と、上部接続配線と同じ配線層に形成された論理回路を構成する配線の上面とが、同一面を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】下層の金属配線のダメージがなく上層の金属配線が形成され、かつ、配線間の寄生容量が低減された半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板上に設けられた第1の金属配線層と、

前記第1の金属配線層上に設けられ、該第1の金属配線層の金属の拡散を防止する拡散防止膜と、前記拡散防止膜上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられた、前記拡散防止膜と同じ材料からなる第2の絶縁膜と、前記第2の絶縁膜上に設けられた第3の絶縁膜と、前記拡散防止膜、前記第1の絶縁膜、前記第2の絶縁膜及び前記第3の絶縁膜に形成された接続孔に充填され、前記第1の金属配線層に電気的に接続された第2の金属配線層と、を備えたことを特徴とする。

(もっと読む)

パターン形成方法

【課題】ダブルパターニング法を用いる場合にパターンの疎密に拘わらず、所望のパターンを形成できるようにする。

【解決手段】第1のレジスト膜に第1の露光光を照射し第1の現像を行なうことにより、配線溝パターンを含む第1の領域Aに第1パターン5aを形成すると共に、第1の領域Aと接続され且つ配線溝パターンと比べてパターン密度が疎である第2の領域Bにダミーパターン5bを形成する。その後、第1のレジスト膜を硬化し、硬化した第1のレジスト膜の上に、第2のレジスト膜9を形成する。その後、第2のレジスト膜9に第2の露光光を照射し第2の現像を行なうことにより、第1の領域Aに第2パターン9aを形成する。該第2パターン9aを形成する際に、第1の領域Aには、第1パターン5a及び第2パターン9aにより配線溝パターン2aが形成される一方、第2の領域Bは、ダミーパターン5bの開口部が第2のレジスト膜9によって埋められる。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】アモルファスカーボン膜3及びシリコン酸窒化膜4からなる被エッチング部材上に塗布膜5をスピン塗布法により成膜し、塗布膜5をパターニングすることによってサイドウォールコアを形成し、サイドウォールコアの少なくとも側面を覆うシリコン酸化膜7を成膜し、シリコン酸化膜7上に有機反射防止膜8をスピン塗布法により成膜する。次いで、有機反射防止膜8をエッチングすることによって、シリコン酸化膜7の凹部7aを覆う埋込マスクを形成し、シリコン酸化膜7をエッチングすることにより、サイドウォールコアまたは埋込マスクと重ならない被エッチング部材を露出させ、被エッチング部材をエッチングすることでフォトリソグラフィー解像限界未満のパターンを得る。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】配線溝パターンの深さを精密に制御でき、かつ当該配線溝パターンのダメージ形成を抑制できる半導体装置の製造方法を提供する。

【解決手段】拡散防止膜ADF上に、第2の低誘電率膜LOWK2c、第3の低誘電率膜LOWK3c、マスク層となるべき膜がこの順に積層される。マスク層となるべき膜をエッチングし、底面が第3の低誘電率膜LOWK3cの表面により構成される配線溝パターンを形成することにより、マスク層SIO2dが形成される。アッシング処理により第1のレジストマスクが除去される。マスク層の配線溝パターンを用いて、底面が第2の低誘電率膜LOWK2cとなるように、配線溝TRCHが形成される。充填される銅金属CUaの頂面から第3の低誘電率膜LOWK3cまでの層がCMP法により除去される。上記各低誘電率膜はFSGよりも誘電率が低く、第2の低誘電率膜LOWK2cは第3の低誘電率膜LOWK3cよりも誘電率が低い。

(もっと読む)

半導体装置の製造方法

【課題】セルアレイ内部とセルアレイの端部とでパターンを均一に形成できる半導体装置の製造方法を提供すること。

【解決手段】 本発明は、第1の領域と第2の領域とが画定された基板上にエッチング対象層を形成するステップと、該エッチング対象層上に第1の開口を有する第1の感光膜パターンを形成するステップと、該第1の感光膜パターンの表面に遮光膜を形成するステップと、該遮光膜が形成された第1の感光膜パターン上に、前記第1の領域と第2の領域とを同時に露光して複数の第2の開口を有する第2の感光膜パターンを形成するステップと、前記第1の感光膜パターンと第2の感光膜パターンとをエッチングバリアとして、前記エッチング対象層をエッチングして複数のパターンを形成するステップとを含むことを特徴とする。

(もっと読む)

電極構造体及びその製造方法、並びに半導体装置

【課題】精度良く形成された小型化された電極を備えた電極構造体及びその製造方法、並びに半導体装置を提供する。

【解決手段】第1の層間絶縁膜13に、第1の方向に延在する複数の第1の溝16を形成し、第1の溝16の対向する2つの側面及び底面を覆うように第1の導電膜32を形成し、第1の導電膜32が形成された複数の第1の溝16を第1の絶縁膜19で充填し、第1の層間絶縁膜13、第1の絶縁膜19、及び第1の導電膜32の上面に、第2の方向に延在する複数の開口部を有したハードマスク層33を形成し、異方性エッチング法により、複数の開口部から露出された部分の第1の絶縁膜19及び第1の導電膜32を除去することで、第1の溝16に第1の導電膜32よりなる電極を形成すると共に、第1の層間絶縁膜13に第1の溝16と交差する第2の溝17を複数形成し、ハードマスク層33を除去した後、第2の溝17を第2の絶縁膜21で充填する。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

半導体装置の製造方法及びフォトマスク

【課題】半導体記憶装置の製造において、パターン間隔を縮小し、レジスト膜厚、エッチング量等のバラツキに対応する。

【解決手段】半導体装置の製造方法は、基板上に被加工膜を形成する工程(a)、被加工膜上にレジスト膜を形成する工程(b)、フォトマスクのマスクパターン200bをレジスト膜に転写パターン200cとして転写する工程(c)、転写パターン200cを加工する工程(d)を含む。転写パターン200cは、所定間隔を開けて端部同士が対向して直列に並ぶ第1及び第2の転写ラインパターン201c及び202cと、これらに各々並列する第3及び第4の転写ラインパターン203c及び204cと、第2及び第3の転写ラインパターン202c及び203cの端部同士を接続する接続部212とを含む。工程(d)にて、接続部212の少なくとも一部を除去し、第2及び第3の転写ラインパターン202c及び203cを分離する。

(もっと読む)

リソグラフィー用洗浄液及び配線形成方法

【課題】ILD材料に対する腐食抑制機能に優れ、かつ、レジスト膜及び下層反射防止膜の除去性能にも優れたリソグラフィー用洗浄液、及びこのリソグラフィー用洗浄液を用いた配線形成方法を提供する。

【解決手段】本発明に係るリソグラフィー用洗浄液は、4級アンモニウム水酸化物と、水溶性有機溶剤と、水と、無機塩基とを含有する。水溶性有機溶剤は、双極子モーメントが3.0D以上である高極性溶剤と、グリコールエーテル系溶剤と、多価アルコールとを含み、上記高極性溶剤とグリコールエーテル系溶剤との合計含有量が、全量に対して30質量%以上である。

(もっと読む)

半導体装置の製造方法

【課題】ビア等となる開口内への金属の埋設において、ボイドの発生を抑制することを課題とする。

【解決手段】基板上に形成された第2のp−SiCOH膜204の直上に、ハードマスクとしてTiN膜205を形成する工程と、フォトリソグラフィーとエッチングにより、TiN膜205および第2のp−SiCOH膜204を貫く開口を形成する工程と、前記開口内を洗浄する工程と、前記洗浄工程の後、TiN膜205を除去する工程と、TiN膜205を除去後、第2のp−SiCOH膜204の直上に、前記開口を埋める第2の金属膜214を形成する工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法、半導体装置、及び半導体製造装置

【課題】有機シリカ膜を成膜したのちのプラズマ反応室の内壁のクリーニング時間を短縮する。

【解決手段】まずプラズマ反応室内壁をプリコート膜で被覆する(プリコート工程)。次いで基板上に、シリコン炭素組成比(C/Si)が1以上である有機シリカ膜を成長させる(基板処理工程)。次いで、基板を取り出した後、プラズマ反応室内壁に付着した有機シリカ膜とプリコート膜とをプラズマを用いて除去する(クリーニング工程)。プリコート膜としては、基板上に成膜された有機シリカ膜よりも少なくとも炭素含有率が低い有機シリカ膜である高酸素含有プリコート膜を用いる。

(もっと読む)

ハードマスク材料

【課題】集積回路製造工程のバックエンドプロセス、およびフロントエンドプロセスにおいて利用することができる、高硬度、且つ低応力のハードマスク膜を提供する。

【解決手段】ハードマスク膜は、応力が約−600MPaから600MPaの範囲内であり、硬度は少なくとも約12Gpaである。ハードマスク膜は、PECVD処理チャンバにおいて、高密度化プラズマ後処理を複数回行うことによって、ドープ済または未ドープのシリコンカーバイドの副層を複数成膜することによって得られる。ハードマスク膜は、SixByCz、SixByNz、SixByCzNw、BxCy、およびBxNyから成る群から選択される高硬度のホウ素含有膜を含む。ハードマスク膜は、ゲルマニウム含有率が少なくとも約60原子パーセントと、ゲルマニウム含有率が高いGeNxハードマスク材料を含む。

(もっと読む)

パターン形成方法及びパターン形成装置

【課題】生産性に優れたパターン形成方法及びパターン形成装置を提供することを目的とする。

【解決手段】被加工膜上の第1の領域に第1のパターン被覆率である第1のパターンを形成する工程と、第1の領域とは異なる被加工膜上の第2の領域に第2のパターン被覆率である第2のパターンを形成する工程と、を含む。第2のパターンを形成する工程は、ブロックコポリマー含有膜またはポリマー混合膜からなる第2の膜を被加工膜上に形成する工程と、第2の膜を自己組織化する工程と、自己組織化された第2の膜に含有される複数種のポリマーを、少なくとも1種類のポリマーを残すように選択的に除去することにより、第2のパターン被覆率を第1のパターン被覆率に近づけるように第2のパターンを第2の領域に形成する工程と、を有する。

(もっと読む)

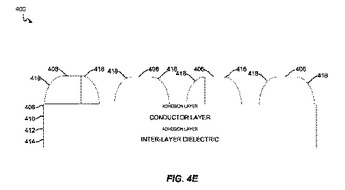

4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いたメモリ線および構造を形成する装置および方法

本発明は、4倍ハーフピッチレリーフパターニングのための双側壁パターニングを用いてメモリ線および構造を製作する装置、方法およびシステムを提供する。本発明は、基板の上方に配される第1のテンプレート層からフィーチャを形成することと、フィーチャに隣接してハーフピッチの側壁スペーサを形成することと、ハーフピッチの側壁スペーサをハードマスクとして用いることによって第2のテンプレート層内により小さいフィーチャを形成することと、より小さいフィーチャに隣接して4分の1ピッチの側壁スペーサを形成することと、4分の1ピッチの側壁スペーサをハードマスクとして用いることによって導体層から導体フィーチャを形成することとを含む。多数の追加の態様が開示される。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いて銅の埋め込み配線および接続プラグを形成するとき、接続プラグ中のボイド発生を防止する。

【解決手段】 Low−k膜13、15、ELK膜14、TEOS膜16からなる層間絶縁膜にプラグとなる接続孔19aを形成した後、酸素プラズマ処理を行って変質層20を形成し、この層を薬液処理により選択的に除去すると、ELK膜14が多孔質であることに起因してその側壁21にLow−k膜13、15などより大きい角度のテーパーが形成される。次に配線埋め込み用の溝の底面がELK膜14中にくるように形成して、プラグ開口の入口が広がる形状にした後、銅膜を埋め込む。

(もっと読む)

21 - 40 / 196

[ Back to top ]