Fターム[5F033QQ02]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 露光 (971) | 反射防止に関するもの (535)

Fターム[5F033QQ02]の下位に属するFターム

導電膜の反射防止膜を用いるもの (97)

絶縁膜の反射防止膜を用いるもの (242)

Fターム[5F033QQ02]に分類される特許

41 - 60 / 196

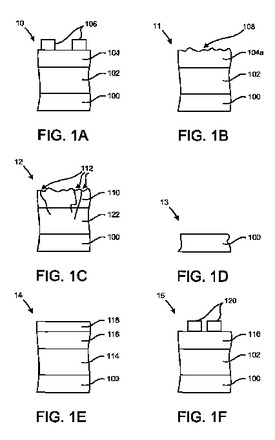

基板上のシリコン含有反射防止コーティング層の再加工方法

半導体デバイス製造においてシリコン含有反射防止コーティング(SiARC)層を有する膜構造を再加工する方法が供される。当該方法は、上にSiARC層を有する膜積層体を含む基板、及び、前記SiARC層上に形成されるレジストパターンを供する工程を有する。当該方法はさらに、前記SiARC層から前記レジストパターンを除去する工程、前記SiARC層を、オゾン(O3)気体を含む処理気体に曝露することで、前記SiARC層を改質する工程、希釈フッ化水素(DHF)液体によって前記の改質されたSiARC層を処理する工程、及び、遠心力により、前記基板から前記の改質されたSiARC層を除去する工程を有する。  (もっと読む)

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPにおいて、側壁部の形状の対称性を高め、被エッチング膜をエッチングするときの加工精度を向上させることができるマスクパターンの形成方法を提供する。

【解決手段】基板上の被エッチング膜の上に形成されたシリコン膜よりなる第1のライン部が配列したシリコン膜パターンの表面を等方的に被覆するように、カーボン膜を成膜する成膜工程S18と、カーボン膜を第1のライン部の上部から除去すると共に、第1のライン部の側壁部として残存するように、カーボン膜をエッチバックするエッチバック工程S19と、第1のライン部を除去し、側壁部が配列したマスクパターンを形成するシリコン膜除去工程S20とを有する。

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPによりマスクパターンを形成する場合に、反射防止膜のエッチング工程を省略し、マスクパターンのパターン倒れを防止することができるマスクパターンの形成方法を提供する。

【解決手段】レジストパターン列の表面を等方的に酸化シリコン膜で被覆するステップS14と、レジストパターン列の間をカーボン膜で埋め込むと共に、上部をカーボン膜で被覆するステップS15と、カーボン膜を、レジストパターン列の上部から除去すると共に、レジストパターン列の間に残存するようにエッチバック処理するステップS16と、残存するカーボン膜を除去すると共に、レジストパターン列の上部を被覆する酸化シリコン膜をエッチバック処理するステップS17と、レジストパターン列をアッシング処理し、中央部と、中央部を両側から挟む膜側壁部とを有する、酸化シリコン膜よりなる第1のマスクパターン列を形成するステップS18とを有する。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、通常のコンタクトとシェアードコンタクトとを同時に形成することが難しくなり、接合リーク不良やコンタクト抵抗の上昇が発生する等の課題があった。

【解決手段】ロジックSRAM部のゲート配線6の側壁に形成するサイドウォール9と、拡散層11の表面に形成するシリサイド層13とゲート配線6のシリサイド層15とを電気的に接続するドープトポリシリコン18と、ドープトポリシリコン18と第1層アルミ配線とを電気的に接続するWプラグ26と、ロジックSRAM部の拡散層11の表面のシリサイド層と第1層アルミ配線とを電気的に接続するWプラグ25とを備えるものである。

(もっと読む)

半導体装置の製造方法及び露光装置

【課題】フォーカス値の測定時間を短縮し、かつ正確なフォーカス値を得ることができる半導体装置の製造方法及び露光装置を提供する。

【解決手段】半導体装置の製造方法は、ウエハ3上に形成されたレジスト6より下層に形成された膜によって反射率が異なる領域について測定されたフォーカス値を取得し、反射率が低い第1の領域31について得られたフォーカス値に、前記第1の領域31よりも反射率が高い第2の領域32について得られたフォーカス値を近づけて露光処理を行う。

(もっと読む)

半導体装置とその製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上のコンタクトと柱状半導体層の周囲に形成されるゲート電極のショートの抑制。

【解決手段】上方に平面状半導体層及び該平面状半導体層上の柱状半導体層が形成された基板に対して、柱状半導体層の上部に第2のドレイン/ソース領域を形成し、コンタクトストッパー膜を成膜し、コンタクト層間膜を成膜し、第2のドレイン/ソース領域上にコンタクトを形成し、ここでコンタクトの形成は、コンタクトのパターンを形成し、コンタクトのパターンを用いてコンタクト層間膜をコンタクトストッパー膜までエッチングすることにより、コンタクト用のコンタクト孔を形成し、コンタクト用のコンタクト孔の底部に残存するコンタクトストッパー膜をエッチングにより除去することを含み、コンタクト用のコンタクト孔の底面の基板への投影面は、柱状半導体層の上面及び側面に形成されたコンタクトストッパー膜の基板への投影形状の外周内に位置する。

(もっと読む)

半導体装置の製造方法。

【課題】 金属膜やHigh−k膜の膜質の劣化を抑制できる半導体装置の製造方法を提供すること。

【解決手段】 第1の薄膜2上に、第1の薄膜2とは異なる第2の薄膜3を形成し、第2の薄膜3上に、第2の薄膜3とは異なる膜からなる犠牲膜5を形成し、犠牲膜5をエッチングにより所望の間隔を持つパターンに加工し、犠牲膜パターンを形成し、シリコン含有プリカーサー、酸素含有ガスを基板上に間欠的に供給して、犠牲膜パターンにシリコン酸化膜6を被覆し、シリコン酸化膜6をエッチングにより犠牲膜5の側壁上に側壁スペーサー6aを形成し、犠牲膜5を除去し、側壁スペーサー6aをマスクとして用いて第1の薄膜2および第2の薄膜3を加工する。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

有機質物除去方法

【課題】半導体基板に存在する、ドライエッチング後に生成する硬化したレジスト膜、その下層に残留するBARC膜、及びドライエッチング残渣等の除去において、アッシング処理を行わずに除去する方法を提供する。

【解決手段】半導体製造プロセスにおいて基板上に形成される有機質物膜および/またはその膜をエッチングおよび/または研磨した際に生成する有機残渣に、1〜500mW/cm2の照射強度の真空紫外線を、大気中、2mm以下の距離で照射することを特徴とする有機質物除去方法。

(もっと読む)

液処理装置及び液処理方法

【課題】新たな手法を用いて基板の表面から膜を除去する液処理装置等を提供する。

【解決手段】第1の膜の上層に第2の膜が形成された基板から、第1の膜及び第2の膜を除去する液処理装置3において、第1の薬液供給部51は基板Wに第1の膜を溶解させるための前記第1の薬液を供給し、第2の薬液供給部51は前記第2の膜の強度を低下させるための第2の薬液を供給し、衝撃供給部としての機能を兼ねる流体供給部52は第2の膜に物理的衝撃を与えて当該第2の膜を破壊すると共に破壊された第2の膜の破片を流し去るための流体を供給する。制御部7は第2の薬液を供給し、次いで前記流体供給部52から流体を供給した後、第1の薬液を供給するように各部を制御する。

(もっと読む)

半導体装置の製造方法

【課題】低コストで微細パターンを形成可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、被加工体10上に第1のレジスト11を形成し、第1のレジスト11をパターニングする工程と、第1のレジスト11のパターニングの後、被加工体10上に第2のレジスト12を形成し、第2のレジスト12に対する選択的露光、ベーク及び現像を行い、その現像時に被加工体10上に残っている第1のレジスト11を除去するとともに、第2のレジスト12の一部を選択的に除去して、第2のレジスト12をパターニングする工程と、パターニングされた第2のレジスト12をマスクにして被加工体10を加工する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【目的】キャップ成膜時に起因するlow−k膜の絶縁性劣化を低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に絶縁材料を用いたキャップ膜を形成する工程(S106)と、前記キャップ膜を形成した後に、前記キャップ膜を介して前記前記キャップ膜の下層のシリル化処理を行なう工程(S108)と、前記シリル化処理の後、エッチング法を用いて、前記キャップ膜上から前記絶縁膜内へと続く開口部を形成する工程(S114)と、前記開口部に導電性材料を堆積させる工程(S124)と、を備えたことを特徴とする。

(もっと読む)

基板処理方法

【課題】半導体デバイスの小型化要求を満たす寸法の開口部をマスク層又は中間層に形成することができる制御性に優れた基板処理方法を提供する。

【解決手段】アモルファスカーボン膜51、SiON膜52,BARC膜53及びフォトレジスト膜54が順に積層されたウエハWを処理する基板処理方法であって、CHF3ガスと、CF3Iガスと、H2ガス及びN2ガスの混合ガスから生成されたプラズマによって、フォトレジスト膜54の開口部55のCD値を縮小しつつ開口部底部のSiON膜をエッチングするシュリンクエッチングステップと、開口部55の側壁面へのデポの堆積を促進させて各CD値のばらつきを吸収するばらつき吸収ステップと、開口部の内面に薄膜を形成して各開口部の開口幅を縮小させる開口幅縮小ステップとを1ステップで行う。

(もっと読む)

ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法

【課題】 ポリマの指向性自己組織化を利用するサブリソグラフィ構造の形成方法を提供する。

【解決手段】 ブロック・コポリマの自己組織化を含む方法であって、目標とするCD(限界寸法)を有する開口部(1つ又は複数の基板内の)から開始して、ホールを規則的な配列又は任意の配列に形成する方法を説明する。重要なことに、形成されたホールの平均直径の百分率ばらつきは、最初の開口部の平均直径の百分率ばらつきより小さくなる。形成されたホール(又はビア)を下層の基板に転写することができ、次にこれらのホールを金属導体のような材料で埋め戻すことができる。本発明の好ましい態様は、22nm以下の技術ノードにおいても、より狭いピッチ及びより優れたCDの均一性を有するビアの作成を可能にする。

(もっと読む)

ブロック共重合体を用いてホール又はビアを有するデバイスを形成する方法

【課題】 ブロック共重合体を用いて所定の位置にホール又はビアを有するデバイスを形成する方法を提供する。

【解決手段】 例えば、光リソグラフィを用いて、輪郭を付けられた凸状のセグメントによって与えられる断面を有する開口部を基板内に形成する。開口部の断面は、例えば、重なった円形領域によって与えることができる。側壁は、種々の点で隣接し、そこで突起を画定する。ブロック共重合体を含むポリマーの層を開口部及び基板の上に塗布し、自己集合させる。開口部内に個別分離ドメインが形成され、これらを除去してホールを形成し、これを下層の基板に転写することができる。これらのドメイン及びこれらの対応するホールの位置は、側壁及びそれらに付随する突起によって所定の位置に誘導される。これらのホールを隔てる距離は、何も側壁がない場合にブロック共重合体(及び何れかの添加剤)が自己集合したとする場合よりも大きく又は小さくすることができる。

(もっと読む)

半導体装置の製造方法

【課題】複数の同種の製造装置を用いて半導体装置を製造する場合に、製品間での寸法のばらつきの発生を抑制できる技術を提供する。

【解決手段】制御機器CDをそれぞれの露光機に対して個別に配置する。露光処理が完了した各ロットは、どの露光機で露光処理がなされたかによって分類され、露光機毎に、露光機を調整するためのパラメータが製品情報収集部CD1に収集され、最適製造条件計算部CD2にて処理条件が計算され、計算された処理条件が設定される。すべてのロットは、露光処理を行う露光機が予め割り当てられ、露光処理が済んでいないロットは、分類機CMによって割り当てられた露光機へ振り分けられ、制御機器CDによって求められた処理条件で露光処理が行われる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】第2絶縁層にビアとなる接続孔を形成するときにビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。エッチングストッパー膜200は、第1絶縁層120上、エアギャップ128上、及び配線162上に形成されている。第2絶縁層220はエッチングストッパー膜200上に形成されている。ビア262は第2絶縁層220に埋め込まれており、配線162に接続している。そしてエッチングストッパー膜200は、エアギャップ128上に位置する部分202が、配線162上に位置する部分より厚い。

(もっと読む)

プラズマエッチング方法、プラズマエッチング装置および記憶媒体

【課題】高速電子による有機膜の改質効果を十分に発揮することができるプラズマエッチング方法を提供すること。

【解決手段】プラズマエッチングによりエッチング対象膜にホールを形成するにあたり、プラズマ生成用高周波電力印加ユニットをオンにして処理容器内にプラズマを生成する第1条件と、プラズマ生成用高周波電力印加ユニットをオフにして処理容器内のプラズマを消滅させる第2条件とを交互に繰り返し、第1の直流電源から、第1条件の期間よりも第2条件の期間のほうが印加電圧の絶対値が大きくなるように負の直流電圧を印加する。

(もっと読む)

半導体装置及びその製造方法

【課題】導電プラグの酸化を抑止し、コンタクト抵抗の安定化された信頼性の高い半導体装置を実現する。

【解決手段】下部電極101と上部電極103とで強誘電体膜102を挟持してなる強誘電体キャパシタ構造100と、導電プラグ110との間に、酸化しても導電性を有する導電材料(例えば金属)からなる導電層112を形成し、ここでは、導電プラグ110の下地膜を導電層112(Ag,Ni,Cu,Zn,In,Sn,Ir,Ru,Rh,Pd,Osから選ばれた少なくとも1種を材料として形成される。)とする。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ法の露光解像限界を超えた寸法を有するパターンの形成において、工程数を削減し、製造コストを抑えることができる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様は、被加工膜2上に、被加工膜2を加工する際のマスク材となる膜をCVD法によって形成するに当って、第1の温度条件でマスクとして機能する第1の領域3を形成し、第1の領域3上に、同一チャンバー内にて第1の温度条件を変えた第2の温度条件で反射防止膜として機能する第2の領域4を形成し、第1および第2の領域3、4からなる第1のマスク材膜5を形成する工程を含む半導体装置の製造方法を提供する。

(もっと読む)

41 - 60 / 196

[ Back to top ]