Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

761 - 780 / 898

CMOSFET内の歪みを最適化するための構造体及び方法

【課題】 CMOSFET内の歪みを最適化するための構造体及び方法を提供すること。

【解決手段】 MOSFET内の歪みを最適化し、より具体的には、1つの種類(P又はN)のMOSFET内の歪みを最大にし、かつ、別の種類(N又はP)のMOSFET内の歪みを最小にし緩和する、PMOSFET及びNMOSFETの両方を含む歪みMOSFETの半導体構造体、及び歪みMOSFETを製造する方法が開示される。元の完全な厚さを有する歪み誘起CA窒化物コーティングが、PMOSFET及びNMOSFETの両方の上に形成され、この歪み誘起コーティングは、1つの種類の半導体デバイス内に最適化された十分な歪みをもたらし、別の種類の半導体デバイスの性能を劣化させる。歪み誘起CA窒化物コーティングは、別の種類の半導体デバイスの上で減少した厚さまでエッチングされ、減少した厚さの歪み誘起コーティングは、他方のMOSFET内でより少ない歪みを緩和し、他方のMOSFET内により少ない歪みをもたらす。

(もっと読む)

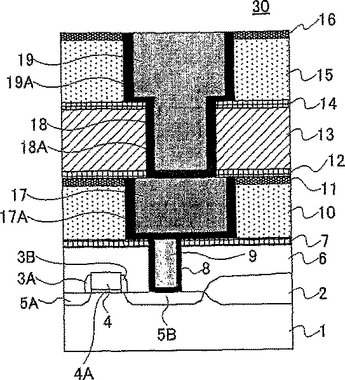

半導体装置およびその製造方法

【課題】配線層の第1絶縁膜に対して選択的にエッチングできるもので接続孔が形成される第2絶縁膜を形成することで、配線信頼性の高い多層配線構造を有する半導体装置を可能とする。

【解決手段】第1絶縁膜11と、前記第1絶縁膜11に形成されたもので第1配線21上のみにバリア膜22が形成された第1配線21と、前記第1配線21を被覆して前記第1絶縁膜11上に形成されかつ接続孔23が形成された第2絶縁膜12とを有し、前記第2絶縁膜12の前記第1絶縁膜11側は、前記第1絶縁膜11に対して選択的にエッチング可能なものである。

(もっと読む)

成膜方法、半導体装置の製造方法、半導体装置および成膜装置

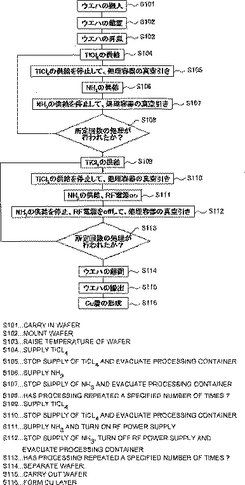

処理容器内の被処理基板に成膜する成膜方法であって、ハロゲン元素を含まない有機金属化合物からなる第1の原料ガスを前記処理容器内に供給した後、前記第1の原料ガスを前記処理容器内から除去する第1の工程と、水素または水素化合物を含む第2の原料ガスを前記処理容器内に供給した後、前記第2の原料ガスを前記処理容器内から除去する第2の工程とを繰り返してなる第1の膜成長工程と、金属ハロゲン化物からなる第3の原料ガスを前記処理容器内に供給した後、前記第3の原料ガスを前記被処理基板から除去する第3の工程と、水素または水素化合物を含む第4の原料ガスを前記処理容器内に供給した後、前記第4の原料ガスを前記処理容器内から除去する第4の工程とを繰り返してなる第2の膜成長工程からなる成膜方法を用いた。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】金属薄膜抵抗体を備えた半導体装置の製造方法において、金属薄膜抵抗体の上面への酸素プラズマの照射を防止しつつ、金属薄膜抵抗体と金属配線パターンの電気的接続を確実に形成する。

【解決手段】下地絶縁膜5上に配線パターン11を形成し、下地絶縁膜5上に絶縁膜19を形成し、絶縁膜19に、金属薄膜抵抗体の両端部の形成予定領域及び配線パターン11に対応して接続孔21を形成し、接続孔21内を含み絶縁膜19上に金属薄膜37を形成し、さらにその上に保護膜43を形成し、21接続孔の形成領域にも金属薄膜37及び保護膜43を残存させるように、保護膜43上にレジストパターン39を形成し、異方性エッチング技術によりレジストパターン39をマスクにして保護膜43及び金属薄膜37をパターニングして保護膜パターン41及び金属薄膜抵抗体23からなる積層パターンを形成し、その後、レジストパターン39を除去する。

(もっと読む)

半導体装置

多層配線構造を有する半導体装置において、Cuビアプラグ部への応力集中を抑制する多層配線構造を提供する。そのため、Cu配線部を含む第1の絶縁層と、前記基板上に形成された、前記Cu配線に電気的に接続されるCuビアプラグ部を含む第2の絶縁層とを有し、前記第1の絶縁層は弾性率が5GPa以上、硬度が0.6GPa以上である多孔質絶縁膜からなり、前記第2の絶縁層の弾性率が10GPa以上、硬度が1GPa以上であることを特徴とする半導体装置を用いる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線間の寄生容量を十分に低減し得る半導体装置の製造方法を提供することにある。

【解決手段】半導体基板10上に多孔質絶縁膜54を形成する工程と、多孔質絶縁膜の表層部を緻密化する緻密化処理を行うことにより、多孔質絶縁膜54の表層部に、多孔質絶縁膜より密度の高い緻密層56を形成する工程とを有している。多孔質絶縁膜の表層部を緻密化する緻密化処理を行うことにより緻密層を形成するため、エッチングストッパ膜や保護膜として機能しうる良質な緻密層を極めて薄く形成することができる。従って、配線間の寄生容量を十分に低減することができる。

(もっと読む)

半導体装置の製造方法とそのような方法により得られる半導体装置

この発明は、半導体本体(1)と基板(2)とを備えた半導体装置(10)であって、少なくとも一つの半導体素子(3)を備え、そして、少なくとも一つの接続領域(4)と、接続領域(4)に接続された上部に横たわる帯状接続導体(5)とが設けられ、帯状接続導体と接続領域とが共に誘電体材料内に窪んでおり、続いて、第一の誘電体層(6)と、第一のハードマスク層(7)と、そして、第二の誘電体層(8)とが半導体本体(1)上に堆積され、接続領域(4)が形成される部位において、炭素とフッ素との化合物を含むプラズマを用いたプラズマエッチングにより第一の誘電体層(6)内にバイア(44)が形成され、そして、この構造の上部に堆積されたパターンニングされたフォトレジスト層が存在している状態で、接続導体(6)が形成される部位において、プラズマエッチングにより第二の誘電体層(8)内にトレンチ(55)が形成され、接続領域(4)と接続導体(5)とをそれぞれ形成するために、バイア(44)及びトレンチ(55)が導電材料で満たされ、そして、トレンチ(55)が形成される前に、既に形成されたバイア(44)が有機材料(2)で満たされる半導体装置の製造方法に関する。この発明では、バイア(44)のエッチング中にバイア(44)が同時にほぼ完全に有機材料(20)で満たされるように、第一の誘電体層(6)の材料と、プラズマエッチングによる第一の誘電体層(6)内のバイア(44)の形成中のエッチング条件とが選ばれ、この構造及びプラズマ内に既に存在する有機材料から有機材料(20)が形成される。エッチングの間にレジスト層が存在することと、そこで炭素とフッ素との化合物を用いること以外に、関わる条件は、第一(そして第二)の誘電体層(6,8)とこれら層(6,8)のエッチングの間の電力の選択に関する。  (もっと読む)

(もっと読む)

多孔性低k誘電体膜上への不透過性膜の堆積方法

【課題】多孔性低k誘電体膜上に不透過性膜を堆積させる方法を提供する。

【解決手段】相互接続構造における多孔性低k誘電体膜のようなデバイス上への不透過性膜の接着性を改善するための方法。本方法は、多孔性低k誘電体膜の水、アルコール、HCl、HF蒸気のような捕捉された蒸気又は吸着された分子を放出するために、不透過性膜の堆積前の原位置アニーリング段階を提供する。本方法はまた、多孔性低誘電性膜の堆積に続いて、捕捉可能分子を含む大気に露出することなく不透過性膜の原位置堆積を提供する。本方法は、更に、多孔性低k誘電体膜の一部分の除去に続いて、捕捉可能分子を含む大気に露出することなく不透過性膜の原位置堆積を提供する。実質的に全ての捕捉又は吸着分子を多孔性低k誘電体膜から除去することにより、堆積した不透過性膜と低k誘電体膜の間の接着性が改善される。本方法は、多孔性ハイドロシルセスキオキサン又は多孔性メチルシルセスキオキサン、エアロゲルのような多孔性シリカ構造体、低温堆積シリコン炭素膜、低温堆積Si−O−C膜、及びメチルドープ多孔性シリカのような多くの多孔性低k誘電体膜に特に適用可能である。  (もっと読む)

(もっと読む)

絶縁膜及び半導体装置の作製方法

【課題】複数の空孔を有する絶縁膜の形成方法を提案する。また、高集積化された半導体装置の歩留まり高い作製方法を提案する。

【解決手段】層間絶縁膜の低誘電率化の方法として、レーザ光を用いて層間絶縁膜中に複数の空孔を作成形成してすることにより、多孔質の絶縁膜を形成することを特徴とする。また、インクジェット法に代表される液滴吐出法を用いて、前記多孔質の絶縁膜に導電性粒子を含む組成物を吐出し、焼成して配線を形成する。レーザ光としては、超短パルスレーザーレーザ光を用いることが好ましい。

(もっと読む)

半導体装置

【課題】 半導体装置に関し、強誘電体キャパシタに印加される樹脂の吸湿による応力を実効的に低減して、安定した分極反転を可能にする。

【解決手段】 強誘電体キャパシタ1の上部電極4に接続する配線7の延在方向に沿って、強誘電体キャパシタ1を挟んで2つのプラグ5,6を配置する。

(もっと読む)

半導体装置の作製方法

【課題】材料の利用効率を向上させ、作製工程を簡略化した半導体装置の作製技術を提供することを目的とする。また、それらの半導体装置を構成する配線等のパターンを、所望の形状で密着性よく形成できる技術を提供することも目的とする。

【解決手段】第1の導電層上に第1の絶縁層を形成し、第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層上に第1の開口を有する第1のマスク層を形成し、第1の絶縁層及び第2の絶縁層をエッチングすることにより、第1の導電層に達する第1の開口部を形成し、第1のマスク層除去後、第1の開口よりも開口面積が広い第2の開口を有し、且つ、導電性材料を含む組成物に対してぬれ性の低い第2のマスク層を第2の絶縁層上に形成し、第1の絶縁層上面の一部が露出するように第2の絶縁層をエッチングし、第2の開口部を形成し、第1の開口部及び第2の開口部に導電性材料を含む組成物を充填し、第2の導電層を形成する。

(もっと読む)

相互接続構造の金属エッチング方法およびそのような方法で得られた金属相互接続構造

金属相互接続構造であって、

基板(11)と、基板の上にある誘電体層(12)と、誘電体層の上にある金属エッチング用の停止層(13)と、停止層の上にある金属層(15’)とを備え、前記金属層が所望のパターンに従ってパターン形成される金属相互接続構造。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 空孔を有する低誘電率膜に配線溝やビア孔などを形成した時に、その側壁からバリアメタルや配線材料が拡散することを阻止できる半導体装置の製造方法を提供することを目的とする。

【解決手段】 基体の上に、絶縁膜を形成する工程と、前記絶縁膜に開口を形成する工程と、前記絶縁膜の前記開口の内壁面に埋込層原材料を吸着させる工程と、前記吸着させた前記埋込層原材料を加熱して埋込層を形成する工程と、前記開口を導電性材料により充填する工程と、を備えたことを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

有機低誘電率膜(3)上に、SiC膜(4)、SiO2膜(5)及びシリコン窒化膜(6)を順次形成した後、シリコン窒化膜(6)の表面に対してO2プラズマ処理を施すことにより、シリコン窒化膜(6)の表面に酸化物層(7)を形成する。その後、シリコン窒化膜(6)及び酸化物層(7)に配線溝用のパターンを形成し、ビアホールのパターンが形成された樹脂層(10)を形成する。そして、酸化物層(7)の樹脂層(10)から露出している部分を除去することにより、不要なパーティクルも除去する。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】好適な形状の配線を有する半導体装置を提供することを課題とする。

【解決手段】素子と接続される第1の導電層と、その上の第2の導電層とを形成し、第2の導電層上にレジストのマスクを形成し、マスクを用いたドライエッチングによって第2の導電層を加工し、マスクを残したままウエットエッチングによって第1の導電層を加工する配線の作製方法であって、ドライエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレートより大きく、ウエットエッチングにおいて、第2の導電層のエッチングレートは第1の導電層のエッチングレート以上とする。

(もっと読む)

半導体素子の製造方法、及びエッチング方法

【課題】デュアルダマシン多層配線構造の形成においてハードマスクの肩落ちを抑制する。

【解決手段】半導体基板100上の第1配線層102上に無機系絶縁膜104を形成し、無機系絶縁膜上に開口部を有する第1レジストパターンを形成し、無機系絶縁膜をエッチングして無機系絶縁膜にビアホール106を形成し、第1レジストパターンを除去する。無機系絶縁膜上及びビアホールの内部を覆うように有機系絶縁膜107を形成する。有機系絶縁膜上にハードマスク108を形成し、ハードマスク上に開口部を有する第2レジストパターン109を形成してハードマスクパターン108aを形成する。第2レジストパターン及びハードマスクパターンをエッチングマスクとしてビアホール内の有機系絶縁膜が除去されるまで有機系絶縁膜をエッチングしてビアホール上に配線溝110を形成し、第2レジストパターンを除去する。ビアホール及び配線溝に導電材料を充填する。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール、ヴィアホール等のホールを形成するうえにおいて、ホール上部での歪の発生やホール寸法が所定の寸法から拡大してしまうという現象を防止する。

【解決手段】半導体基板11の上に、層間絶縁膜13、酸化タンタル膜14、有機反射防止膜15、レジスト膜16を順次形成する工程と、露光及び現像を行なうことにより、レジスト膜16に対してパターンを形成する工程と、パターンが形成されたレジスト膜16をマスクとして、有機反射防止膜15の少なくとも一部に対してドライエッチングをする工程と、酸化タンタル膜14をドライエッチングしながら、少なくともレジスト膜16及び有機反射防止膜15の側面に、タンタルの塩化物17を堆積する工程と、タンタルの塩化物17を保護膜として、層間絶縁膜13をドライエッチングする工程と、アッシングにより、タンタルの塩化物17を除去する工程を行なう。

(もっと読む)

半導体装置の製造方法

【課題】 エッチング工程で生成される反応生成物による配線信頼性の低下を防ぐ半導体装置の製造方法を提供する。

【解決手段】 配線と、配線に接続されるプラグとを有する半導体装置の製造方法であって、配線上に絶縁膜を形成する工程と、プラグを形成するためにドライエッチングにより絶縁膜に開口を形成する工程と、水素単体ガスまたは窒素を含むガスによるプラズマ放電により上記ドライエッチングにより生じた反応生成物を除去する工程とを有するものである。

(もっと読む)

導体通路上での分子構造の構築方法及び分子メモリマトリックス

この発明は、導体通路上に分子の構造を構築する方法及び分子メモリマトリックスに関する。この発明にもとづく方法により、安価で簡単な手法により任意の数の分子メモリ素子の構造を目的通り構築して、それによりメモリマトリックスを分子レベルで準備することが初めて可能となる。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜に設けられた接続孔内に設けられるバリア膜のカバレッジ不良を防止し、配線信頼性を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】基板11上に設けられた下層配線15上に層間絶縁膜17を形成し、層間絶縁膜17に接続孔18を形成する第1工程と、下層配線15の表面側の接続孔18の底部となる領域に、下層配線15を構成する第1の金属材料と当該第1の金属材料とは異なる第2の金属材料とからなる合金層31を形成する第2工程と、合金層31をスパッタエッチングする第3工程と、接続孔18に下層配線15に達する状態のヴィアを形成する第4工程とを有することを特徴とする半導体装置の製造方法および半導体装置である。

(もっと読む)

761 - 780 / 898

[ Back to top ]