Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

841 - 860 / 898

溝配線または接続孔を有する半導体装置の製造方法

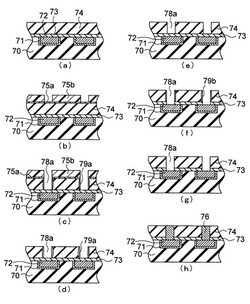

【課題】 電気的特性および信頼性に優れた溝配線または接続孔を有する半導体装置の製造方法を提供する。

【解決手段】 層間絶縁膜74上に所定の回路パターンを有するレジスト膜75bを形成し、レジスト膜75bをマスクとしてエッチング処理し、層間絶縁膜74にビア78aを形成する。このエッチング処理によって層間絶縁膜74に形成されたビア78aの側面部をシリル化処理し、ビア78aの側面部をエッチング処理によるダメージから回復させる。その後、ビア78aに金属を埋め込み、その表面を平坦化する。

(もっと読む)

配線基板の製造方法

【課題】 微細配線を実現することができる「配線基板の製造方法」を提供すること。

【解決手段】 ダマシンプロセスを用いた配線形成工程を含む配線基板の製造方法において、下層配線層10上に形成された層間絶縁層11に、下層配線層11に達するビアホールVHを形成し、その際に生じたスミアSMを除去した後、層間絶縁層11上に、ビアホールVHの上方に位置する所要の配線パターンの形状に従う開口部(配線溝)OPを有するように感光性永久レジスト層12を形成する。次に、全面にシード層13を形成し、ビアホールVH及び開口部(配線溝)OPの内部を充填するようにしてシード層13上に導体層14を形成した後、感光性永久レジスト層12が露出するまで導体層14の表面を研磨して平坦化し、配線パターン15を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコンプラグ上のプラグコンタクトの抵抗ばらつきを低減する。

【解決手段】半導体基板上の第1の絶縁膜12中にポリシリコンよりなるプラグ13を形成する工程と、ポリシリコンよりなるプラグの上に、酸化物層14を形成する工程と、ポリシリコンよりなるプラグと第1の絶縁膜の上に、第2の絶縁膜16を形成する工程と、第2の絶縁膜の上に、所定の形状にパターニングされたレジストを形成する工程と、パターニングされたレジストをマスクとして第2の絶縁膜の中に、コンタクト孔17bを設ける工程と、酸化物層を、ポリシリコンよりなるプラグの上に残した状態で、コンタクト孔の内部を洗浄する工程と、酸化物層を除去した後に、コンタクト孔の内部を導電性金属19で埋め込むことにより導電性金属よりなるプラグを形成する工程とを有する。

(もっと読む)

半導体装置の製造方法

本発明の目的は歩留りおよび生産性向上が図れる半導体装置の製造方法を提供することにある。本発明に係わる半導体装置の製造方法は、本発明は、真空容器1と、前記真空容器1内に設けられたウエハ8を設置するためのサセプタ7と、前記真空容器に原料ガスを導入するためのガス導入手段2と、および高周波電力導入手段6とを有するプラズマエッチング装置が準備され、前記ガス導入手段2により前記真空容器1内に導入されたガスを前記高周波電力でプラズマ化し、前記プラズマ雰囲気中でウエハ主面の酸化膜23に選択的に複数の穴を形成する工程を含む半導体装置の製造方法であって、前記穴を形成する工程で前記半導体ウエハ主面の平坦部と穴部とに連続スペクトルを有する光15を照射させ、前記平坦部と前記穴部との反射率変化を測定することを特徴とする。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 抵抗率のばらつきによる抵抗値のばらつきをもなくすため、抵抗素子の抵抗値を正確に知ることが可能であって、かつ、抵抗値を知るために回路領域が制限されることがない半導体装置の製造方法を提供する。

【解決手段】 抵抗素子を構成するポリシリコン膜と共にスクライブライン9上にもポリシリコン膜を成膜し、スクライブライン9上に成膜されたポリシリコン膜をパターニングし、モニタパターン7を形成する。また、モニタパターン7を使ったポリシリコン膜の抵抗率の測定結果に基づいて、抵抗素子を構成するポリシリコン膜を、このポリシリコン膜よりも上方に設けられる膜と同時にエッチングする。

(もっと読む)

ガス層形成材料

本発明は、アセナフチレンホモポリマー、アセナフチレンコポリマー、ポリ(アリーレンエーテル)、ポリアミド、B−ステージ多官能性アクリレート/メタクリレート、架橋スチレンジビニルベンゼンポリマー、およびスチレンとジビニルベンゼンとマレイミドまたはビス−マレイミドとのコポリマーから成る群から選択されるガス層形成材料を提供するものである。形成されたガス層はマイクロチップおよびマルチチップモジュールにおいて使用される。  (もっと読む)

(もっと読む)

非結晶性炭素膜を犠牲ハードマスクとして用いる半導体素子の製造方法

【課題】 本発明は、犠牲ハードマスクのエッチング選択比を増加させ、パターン変形を最小化できる半導体素子の製造方法を提供すること。

【解決手段】 本発明は、被エッチング層上に犠牲ハードマスク用の非結晶性炭素膜を形成するステップと、該犠牲ハードマスク用の非結晶性炭素膜上にフォトレジストパターンを形成するステップと、該フォトレジストパターンをエッチングマスクとして前記犠牲ハードマスク用の非結晶性炭素膜をエッチングし、犠牲ハードマスクを形成するステップと、少なくとも前記犠牲ハードマスクをエッチングマスクとして前記被エッチング層をエッチングし、所定のパターンを形成するステップとを含む。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】 半導体集積回路チップに基板貫通孔を短時間に効率よく形成する。

【解決手段】 チップ表面に拡散層15を形成して配線14と接続させ、貫通孔底部の中心が拡散層15と配線14との接続部分の中心にくるようにし、且つ貫通孔底部径が配線14と拡散層15との接合部分の径と同一かそれよりもやや大きな径になるように径を制御しながら、半導体集積回路チップ裏面13よりドライエッチングを開始して、貫通孔16を形成する。本発明の半導体チップ構造では、ドライエッチングの際に使用するエッチングガスはシリコンを選択的にエッチングするガスだけでよい。従ってエッチング工程の途中でエッチングガスを他の種類のエッチングガスに交換する必要がなく、基板貫通孔を短時間に効率よく形成することができる。

(もっと読む)

半導体装置の製造方法

【課題】 ダマシン配線のトレンチあるいはビアホールの側壁部でのダメージ層の生成および多孔質のLow−k膜中でのボイドの発生を抑制する。

【解決手段】 下層配線1上に第1エッチングストッパー層2a、多孔質の第1低誘電率膜2bおよび第1キャップ層2cの積層した第1層間絶縁膜2を形成し、C4F8のような炭素含有量が多いフルオロカーボンガスを用いレジストマスク3を使用したドライエッチングによりビアホール4を形成する。次に、第1キャップ層2cをハードマスクにし、エッチングガスとしてCF4/Ar/N2混合ガスあるいはCHF3/Ar/N2混合ガスを用い、上記エッチングガスの圧力を0.1Pa〜6.0Pa範囲にして第1エッチングストッパー層2aをエッチング除去し、ビアホール4を下層配線1表面に達するように貫通させる。

(もっと読む)

配線形成方法及び配線形成装置

【課題】 絶縁膜の材料の違いによってプロセス条件を変えたりすることなく、配線の表面に金属膜を選択的に成膜でき、しかも、不要となったバリア膜を、機械的な要素が相対的に少ない方法で除去できるようにする。

【解決手段】 絶縁膜10内に配線用凹部12を形成した基板表面にバリア膜14を形成し、次いで配線用凹部12内ならびに基板表面に配線材料16を成膜した基板Wを用意し、基板表面に成膜した余剰の配線材料16を除去して配線用凹部12内に埋込んだ配線材料16で配線18を形成するとともに、該配線形成部以外のバリア膜14を露出させ、配線18の表面に金属膜20を選択的に成膜する。

(もっと読む)

半導体装置の製造方法、半導体装置、及び電子機器

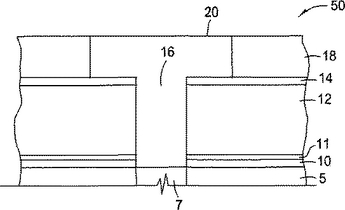

【課題】 積層された半導体チップの接合強度が高く、これにより高い信頼性を確保することができる半導体装置の製造方法及び半導体装置、並びに当該半導体装置を備える電子機器を提供する。

【解決手段】 半導体基板10の能動面10aから半導体基板10の内部にかけて第一孔部H3を形成する工程と、第一孔部H3の内側に導電材料を充填して第一接続端子20を形成する工程と、半導体基板10の能動面10aとは反対側の裏面10bから第一孔部H3の底面に到達する第二孔部H6を形成する工程と、第二孔部H6の内面に導電材料を充填して第二接続端子21を形成する工程と、を有する。

(もっと読む)

半導体素子のストレージノードコンタクトの形成方法

【課題】ランディングプラグコンタクトとストレージノードコンタクトとの間の不整合を防止し、接触抵抗を改善することができる半導体素子のストレージノードコンタクトの形成方法を提供すること。

【解決手段】複数のゲート23とソース/ドレーン領域25が形成された半導体基板21のゲート間に酸化膜26とランディングプラグコンタクトを形成するステップと、ランディングプラグコンタクト及びゲートを含んだ半導体基板の全面上に層間絶縁膜29を形成するステップと、層間絶縁膜をエッチングしてランディングプラグコンタクトを露出させる第1ストレージノードコンタクトホールを形成するステップと、露出されたランディングプラグコンタクトと酸化膜を除去し、第2ストレージノードコンタクトホールを形成するステップと、第2ストレージノードコンタクトホール内にポリシリコンを埋め込んでストレージノードコンタクト30を形成するステップとを含む。

(もっと読む)

半導体装置の製造方法

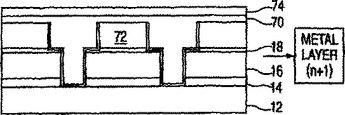

【課題】上層配線に被覆されない接続孔を選択的に縮小させることにより、隣接する異電位配線とのショート不良を防止することを可能とする。

【解決手段】基板上に第1、第2絶縁膜18、19を形成する工程と、その上に有機犠牲層30と第1、第2マスク層31、32を順に形成する工程と、第2マスク層32に配線溝パターン33を形成する工程と、第2、第1マスク層32、31および有機犠牲層30に接続孔を形成するための接続孔パターン34を形成する工程と、第2、第1マスク層31、32をエッチングマスクに用いたエッチングにより第1マスク層31、有機犠牲層30に配線溝パターン33を形成し、第2絶縁膜19に接続孔35を形成する工程と、第1マスク層31、有機犠牲層30をマスクに用いて、第2絶縁膜19に配線溝36を形成し、第2、第1絶縁膜19、18に接続孔35を形成する工程とを備えている。

(もっと読む)

プラズマ処理方法およびプラグ形成方法

【課題】表層部に銅とシリコンが存在する基板を対象として、六フッ化硫黄をプラズマ発生用ガスとして用いたプラズマエッチングにおいて、硫化銅の生成に起因して生じる銅部分への異物付着や形状不良を防止することができるプラズマエッチング方法およびプラグ形成方法を提供することを目的とする。

【解決手段】シリコン基板の表面をプラズマエッチングによって除去することにより、シリコン基板に埋設された銅電極の一端をシリコン基板の表面から突出させてプラグを形成する目的で行われるプラズマエッチングにおいて、プラズマ発生用ガスとして六フッ化硫黄を主成分とする混合ガスを使用し、シリコン基板の表面温度を65℃以下に保ちながらプラズマエッチングを行う。これによりプラズマ処理過程で生成した硫化銅の付着を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】加工パターンの疎密に依存することなく面内均一に精度良好なパターン加工行うことが可能なエッチング工程を備えた半導体装置の製造方法を提供する。

【解決手段】基板11上にSiOCH系絶縁膜からなる被エッチング膜13を形成し、マスクパターン15上からのプラズマ処理を行う。これにより、マスクパターン15から露出している被エッチング膜13部分をSiO2化して改質部13bを形成する前処理を行う。次に、マスクパターン15およびSiOCH系材料からなる未改質部13aに対して選択的に改質部13bをエッチング除去する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ダミーパターンの面積を大きくしなくても、半導体素子や配線へのプラズマチャージ量を少なくする。

【解決手段】 半導体基板1にトランジスタ11を形成すると共に、半導体基板1上にMNOS素子10を形成する。MNOS素子10に電荷を蓄積した後、層間絶縁膜20を形成する。層間絶縁膜20に、ゲート電極5b上に位置する第1の接続孔20b、及びMNOS素子10上に位置する第2の接続孔20aを形成する。層間絶縁膜20上に、第1の接続孔20bを介してゲート電極5bに接続する配線22bを形成すると共に、第2の接続孔20aを介してMNOS素子10に接続するダミーパターン22aを形成する。

(もっと読む)

半導体装置の作製方法

【課題】 ナノインプリント法を用いることでコストを抑えることができる、半導体装置の作製方法の提案を課題とする。

【解決手段】 本発明は、島状の半導体膜上にゲート絶縁膜と、導電膜と、レジストとを順に形成し、パターンが形成されたモールドをレジストに押し付けた状態でレジストの硬化を行なうことで、パターンをレジストに転写し、導電膜の一部が露出するまでパターンが転写されたレジストの表面をアッシングし、アッシングされたレジストをマスクとして用い、導電膜をエッチングすることを特徴とする。

(もっと読む)

耐酸化性が良好な次世代ダマシンバリヤ適用のための二層膜

基板を処理する方法であって、フェニル基を含む有機シリコン化合物を含む処理ガスを処理チャンバに供給するステップと、処理ガスを反応させて低k誘電物質によるダマシン又はデュアルダマシン適用においてバリヤ層として用いられる低kシリコンカーバイドバリヤ層を堆積させるステップとを含む、前記方法が提供される。低kシリコンカーバイドバリヤ層上に酸素を含まない有機シリコン化合物を含む処理ガスからのシリコン原子にフェニル基がほとんど結合されていないシリコンカーバイドキャップ層を堆積する方法が提供される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 少ない工程でアライメントマークとして利用できる段差を形成することが出来る、半導体装置の製造方法を提供する。

【解決手段】 基板の表面又は基板上に形成した第1の膜の表面に、複数の凹部を形成する第1の工程と、凹部の内部に選択的に第2の膜を形成する第2の工程と、少なくとも1つの凹部及びその近傍を含む第1の領域に局所的エッチングを行って、第1の領域内の第2の膜の表面とその近傍との間に段差を形成する第3の工程とを備える。段差が形成された位置をアライメントマークとして利用する。

(もっと読む)

半導体集積回路装置及び回路配線方法

【課題】 ゲート電極に繋がる配線に関し、アンテナ効果によるチャージングの影響を極力抑え、プラズマ処理を伴うウェハプロセスにおいても高信頼性が得られる半導体集積回路装置及び回路配線方法を提供する。

【解決手段】 配線部WR1はゲート電極13引き出し用の縦方向優先配線部として、最終的な配線前の配線層153まで配線面積を最小限とする。これにより、アンテナ効果対策として最良の配線構造が得られる。一方、配線部WR2は、アンテナ効果対象外の配線パターンとして、配線部WR1との接続以外の実質的な回路配線を構成する広域配線部である。また、必須パターンとして配線部WR1近傍にパターン端部153Eを配する。配線部WR3は最終接続配線部である。すなわち、配線部WR1は、配線部WR3によってはじめて他の必要な素子回路(配線部WR2)と接続関係を持つことになる。

(もっと読む)

841 - 860 / 898

[ Back to top ]