Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

861 - 880 / 898

半導体装置及び半導体装置の製造方法

【課題】 半導体素子の搭載されたで導電性基板に、導電性基板の表裏面の導通をとる高アスペクト比、小径の貫通孔を、高温プロセスを使用する事なく形成する。

【解決手段】 あらかじめその表面に半導体素子及び該半導体素子と繋がる電気接続部が作りこまれている、半導体基板またはガラス基板からなる導電性基板の所定位置に、少なくとも1つの貫通孔をレーザ等で形成し、該貫通孔の内側表面に蒸着重合法により絶縁層を形成し、該絶縁層の内側表面およびそれと連なる該貫通孔の開孔部周辺部に、無電解メッキ等により導電層を該電気接続部と繋がるように形成する事で、該電気接続部と基板の裏面あるいは側面との導通をとる。

(もっと読む)

半導体装置の製造方法

【課題】 少ない工程でアライメントマークとして利用できる段差を形成することが出来る、半導体装置の製造方法を提供する。

【解決手段】 基板の表面又は基板上に形成した第1の膜の表面に、複数の凹部を形成する第1の工程と、凹部の内部に選択的に第2の膜を形成する第2の工程と、少なくとも1つの凹部及びその近傍を含む第1の領域に局所的エッチングを行って、第1の領域内の第2の膜の表面とその近傍との間に段差を形成する第3の工程とを備える。段差が形成された位置をアライメントマークとして利用する。

(もっと読む)

半導体集積回路装置及び回路配線方法

【課題】 ゲート電極に繋がる配線に関し、アンテナ効果によるチャージングの影響を極力抑え、プラズマ処理を伴うウェハプロセスにおいても高信頼性が得られる半導体集積回路装置及び回路配線方法を提供する。

【解決手段】 配線部WR1はゲート電極13引き出し用の縦方向優先配線部として、最終的な配線前の配線層153まで配線面積を最小限とする。これにより、アンテナ効果対策として最良の配線構造が得られる。一方、配線部WR2は、アンテナ効果対象外の配線パターンとして、配線部WR1との接続以外の実質的な回路配線を構成する広域配線部である。また、必須パターンとして配線部WR1近傍にパターン端部153Eを配する。配線部WR3は最終接続配線部である。すなわち、配線部WR1は、配線部WR3によってはじめて他の必要な素子回路(配線部WR2)と接続関係を持つことになる。

(もっと読む)

貫通電極の形成方法、貫通電極および半導体装置

【課題】 工数や手間の増大を招くことなく、半導体基板の汚染を防止できる貫通電極の形成方法を提供すること。

【解決手段】 シリコン基板1に非貫通孔を形成し、この非貫通孔の底面からシリコン基板1に不純物を添加して、不純物添加部2を形成する。非貫通孔の側面および底面に表面側絶縁膜3を形成し、表面側絶縁膜3の内側に埋め込み電極4を形成する。シリコン基板1の裏面部分を除去して、不純物添加部2を裏面に露出させる。シリコンに対してエッチングレートが高いエッチングによって、不純物添加部2を、埋め込み電極4に対してセルフアライメントした状態で除去できる。

(もっと読む)

基板をエッチングするための方法及び装置

本方法及び装置は、化学式CaFbを有する第1のガス及び化学式CxHyFzを有する第2のガスの混合物(ただし、a/b≧2/3、x/z≧1/2である)に基づくプラズマの使用を通して半導体及び誘電体基板をエッチングするために提供される。この混合物は、磁気的に増強された反応性イオンチャンバ内に維持された低または中密度プラズマにおいて用いられ、優れたコーナー層の選択性、ホトレジストの選択性、下層の選択性及びプロファイルと底部のCD制御を示すプロセスを提供する。第1と第2のガスのパーセンテージは、ドープされない酸化物膜をエッチングするプラズマまたはこのような膜上でエッチング停止を与えるために、エッチング中に変えることができる。  (もっと読む)

(もっと読む)

半導体チップの製造方法および半導体装置の製造方法

【課題】 貫通電極用の貫通孔の形成時間を短縮化することで生産性を向上させた半導体チップの製造方法を提供する。

【解決手段】 まず、第1の絶縁膜3をマスク部材としてシリコン基板1の上面側に第1のトレンチ7aを例えばボッシュプロセスを用いて形成する。次に、第2の絶縁膜5をマスク部材としてシリコン基板1の裏面側に、第1のトレンチ7aに連通する第2のトレンチ7bを同じくボッシュプロセスを用いて形成する。そして、これにより形成された貫通孔8内に絶縁膜を形成した後、その貫通孔8内に導電性材料を充填して貫通電極2を形成する。

(もっと読む)

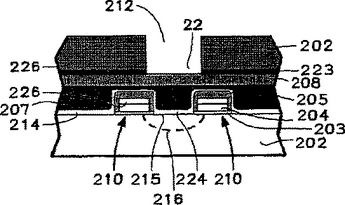

相異なるチャネル領域に相異なるよう調整された内在応力を有するエッチストップ層を形成することによって、相異なる機械的応力を生成するための技術

コンタクトエッチストップ層(116)を設けることによって、異なるトランジスタ型(100N),(100P)のチャネル領域内の応力を効果的に制御することができる。その際、コンタクトエッチストップ層(116)の引張応力部分と圧縮応力部分は、ウェット化学エッチング、プラズマエッチング、イオン注入、プラズマ処理などの十分に確立されたプロセスによって得ることができる。このため、プロセスを著しく複雑にすることなく、トランジスタ(100N),(100P)の性能を大きく改善することができる。  (もっと読む)

(もっと読む)

スパッタ反応装置内で金属バリアを形成するために特にマルチステッププロセスで使用される可変四重電磁石アレー

スパッタチャンバ(70)及びそれが可能にするマルチステッププロセス。チャンバ軸と同軸な四重電磁石矩形アレー(72)はチャンバ内のRFコイル(46)の裏側にあることが好ましい。異なる磁場分布を生成するために、例えば、ターゲット材料をウエハ(32)上にスパッタするためにスパッタターゲット(38)が給電されるスパッタ堆積モードとRFコイルがアルゴンスパッタリングプラズマをサポートするスパッタエッチングモードとの間でコイル電流を個別に制御できる。ターゲット材料のRFコイルにおいては、コイルにDCバイアスをかけることができ、コイルアレーがマグネトロンとしての機能を果たす。このようなプラズマスパッタチャンバ内で行なわれるマルチステッププロセスは、様々な条件下でのターゲットからのバリア材料のスパッタ堆積と、基板のアルゴンスパッタエッチングとを含んでいてもよい。ターゲット電力及びウエハバイアスの減少を伴うフラッシュステップが適用される。 (もっと読む)

空隙を有する半導体デバイスの形成方法および該方法によって形成された構造

【課題】半導体デバイスの形成方法および該方法によって形成されたデバイスを提供すること。

【解決手段】第1の誘電材料(12a〜f)と第2の誘電材料(14a〜f)の互層を付着させる。ここで、第1の誘電材料と第2の誘電材料は異なる速度で選択的にエッチング可能である。誘電材料の互層内に第1のフィーチャ(22、24)を形成する。誘電材料の互層を選択的にエッチングして、第1の誘電材料を有するそれぞれの層内の第1の誘電材料の少なくとも一部分(26)を除去し、第2の誘電材料は本質的にエッチングされていないままにしておく。

(もっと読む)

フルオロカーボン化学エッチングにおけるH2添加物を使用しての炭素ドープ酸化ケイ素エッチング

実施例はエッチング材料の供給(210)、水素を含む混合ガスの適用(230)、プラズマの発生(240)、エッチング材料のエッチング(250)を含むエッチング方法(200及び1600)を含む。エッチング材料は低k誘電性材料を含み得る。混合ガスは水素ガス、水素非含有フルオロカーボン、窒素ガスを含み得る。また、1つ以上のハイドロフルオロカーボンガス、不活性ガス、及び/又は一酸化炭素を含み得る。水素ガスとしては、H2、CH4、C2H4、NH3、及び/又はH2Oガスを含む、二原子水素、炭化水素、シラン、及び/又はフッ素非含有水素ガスであってもよい。水素非含有フルオロカーボンガスはCxFyガス(x≧1、y≧1)、ハイドロフルオロカーボンガスはCxHyFzガス(x≧1、y≧1、z≧1)であってもよい。混合ガスは酸素非含有であってもよい。実施例は減圧、低流量水素、1つ以上のプラズマ周波数を含み得る。

(もっと読む)

(もっと読む)

プラズマ加工システムによる基板エッチング法

プラズマ加工システムで基板をエッチングする方法を提供する。基板は、半導体層、その半導体層上方に提供された第1バリアー層、その第1バリアー層上方に提供された低k層、その低k層上方に提供された第3ハードマスク層、その第3ハードマスク層上方に提供された第2ハードマスク層、及びその第2ハードマスク層上方に提供された第1ハードマスク層を有する。方法には、第1ハードマスク層の第1ハードマスク材料、第3ハードマスク層の第3ハードマスク材料、及び第1バリアー層の第1バリアー層材料に対して低選択度を有するが、第2ハードマスク層の第2ハードマスク材料に対しては高選択度を有する第1エチャントと、第1ハードマスク層の第1ハードマスク材料、第3ハードマスク層の第3ハードマスク材料、及び第1バリアー層の第1バリアー層材料に対しては高選択度を有する第2エチャントとで基板を交互にエッチングするステップが含まれ、第1エチャントは第2ハードマスク層の第2ハードマスク材料に対して低選択度を有する。  (もっと読む)

(もっと読む)

成膜方法、SiO2膜、電子部品および電子機器

【課題】所定パターンのSiO2膜を容易かつ安価に形成し得る成膜方法、かかる成膜方法により形成されたSiO2膜、このSiO2膜を備える電子部品および電子機器を提供すること。

【解決手段】本発明の成膜方法は、所定パターンの第2の層間絶縁層(SiO2膜)5を形成する方法であり、主としてポリオルガノシロキサンで構成されるポリオルガノシロキサン膜を形成する第1の工程と、ポリオルガノシロキサン膜の前記所定パターンに対応する領域に、第1のSiO2化処理を施して、前記領域に存在するポリオルガノシロキサンをSiO2に変化させる第2の工程と、SiO2に変化した前記領域をアルカリ溶液により除去する第3の工程と、第3の工程において残存するポリオルガノシロキサン膜に、第2のSiO2化処理を施して、ポリオルガノシロキサンをSiO2に変化させることにより、第2の層間絶縁層5を得る第4の工程とを有する。

(もっと読む)

アモルファスカーボン膜を含む構造およびその形成方法。

【課題】 アモルファスカーボン膜を有する構造およびその形成方法を提供することである。

【解決手段】 半導体デバイスは、半導体基板と、半導体基板上に形成され、被処理膜を有する膜スタックとを含む。膜スタックに含まれるデュアルハードマスクは、アモルファスカーボン層、およびアモルファスカーボン層と被処理膜との間に配置される下層のハードマスク層を有し、ハードマスク層は、アモルファスカーボン層を含まない。金属配線のためのダマシン構造は、膜スタックに形成されている。アモルファスカーボン膜は、例えば、シングルダマシン構造またはデュアルダマシン構造の中で取り入れられることができる。アモルファスカーボン膜は、配線構造を形成するためのリソグラフィマスクの一部として役に立つことができ、または、それは、CMPの間、デュアルハードマスク、ケミカルメカニカルポリシング(CMP)ストップ層または犠牲層の上部層として役立つことになる。

(もっと読む)

銅表面に対する表面還元、不動態化、腐食防止、および活性化のためのシステムおよび方法

【課題】

【解決手段】露出された導電材料を不動態化するシステムおよび方法は、処理チャンバ内に基板を配置する工程と、処理チャンバ内に水素種を注入する工程とを備える。処理チャンバ内で、水素種のプラズマが形成される。基板の上面から、表面層の種が還元される。還元された表面層の種は、処理チャンバから取り除かれる。

(もっと読む)

基板処理方法、プラズマ室および半導体デバイス

【課題】

【解決手段】基板処理のシステムおよび方法には、プラズマ室に基板を装填しプラズマ室の圧力を所定の圧力設定値に設定することが含まれる。プラズマ領域を構成するいくつかの内面が約200℃以上の処理温度に加熱される。プラズマを形成するために処理ガスがプラズマ領域に注入され、基板が処理される。

(もっと読む)

プラズマ処理システムにおける選択性の制御方法

プラズマ処理システムにおける、半導体基板上の所定の層を介して機能をエッチングするための方法。本方法は、上記プラズマ処理システムのプラズマ処理室に基板を置くことを含む。また本方法は、上記プラズマ処理室内へエッチャント混合気を流し込むことも含み、上記エッチャント混合気は所定の層をエッチングするように構成されている。本方法はさらに、エッチャント・ソース・ガスからのプラズマを打撃することを含む。さらに本方法は、上記基板にバイアスRF信号を印加しながら、上記機能を少なくとも部分的に所定の層を介してエッチングすることを含む。上記バイアスRF信号は約27MHz乃至約75MHzの範囲のバイアスRF周波数と、バイアスRF電力成分とを有し、上記バイアスRF電力成分は、エッチ機能を、基板の第2の層への、予め決められた選択性しきい値より高いエッチング選択性でエッチングさせるように構成され、または上記機能を、バイアスRF周波数における予め決められたエッチ速度パラメータ及びエッチ・プロファイル・パラメータに従ってエッチングさせるように構成される。  (もっと読む)

(もっと読む)

レジスト剥離中における多孔質低誘電率材料の損傷を阻止する方法

【課題】レジスト剥離中における多孔質低誘電率材料の損傷を阻止する。

【解決手段】多孔質低誘電率層内に形状を形成する方法が提供される。先ず、基板の上に、多孔質低誘電率層が配される。次いで、多孔質低誘電率層の上に、パターン形成されたフォトレジストマスクが配される。次いで、多孔質低誘電率層内に、形状がエッチングされる。形状のエッチング後は、形状の上に保護層が成長される。そして、保護層の一部が除去されるように、パターン形成されたフォトレジストマスクが剥離され、形状内に、保護層で形成された保護壁を残留させる。

(もっと読む)

トレンチエッチングのためのラインエッジ粗さ低減

【課題】基板上の誘電体レイヤにおいてトレンチ深さまでトレンチをエッチングする方法を提供する。

【解決手段】ARCが前記誘電体レイヤ上に設けられる。厚さを有するフォトレジストマスクが前記ARC上に形成される。前記ARCがエッチングされる。1:1および2:1の間であるフォトレジストに対する誘電体のエッチング選択性で、トレンチが前記誘電体レイヤ中へエッチングされる。

(もっと読む)

フォトレジストストリッピングの間のバリヤー物質損失の最小化

銅インターコネクトを覆う暴露されたバリヤー層を含むエッチングされた誘電体物質を有する集積回路(IC)構造からフォトレジスト層を除去する方法。バリヤー層は、5窒化ケイ素または炭化ケイ素のような物質によって構成される。本方法は、一酸化炭素(CO)をさらすガス混合物を反応器に供給する工程を含む。ついで、反応器内で、プラズマを発生させる。フォトレジスト層は、ついで、暴露されたバリヤー層をほとんどまたは全くエッチングすることなく選択的に除去される。  (もっと読む)

(もっと読む)

ウエハのエッチング技術

半導体材料(102)のウエハ(100)上に貫通ビア(116、118)をエッチングするための方法(10)であって、ウエハ(100)が前側表面(110)と裏側表面(106)を有する方法を記載する。フォトレジスト材料の層(104)を裏側表面(106)に施用する。その後、フォトレジストの層(104)を、予め選択されたパターンを有するマスクを介して光源に暴露し、ここにおいて、現像されたフォトレジストを除去して、残存フォトレジスト層(104’)に少なくとも1つのビア(112、114)を形成させる。その後、残存フォトレジスト層(104’)を焼き付けて、硬化した残存フォトレジスト層(104’)を形成させる。その後、少なくとも1つのビア(112、114)に隣接する半導体材料(102)をガスプラズマエッチングして、裏側表面(106)と前側表面(110)の間に貫通ビア(116、118)を形成させる。その後、硬化した残存フォトレジスト層(104’)を除去し、続いて伝導性材料の層(120)を貫通ビア(116、118)の表面に施用して、裏側表面(106)と前側表面(110)の間に電気接続性を確立する。 (もっと読む)

861 - 880 / 898

[ Back to top ]