Fターム[5F033QQ33]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | サイドエッチング、アンダーエッチング (105)

Fターム[5F033QQ33]に分類される特許

1 - 20 / 105

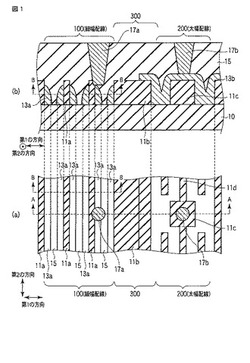

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜上に下地金属層と上部金属層からなる配線を備えた半導体装置において、下地金属層のサイドエッチングによる絶縁膜と上部金属層との密着性の劣化を抑制することができる半導体装置、及び、その製造方法を提供する。

【解決手段】配線本体16が形成される絶縁膜14の上面には、配線本体16のパターンに対応し、かつ、絶縁膜14の上面から所定の深さの凹部14aが設けられ、当該凹部14aを含む絶縁膜14上面に、配線の一部であり、かつ、密着層であるチタン薄膜15を介して配線本体16が設けられている。凹部14aの幅は、配線本体16の幅よりも狭くなるように設定される。チタン薄膜15は配線本体16の配線幅よりも狭く形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板を実装する際の温度負荷によって絶縁層と下地金属層の側面との接点領域に加わる応力を緩和させ、応力に起因した絶縁層のクラックの発生を抑えるように構成された半導体装置を提供する。

【解決手段】半導体基板101の一面101aに、絶縁層102、下地金属層103、金属端子が設けられるためのランド部104を順に積層してなる半導体装置109であって、ランド部104は、絶縁層102と対向する面の中央部において、下地金属層103と接合する接合領域と、絶縁層102と対向する面において、接合領域を除いた非接合領域と、を有し、下地金属層103は、ランド部104側から絶縁層102側にかけて外向きに傾斜した側面を有していること、を特徴とする半導体装置109。

(もっと読む)

半導体装置、およびコンタクトプラグの形成方法

【課題】半導体装置内の回路に用いる構造として、半導体回路の電極体と導通電極とのコンタクト抵抗を良好に維持する。

【解決手段】半導体装置内の回路に用いる構造として、半導体回路の電極体とするシリサイドと、そのシリサイドと電気的に接続され、ストッパ層を取り除いて該シリサイドの側面を露出させた空間に形成された導通電極とするコンタクトプラグとを設ける。

(もっと読む)

パターン状金属膜の製造方法

【課題】レジスト膜の厚みを比較的小さくしてかつオーバーエッチングするパターン状金属膜の製造方法において、所望パターンの金属膜を安定的に製造することができる製造方法を提供する。

【解決手段】金属膜上にパターン状のレジスト膜を形成する工程(A)、前記金属膜をエッチングする工程(B)を順次有するパターン状金属膜の製造方法であって、前記レジスト膜は厚みが5μm以下でかつ鉛筆硬度がB以下であり、前記工程(B)において前記レジスト膜の線幅100%に対してパターン状金属膜の線幅が80%以下となるようにオーバーエッチングする、パターン状金属膜の製造方法。

(もっと読む)

半導体装置、半導体装置の製造方法、固体撮像装置及び電子機器

【課題】 ビア形成時のエッチングによる基板や配線への影響を抑制しつつ積層された半導体ウェハの回路どうしを接続する。

【解決手段】 半導体装置の製造方法は、第1基板と第1基板の一面と接するように形成された第1絶縁層を有する第1の半導体ウェハと、第2基板と第2基板の一面と接するように形成された第2絶縁層を有する第2の半導体ウェハを接合する工程と、第1基板の他面に第3絶縁層を形成する工程と、第3絶縁層、第1基板、及び第1絶縁層を貫通し第2絶縁層に形成された第2の配線上に第2絶縁層が残るようにエッチングを行い第1接続孔を形成する工程と、第1接続孔に絶縁膜を形成する工程と、第2の配線上の第2絶縁層及び絶縁膜のエッチングを行い第2接続孔を形成し第2の配線を露出させる工程と、第1及び第2接続孔の内部に形成され第2の配線と接続する第1のビアを形成する工程とを備え、第1基板の他面に形成された第1接続孔の径は第3絶縁層に形成された前記第1接続孔の径より大きい。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

固定された導電性ビアおよびその製造方法

【課題】導電性ビアおよびそれを形成する方法に関する。

【解決手段】導電性ビアが、導電性接触構造と該導電性接触構造上に配置された誘電体層の突出部との間に配置された部分を含む。1つの実施形態において、突出部は、導電性接触構造上にアンダーカット層を形成し、次に、該導電性接触構造およびアンダーカット層上に誘電体層を形成することによって形成される。誘電体層に空洞を形成し、誘電体層の突出部を形成するようにアンダーカット層の材料が該空洞を通して除去される。導電性ビアの導電性材料は次に、突出部の下および空洞に形成される。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

多層薄膜パターン及び表示装置の製造方法

【課題】間便に所望の形状のパターンを得ることのできる多層薄膜パターン及び表示装置の製造方法を提供すること。

【解決手段】基板上に層間絶縁膜1を形成する工程と、層間絶縁膜1上に導電性を有する第1の薄膜2を形成する工程と、第1の薄膜2上に第2の薄膜3を形成する工程と、第2の薄膜3上に、複数階調露光によって膜厚差を有するレジストパターン5を形成する工程と、膜厚差を有するレジストパターン5を介して、第2の薄膜3及び第1の薄膜2をエッチングして、レジストパターンの存在しない領域の層間絶縁膜1を露出させる工程と、膜厚差を有するレジストパターン5をアッシングして、レジストパターンの薄膜部5bを除去する工程と、薄膜部5bが除去されたレジストパターン5cを介して、第2の薄膜3をエッチングする工程と、を順次実施する。

(もっと読む)

側壁イメージ転写からパターンを作る改善された方法

【課題】実施の容易な、側壁イメージ転写により部分的に定義されるパターンを生成する方法を提供する。

【解決手段】基板1には、第1の材料2の層と、第1のエッチングマスク4と、カバリング層3と、第2のエッチングマスクとが設けられている。カバリング層3は、覆われた主領域と、覆われていない副領域とを有する。カバリング層3の副領域は、第2のエッチングマスクを介して部分的にエッチングされ、突出パターンが形成される。第3のエッチングマスクを定義する突出パターンの周囲に、横スペーサが形成される。第2のエッチングマスクは除去される。カバリング層3は、第3のエッチングマスクを用いてエッチングされ、カバリング層3における突出パターンが形成され、第1のエッチングマスク4および第1の材料2が露出される。第1の材料2の層は、エッチングされ、第1の材料2から作られるパターンが形成される。

(もっと読む)

半導体装置の作製方法

【課題】コンタクトホールを微細化する。この時、微細化されたコンタクトホールであっ

ても、半導体装置における電極のコンタクトを確実なものとする。

【解決手段】珪化膜と樹脂材料膜とからなる多層の層間絶縁膜を形成する。その後、コン

タクトホールを形成する。このとき、珪化膜に設けられるコンタクトホールの大きさを樹

脂材料膜に設けられるコンタクトホールの大きさよりも小さくする。このような構成は、

パターンが複雑化してもコンタクトのとりやすいものとすることができる。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】少ない工程でパッド電極に段差を設けた半導体素子を製造することができる半導体素子の製造方法及び半導体素子を提供する。

【解決手段】半導体基板12上に中間絶縁膜14、下層メタル配線16、層間絶縁膜18を形成し、層間絶縁膜18上にパッド電極20を形成し、パッド電極20上に最終保護膜22を形成し、最終保護膜22上に、パッド電極20の一部に対応した第1領域に開口部を備えるレジスト22を形成し、最終保護膜22をエッチングすると共に、パッド電極20の一部の第1領域を予め定めた深さまでエッチングすることにより凹部20Aを形成し、パッド電極20の第1領域を囲う第2領域上の最終保護膜22をエッチングし、レジスト22を除去することにより、半導体素子10を製造する。

(もっと読む)

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線間のリークを抑制しつつ、再配線のピッチを微細化するとともに、再配線上のビア開口時のマージンを上げる。

【解決手段】緩衝層4上には再配線7bが形成され、再配線7b上には表面層8bが形成されている。表面層8bは、再配線7bから幅方向にはみ出すようにして再配線7bに沿うように配置され、再配線7bよりもエッチング耐性が高い。

(もっと読む)

エッチング方法、エッチングシステムおよびエッチング装置

【課題】シリコン酸化膜にコンタクト部に到達する高アスペクト比のホールを形成する際に、ホール内のコンタクト材料とコンタクト部との間で十分なコンタクトがとれるようなホールを形成すること。

【解決手段】基板上にBおよびPの少なくとも一方を含むシリコン酸化物からなる第1の酸化膜と、その上に形成された、BおよびPを含まないシリコン酸化物からなる第2の酸化膜とを有し、さらに第1の酸化膜および第2の酸化膜の界面より下方に形成されたコンタクト部を有する被処理体を準備し(ステップ1)、第2の酸化膜と前記第1の酸化膜をエッチングしてコンタクト部に到達するホールを形成し(ステップ2)、HFガスおよび不活性ガスを用いたドライプロセスにより第1の酸化膜をエッチングし、第1の酸化膜のコンタクト部上方領域のホール部分を広げる(ステップ3)。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

1 - 20 / 105

[ Back to top ]