Fターム[5F033QQ38]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | コンタクトホールの形成 (4,383) | 深さの異なる複数の孔のエッチング (177)

Fターム[5F033QQ38]の下位に属するFターム

同時にエッチング (119)

Fターム[5F033QQ38]に分類される特許

21 - 40 / 58

半導体装置及びその製造方法

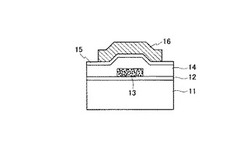

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高信頼性でかつ高レイアウト密度配線と混載可能な容量素子を備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明は、容量素子を有する半導体装置であって、アルミニウム合金膜102と、高融点金属膜を含む上層バリア膜103とを含む金属配線200aおよび下部電極200bと、下部電極200b上に形成された容量絶縁膜104と、容量絶縁膜104上に形成された上部電極105とを有する。高融点金属膜の膜厚は、40nm以上、80nm以下であり、容量絶縁膜104は、有機シランを原料としたシリコン酸化膜からなることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 信号線の形成位置に関わらず、信号線とMIM構造のキャパシタ11との間で発生する寄生容量が抑制できるようにする。

【解決手段】 MIM構造のキャパシタ11と、絶縁膜12a,12bを介してMIM構造のキャパシタ11を挟む、少なくとも一対の遮蔽部13a,13bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】素子分離部に対するウエルコンタクトホールの位置合わせ精度を向上する。

【解決手段】半導体基板にウエル領域2を形成する第1の工程と、前記半導体基板に、第1のアライメントマークと、前記ウエル領域2にアクティブ領域を分離する素子分離部7とを形成する第2の工程と、前記半導体基板の上に、第2のアライメントマークと、MOSトランジスタのゲート電極9とを形成する第3の工程と、前記ゲート電極9とともにソース電極又はドレイン電極となるべき半導体領域を形成する第4の工程と、前記半導体基板及び前記ゲート電極9の上に絶縁膜14を形成する第5の工程と、前記第1のアライメントマークを基準として決められた位置に、ウエルコンタクトホールを形成する第6の工程と、前記第2のアライメントマークを基準として決められた位置に、前記絶縁膜14を貫通するコンタクトホールを形成する第7の工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

半導体構造、半導体構造を形成する方法、および半導体デバイスを操作する方法(信号忠実度および電気的分離が強化されたSOI無線周波スイッチ)

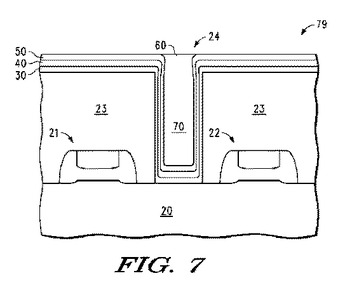

【課題】SOI(セミコンダクタ・オン・インシュレータ)基板内の底部半導体層からの半導体デバイスについて強化された信号分離を可能とする半導体構造、これを製造する方法、およびこれを操作する方法を提供する。

【解決手段】底部半導体層10と反対の導電性タイプを有するドープ接点領域18は底部半導体層10内の埋め込み絶縁体層20の下に設ける。少なくとも1つの導電ビア構造47,77は、相互接続レベル金属ライン94から、中間工程(MOL)誘電体層80、最上部半導体層30内の浅いトレンチ分離構造33、および埋め込み絶縁体層20を通り、ドープ接点領域18まで延びる構造とする。

(もっと読む)

半導体装置及びその製造方法

【課題】金属配線部から、金属が層間絶縁膜に拡散することを抑制するためのシリコン窒化膜等から窒素や水素が拡散することによる影響を軽減した信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2上に形成された半導体素子部100と、半導体素子部100の上部に形成された銅配線225と、半導体素子部100と銅配線225とを電気的に接続するプラグ電極216と、このプラグ電極216が酸化しないようにするシリコン酸化膜223と、半導体素子部100の上部に形成されたアモルファスシリコン膜217と、アモルファスシリコン膜217の上部に形成されたCu拡散防止膜218と、を有した半導体装置1とする。

(もっと読む)

表示装置及びその製造方法

【課題】CVD装置への出し入れ回数を減らした表示装置の製造方法および表示装置を提供すること。

【解決手段】本発明にかかる表示装置の製造方法は、絶縁基板上に第1の電極膜と第2の電極膜とを含む導電層、第1の絶縁層、半導体膜、第2の絶縁層および保護層を形成する工程と、半導体膜の上方の第1の領域に配置される所定の厚さの第1のレジスト膜と、第2の電極膜の上方の第2の領域に配置される開口部と、それら以外の領域に配置される厚い第2のレジスト膜と、を保護層上に形成する工程と、第2の領域下をエッチングする工程と、第1のレジスト膜をアッシングにより除去する工程と、第1の領域下に半導体膜に達する第1の孔を形成し、かつ第2の領域下に第2の電極膜に達する第2の孔を形成する工程と、第2のレジスト膜を除去する工程と、半導体膜および第2の電極膜と接続される配線を形成する工程と、を含む。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、強誘電体膜を備えたキャパシタの劣化を防止すること。

【解決手段】シリコン基板30の上方に、下部電極61と、強誘電体膜よりなるキャパシタ誘電体膜62と、上部電極63とを有するキャパシタQを形成する工程と、キャパシタQ上に第1の保護膜70を形成する工程と、第1の保護膜70に、上部電極63に達する第1の開口70aを形成する工程と、第1の開口70aを形成した後に、第1の保護膜70及び第1の開口70aから露出する上部電極63の上方に層間絶縁膜71を形成する工程と、層間絶縁膜71に、第1の開口70aの内側で上部電極63に達する第1のホール71aを形成する工程と、第1のホール71aに第1の導体プラグ77aを埋め込む工程とを含む半導体装置の製造方法による。

(もっと読む)

半導体装置、及び薄膜キャパシタの製造方法

【課題】 下部電極となるTiN膜の表面のラフネスを低減させるために、化学機械研磨、Arによるスパッタリング、Ta膜の堆積等の工程が必要になる。

【解決手段】 半導体基板(10)の上に薄膜キャパシタが配置されている。この薄膜キャパシタは、少なくとも表層部が非晶質または微結晶の金属で形成された下部電極(21a,22a)、該下部電極の上に配置された誘電体膜(23a)、及び該誘電体膜の上に配置された上部電極(24a)を含む。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の異なる半導体層上においても、良好にゲート電極を形成可能な半導体装置の製造方法を提供する。

【解決手段】絶縁体2上の膜厚の異なる半導体層3a,3bにそれぞれ形成された電界効果型トランジスタを有する半導体装置の製造方法である。まず、膜厚の異なる半導体層3a,3bを絶縁体上に形成する。そして、半導体層3a,3b上にゲート絶縁膜5a,5bを形成し、ゲート絶縁膜5a,5b上にゲート電極材料を積層する。パターニング時におけるフォトリソグラフィに影響を与えない膜厚を有する犠牲膜をゲート電極材料上に形成し、エッチングにより犠牲膜をパターニングするとともに、パターニングされた犠牲膜8aをマスクに用いてゲート電極材料をパターニングしてゲート電極11,12を形成する。

(もっと読む)

半導体装置の製造方法

【課題】アルミニウム膜のウェットエッチングは、等方性のエッチング特性が知られているが、ウエハを高速回転させているため、回転に伴う異方性が現れるため、ウエハ外周部の配線形状を管理することが困難であった。

【解決手段】アルミニウム膜のウエット・エッチングにおいて、フルコーンノズルを2本搭載し、1本のノズルをウエハ全面へ薬液が塗布可能な位置に設置し、もう1本のノズルを薬液濃度が薄くなるウエハ中心部(ウエハ直近の位置)に設置し同時に薬液を塗布することにより、回転数依存が少なくエッチングレート均一性を向上することが可能とするものである。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】

CMOS装置の製造工程におけるコンタクト不良発生を抑制する。

【解決手段】

半導体装置の製造方法は、(a)Si基板に、n型の第1の活性領域、p型の第2の活性領域を形成する工程と、(b)活性領域に、第1、第2のゲート電極構造、第1、第2のソース・ドレイン領域をそれぞれ形成する工程と、(c)第1のソース/ドレイン領域に、凹部を形成する工程と、(d)凹部にSi−Geを含むp型の圧縮応力を有する半導体エピタキシャル層を形成する工程と、(e)半導体基板上に引張応力を有する窒化シリコンのエッチストッパ膜、層間絶縁膜を形成する工程と、(f)層間絶縁膜、エッチストッパ膜を貫通して、コンタクト孔をエッチングする工程と、(g)半導体基板上方に酸素を含むプラズマを発生する工程と、(h)コンタクト孔に導電性プラグを埋め込む工程と、を有する。

(もっと読む)

積層配線構造体及びその製造方法並びに半導体装置及びその製造方法

【課題】積層した導電体層を駆動回路などに接続する部分の製造効率を向上し、且つ信頼性を向上させること。

【解決手段】本発明の積層配線構造体は、導電体層と絶縁層とが交互に積層された積層部と、最上層の絶縁層から形成され導電体層それぞれに達し、側面が導電体層と絶縁膜を介して形成された複数のコンタクトと、を有している。また、コンタクトのうち少なくとも1つは、導電体層で区切られた複数の部分を有し、

上層の導電体層に区切られるコンタクトの内径より、下層の導電体層に接続されるコンタクトの開口部の内径が小さいことを特徴とすることもできる。

(もっと読む)

MIMキャパシタ及びその製造方法

【課題】製造工程を改善することで製造効率を向上できるとともに、集積度を向上させることで半導体素子の価格を低下できるMIMキャパシタ及びその製造方法を提供する。

【解決手段】半導体基板110上に形成される下部金属層140と、下部金属層140上に形成される上部金属層160と、下部金属層140と上部金属層160との間に形成される誘電層150と、上部金属層160上に形成される第1ボンディングメタル層170及び下部金属層140上に形成される第2ボンディングメタル層180と、上部金属層160と第1ボンディングメタル層170との間に形成され、上部金属層160と第1ボンディングメタル層170とを直接接続させる第1接続配線172と、下部金属層140と第2ボンディングメタル層180との間に形成され、下部金属層140と第2ボンディングメタル層180とを直接接続させる第2接続配線182とを備えてMIMキャパシタ100を構成する。

(もっと読む)

プログラマブル素子及びそのプログラマブル素子を有する半導体装置の製造方法。

【課題】 プログラム特性の良好なプログラマブル素子及びそのプログラマブル素子を有する半導体装置の製造方法を提供することを目的とする。

【解決手段】 半導体基板100と、半導体基板100表面に離間して形成されたソース/ドレイン層103と、ソース/ドレイン層103間の半導体基板100上に形成されたHfを含有する電荷トラップ膜を有するゲート絶縁膜105と、ゲート絶縁膜105上に形成されたプログラム電位が印加されるゲート電極106を備えることによって、FPGA等のプログラマブルロジックデバイスに使用されるプログラマブル素子のプログラム特性を向上する。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜をドライエッチングしてコンタクトホールを形成する際に、高耐圧トランジスタのゲート絶縁膜が受けるダメージを低減できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上にHVトランジスタ10のゲート電極13と、LVトランジスタ20のゲート電極23と、ダミーゲート電極53とを同時に形成する工程と、シリコン基板1上に層間絶縁膜30を形成する工程と、層間絶縁膜30を部分的にドライエッチングして、ゲート電極13、23、ダミーゲート電極53上にそれぞれコンタクトホール31、33、34を形成する工程と、を含み、コンタクトホール31、33、34を形成する工程では、コンタクトホール31の底面からゲート電極13の表面が露出すると同時に、又はそれよりも前に、コンタクトホール34の底面からダミーゲート電極53の表面が露出するように層間絶縁膜30をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】プラグまたは局所配線による接続で低い接続抵抗と十分に小さい拡散層リーク電流を実現し、更に深さが異なる接続孔や開口断面の断面の形状や大きさが異なる接続孔または局所配線穴を用いる場合でも、十分に小さい拡散層リーク電流と低い接続抵抗を実現する製造方法を提供する。

【解決手段】基体上の絶縁膜に開口した、表面がシリコンを主成分とする層が底部に露出している第1の開口部(接続孔または局所配線穴)の群と、表面が第1の金属珪化物を主成分とする層が底部に露出している第2の開口部の群と、表面が第1の金属を主成分とする層が底部に露出している第3の開口部の群のうちの、少なくとも2群の各開口部の底部に、第2の金属珪化物を主成分とする層また第2の金属を主成分とする層を、化学気相成長法によって同時に形成する。

【効果】従来以上に高集積、高性能の半導体装置が実現される。

(もっと読む)

ボイドの無いコンタクトプラグ

コンタクトプラグを形成する半導体素子形成プロセスでは、チタンまたはタンタルコンタクト層(30)、窒化チタンバリア層(40)、及びタングステンシード層をコンタクト開口部(24)に順番に堆積させる。次に、コンタクトホール(24)への充填を、コンタクト開口部の底面から上に向かって、銅層(60)を電気メッキすることにより行なって、ボイドがコンタクト開口部(24)内に形成されることがないようにする。全ての余分な材料をCMPプロセスにより除去してコンタクトプラグ(70)を形成し、この場合、CMPプロセスを使用して、コンタクト層/シード層/バリア層(30,40,50)のうちの一つ以上の層を薄くする、または除去することもできる。  (もっと読む)

(もっと読む)

21 - 40 / 58

[ Back to top ]