Fターム[5F033QQ46]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337)

Fターム[5F033QQ46]の下位に属するFターム

機械的研磨 (214)

化学的機械的研磨(CMP) (3,638)

ストッパー膜、研磨速度調整膜 (245)

研磨材、研磨液 (82)

Fターム[5F033QQ46]に分類される特許

141 - 158 / 158

貫通電極付基板の製造方法

【課題】 何ら不具合が発生することなく、半導体基板に貫通電極が設けられた構造の貫通電極付基板の製造方法を提供する。

【解決手段】 仮基板10上に、該仮基板10から剥離できる状態で金属ポスト18aを形成する工程と、金属ポスト18aに対応する位置に貫通孔20xが設けられた正規の基板20を仮基板10の上に配置することにより、正規の基板20の貫通孔20xに仮基板10上の金属ポスト18aを挿入する工程と、仮基板10を金属ポスト18aから剥離することにより、正規の基板20を貫通する金属ポスト18aからなる貫通電極18を得る工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】 基板を貫通する貫通配線などの導電材層と基板との間に安定して絶縁材層を形成することができ、また導電材層の厚みを均一にして貫通配線を安定して形成することのできる半導体装置の製造方法を提供する。

【解決手段】 半導体基板11に半導体基板11の一方の表面部21側から半導体基板11の厚み方向に延びる筒状の絶縁材充填用孔25を形成して、絶縁材充填用孔25の内方に、残留する半導体基板11からなる柱状体26を形成する。形成された絶縁材充填用孔25に絶縁材料を充填して筒状の絶縁材層27を形成した後、柱状体26を除去して絶縁材層27の内方に柱状の導電材充填用孔29を形成する。形成された導電材充填用孔29に導電材料を充填して、絶縁材層27で囲繞された導電材層30を形成する。これによって、導電材層30と半導体基板11との間に絶縁材層27を安定して形成することができる。また導電材層30の厚みを均一にすることができる。

(もっと読む)

電解研磨電解質および前記電解質を使用して金属層を平坦化する方法

本発明の電解研磨電解質は酸溶液および少なくとも1個のヒドロキシル基を有するアルコール添加剤を含有し、その際アルコール添加剤の接触角が電解研磨下の金属層上の酸溶液にお接触角より小さい。アルコール添加剤はメタノール、エタノールおよびグリセリンから選択され、酸溶液が燐酸を含有する。グリセリンと燐酸の体積比は1:50〜1:200であり、有利に1:100である。メタノールと燐酸の体積比は1:100〜1:150であり、エタノールと燐酸の体積比は1:100〜1:150である。酸溶液は更に酢酸およびクエン酸からなる群から選択される有機酸を含有する。酢酸の濃度は10000〜12000ppmであり、クエン酸の濃度は500〜1000ppmである。  (もっと読む)

(もっと読む)

厚さの計測値を使用した適応型の電解研磨と障壁及び犠牲層の除去

半導体ウエハ上に形成された金属層を適応的に研磨する。金属層の一部分が電解研磨され、金属層のその他の部分が別個に電解研磨される。電解研磨の前に、金属層の研磨部分の厚さの測定値が決定される。電解研磨量は厚さの測定値に基づいて調整される。半導体ウエハ上に形成される金属層が研磨され、その金属層は障壁層上に形成されており、障壁層は凹部領域と非凹部領域を有する誘電体層上に形成され、さらに金属層は凹部領域と非凹部領域をカバーする。非凹部領域をカバーする金属層を取り除くために金属層が研磨される。凹部領域中の金属層を非凹部領域以下の高さにまで研磨するが、この高さは障壁層の厚さと等しくあるいはそれよりも大きい。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、ウェーハ周辺のエッジリンスやCMP法に依る研磨を行っても、多層配線構造に於ける構成材料の剥離に起因する異物の発生が抑制されて、高品質の半導体装置を高い歩留りで製造することができ、併せて、ビアホールや配線溝を形成するエッチングを行った場合、Cu層に損傷が発生しないようにする。

【解決手段】 多層配線を形成する工程を含む半導体装置の製造方法であって、第1の低誘電層3と第2の絶縁層4とに形成した第1の配線溝を埋めるCuからなる第1の配線7Aは、そのウェーハ周辺側端縁がハードマスクを兼ねる第1の低誘電層3のウェーハ周辺領域側端縁を越えるように形成し、その後、第1の配線7Aを保護する為に形成する第1のブロック層8が第1の低誘電層3と接触することがないようにし、以下、絶縁層を介して上記低誘電層以下の積層及び加工の工程を繰り返して多層配線を形成する。

(もっと読む)

配線形成方法及び配線形成装置

【課題】 配線金属膜の表面を酸化や汚染などのダメージから保護し、その後の平坦化工程をより容易しつつ、配線を形成できるようにする。

【解決手段】 絶縁膜内に配線用凹部42を形成し表面をバリア膜44で覆った基板Wを用意し、基板Wの表面に配線金属膜48を形成して配線用凹部42内に配線金属を埋込み、配線金属膜48の表面に高分子保護膜50を形成する。

(もっと読む)

半導体ウエハ支持板及び半導体装置の製造方法

【課題】 半導体ウエハの貫通孔部分のメッキ加工等の加工を容易にかつ良好に行うことができ、生産効率良く良好な半導体装置を製造することができる半導体ウエハ支持板及び半導体装置の製造方法を提供する。

【解決手段】 半導体ウエハ支持板1は、紫外線が透過可能なガラス若しくは樹脂から略円板状に形成され、その外径は、支持する半導体ウエハ10の外径より大きく設定されている。半導体ウエハ支持板1には、半導体ウエハ10に形成されている複数の貫通孔11に対応して、複数の開口2が形成されている。これらの開口2は、貫通孔11の開口面積よりも開口面積が広く、すなわち、開口径が大きく設定されている。

(もっと読む)

配線パターン形成方法、TFT用ソース電極およびドレイン電極の形成方法

【課題】 液滴吐出装置から液滴を吐出してTFT用ソース電極またはドレイン電極を設けること。

【解決手段】 配線パターン形成方法は、バンクパターンに縁取られたパターン形成領域における所定のセクションへ液状の導電性材料の液滴を吐出して、パターン形成領域を覆う導電性材料層を形成するステップ(A)を含んでいる。セクションのX軸方向に沿った長さをLとし、Y軸方向に沿った長さをMとすると、吐出される液滴の直径φは、L以下であるとともに、M以下である。そして、ステップ(A)は、バンクパターンから少なくとも直径φの1/2倍離れた位置に液滴の中心が当たるように、液滴を吐出するステップ(a1)を含んでいる。

(もっと読む)

電解研磨のためのシステムと方法

【課題】電解研磨のためのシステムと方法を提供する。

【解決手段】本発明は、半導体ウェハの導電性表面を電解研磨する処理を提供する。この処理中、コンタクト溶液中のコンタクト電極は、導電層の表面上のコンタクト領域にコンタクト溶液を接触させる。さらに、この処理中、処理溶液中の処理電極は、導電性表面上の処理領域に処理溶液を接触させ、同時に、コンタクト電極と処理電極との間に電位差を与えて、処理領域の導電層の表面を電解研磨する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 ヒューズの飛び散りを原因とする、回路素子、配線、及び半導体基板に対する損傷を防止できる半導体装置を提供する。

【解決手段】 表面に回路素子が設けられた半導体基板上に絶縁層が形成され、絶縁層上にレーザートリミングされるヒューズが形成され、ヒューズ上に保護膜が形成されてなる半導体装置であって、ヒューズ近傍に少なくとも1以上の空洞を形成してなる。

(もっと読む)

半導体装置及び同半導体装置の製造方法

【課題】

半導体装置の内部で発生する熱を効率よく外部へ発散させることによって半導体素子の動作特性の劣化を防止することができる半導体装置及びこの半導体装置の製造方法を提供する。

【解決手段】

表面に半導体素子を形成した半導体基板の裏面全体に放熱電極を形成し、この放熱電極に導通するバイアホールを形成した半導体装置を製造する際に、半導体基板の裏面に凹部を形成し、その後、この凹部とバイアホールの内面とに放熱電極を形成することによって放熱電極に凹部を設けた。

(もっと読む)

半導体装置及びその製造方法

【課題】 ボンディング工程、CMP工程、熱応力等による機械的衝撃やウエハの変形によるビアの変位を小さく制御できる半導体装置及びその製造方法を提供する。

【解決手段】 第1配線22と、第1配線22の上に配置された低誘電率絶縁膜310と、低誘電率絶縁膜310の中に第1配線22と接続するように埋め込まれ、第1配線22の長手方向に測った第1長さLx、第1配線22が配置された平面で第1配線22に直交する方向に測った第2長さLy、第1配線22が配置された平面に垂直な高さHに対する第1及び第2長さLx,Lyの少なくとも一方との比が1以上である複数の第1扁平ビア31a,31bと、低誘電率絶縁膜310の上に配置され、複数の第1扁平ビア31a,31bにそれぞれ接続された第2配線32とを備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ダマシン配線に含まれる不純物の濃度を低下させて、配線中の欠陥を低減させる事が可能な半導体装置の製造方法を提供する。

【解決手段】ウェハW上の層間絶縁膜1に幅が0.3μm以下の細幅配線溝1a及び幅が0.3μmを超える太幅配線溝1bを形成する。層間絶縁膜1上にバリアメタル膜2及びシード膜3を形成する。その後、細幅配線溝1a全体に埋め込まれ、かつ太幅配線溝1bの一部に埋め込まれるように膜4を電解めっき法により形成する。太幅配線溝1bの他の部分に埋め込まれるように膜4よりも不純物濃度が低い膜5をスパッタ法により形成する。熱処理により膜4中の不純物を膜5中に拡散して、配線膜6を形成する。最後に層間絶縁膜1上の不要なバリアメタル膜2及び配線膜6を除去し、細幅配線と太幅配線を形成する。

(もっと読む)

アクティブマトリクス型液晶表示装置及びその製造方法

【課題】アクティブマトリクス型液晶表示装置において、データライン等による反射光の干渉を抑止し、LCDパネルに虹状のむらが生じるのを防止する。

【解決手段】アクティブマトリクス型液晶表示装置において、距離的に周期性を有して配置されている構成要素、例えば、データライン10、ゲートライン20、補助容量ライン30、能動層61については、これらの表面に入射する外光による反射による反射光の干渉が生じ、虹状の表示むらが発生する。これらの表面に、複数の凹部及び凸部が形成し、互いに隣接する凸部の間隔及び互いに隣接する凹部の間隔に距離的な周期性がないようにすることで、反射光の干渉をなくす。距離的に周期性を有して配置されている構成要素の全てにそのような複数の凹部及び凸部を形成することが好ましいが、少なくとも1つの構成要素にそのような複数の凹部及び凸部を形成してもよい。

(もっと読む)

付着材料を除去するための反応性流体システムおよびそれを使用するための方法

本発明は、一般に材料を処理するための方法に関する。より詳細には、本発明は反応性流体、および被覆材料、金属、非金属、層状材料、有機物、ポリマーおよび半導体材料を非限定的に含む付着材料を除去するための反応性流体の使用に関する。本発明は、半導体チップ生産のような商用プロセスに適用することが可能である。

(もっと読む)

(もっと読む)

低減された層内静電容量を有する集積回路の配線構造

【課題】

【解決手段】集積回路の配線構造を形成する方法が、誘電材料の層(13)内に複数のフィーチャ(16)を形成するステップと、フィーチャの側壁(16s)にスペーサ(20)を形成するステップとを含む。次に、スペーサによって側壁から分離された導体(25)をフィーチャ内に形成する。その後、スペーサを除去して側壁のところに空隙(40)を形成し、それによって導体が空隙によって側壁から分離されるようにする。導体の上下の誘電体層(42、12)は、導体間の誘電体の誘電率よりも低い誘電率を有する低k誘電体とすることができる。各導体(25)の断面は、低k誘電体層(12)と接触する底部と、他の低k誘電体(42)と接触する上部と、空隙(40)とのみ接触する側面とを有する。空隙は、層内静電容量を低減する機能を果たす。

(もっと読む)

電気コンタクトを対向する両側に有する半導体素子及びその形成方法

半導体(10)はトランジスタのような能動素子を有し、この能動素子はキャパシタ(75,77,79)のような受動素子の直下に位置し、能動素子及び受動素子はビアまたは導電領域(52)及び配線(68,99)によって接続される。ビアまたは導電領域(52)はトランジスタの拡散領域またはソース領域(22)の底面にコンタクトし、更にキャパシタ電極の内の第1電極(75)にコンタクトする。横方向に位置する縦型ビア(32,54,68)及び配線(99)はキャパシタ電極の内の第2電極(79)にコンタクトする。金属配線または導電材料(68)は電源プレーンとして使用することができ、この電源プレーンは、電源プレーンをトランジスタに隣接させるのではなくトランジスタの下に位置するように用いることによって回路面積を節約するように作用する。  (もっと読む)

(もっと読む)

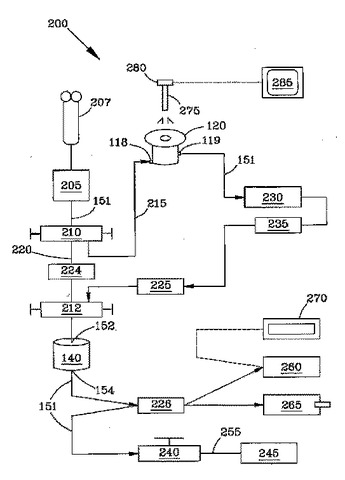

電解加工装置及び電解加工方法

本発明は、被加工物の不良品化を招くと考えられるピットの発生を効果的に防止することができるようにした電解加工装置及び電解加工方法を提供する。この電解加工装置は、被加工物を加工する加工電極(210)と、被加工物に給電する給電電極(212)と、加工電極(210)と給電電極(212)との間に電圧を印加する電源(232)と、加工電極(210)及び給電電極(212)を内部に収納した耐圧容器(200)と、耐圧容器(210)内に高圧液体を供給する高圧液体供給系(204)を有する。  (もっと読む)

(もっと読む)

141 - 158 / 158

[ Back to top ]