Fターム[5F033QQ46]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337)

Fターム[5F033QQ46]の下位に属するFターム

機械的研磨 (214)

化学的機械的研磨(CMP) (3,638)

ストッパー膜、研磨速度調整膜 (245)

研磨材、研磨液 (82)

Fターム[5F033QQ46]に分類される特許

101 - 120 / 158

半導体装置の製造方法

【課題】配線の表面にホイスカが残留するのを抑制する。

【解決手段】下地112に支持された絶縁膜115にコンタクトホール120を形成し、絶縁膜の上およびコンタクトホールの内に付着するメタルがコンタクトホールを充満する程度に溶融する第1温度に下地を加熱した状態で、当該メタルをスパッタリングすることにより、絶縁膜の上およびコンタクトホールの内に第1メタル膜130を成膜し、さらに、第1温度よりも低くかつ第1メタル膜の上に付着するメタルが溶融しても流動しない程度に抑制された第2温度に下地を加熱した状態で、当該メタルをスパッタリングすることにより、第1メタル膜の上に第2メタル膜135を成膜する。

(もっと読む)

半導体装置

【課題】互いに積層される半導体チップ間の接続信頼性を確保するために電極の面積を大きくすると、その電極と半導体層との間に発生する静電容量が増大してしまう。

【解決手段】半導体装置1は、半導体チップ10を備えている。半導体チップ10は、半導体基板12、配線層14、裏面電極16(第1の本電極)、および裏面ダミー電極17(第1のダミー電極)を有している。半導体基板12上には、配線13を含む配線層14が形成されている。また、半導体基板12の裏面S1上には、配線13と電気的に接続された裏面電極16が形成されている。この裏面S1上には、配線13と電気的に絶縁された裏面ダミー電極17も形成されている。

(もっと読む)

半導体装置

【課題】 全表面を絶縁材で覆われた半導体装置において、放熱性を良くする。

【解決手段】 シリコン基板4、入出力用の柱状電極14および放熱用柱状電極15を有する半導体構成体2の下面、側面および上面は、樹脂等からなるベース板1、絶縁層17、絶縁層18およぴオーバーコート膜25によって覆われている。そして、半導体構成体2の放熱用柱状電極15(放熱用再配線13および放熱用下地金属層12を含む)に接続された放熱層23(放熱用下地金属層22を含む)は、オーバーコート膜25の開口部28を介して外部に露出されている。これにより、放熱性を良くすることができる。

(もっと読む)

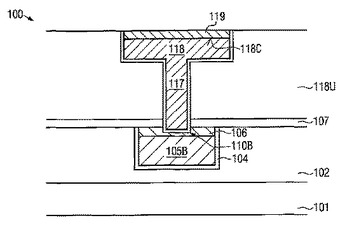

導電性キャッピング層を含む銅ベースのメタライゼーション層を形成する技術

金属ベースの相互接続線に対して導電性キャッピング層(106)を設けることで、エレクトロマイグレーションに対するパフォーマンスを強化することができる。さらに、銅ベースの材料などの下方の金属(105b)を露出せずにビア開口部(110)をキャッピング層(106)に確実にエッチングし、これによりエレクトロマイグレーションパフォーマンスを具体的には銅線とビアの間の遷移において強化することができる。  (もっと読む)

(もっと読む)

厚さの計測値を使用した適応型の電解研磨と障壁及び犠牲層の除去

【課題】半導体ウエハ上に形成された金属層を効果的に研磨する。

【解決手段】半導体ウエハ上に形成された金属層(612)を研磨する方法であって、この金属層(612)は、障壁層(604)上に形成されており、障壁層(604)は、凹部領域(606)と非凹部領域(610)を具備する誘電体層(608)上に形成されており、この金属層(612)は、誘電体層の凹部領域(606)と非凹部領域(610)を覆っているものにおいて、金属層(612)を研磨し、非凹部領域(610)を覆っている金属層(612)を除去する段階と、凹部領域(606)内の金属層を非凹部領域(610)の高さに研磨する段階であって、この高さを障壁層(604)の厚さ以上とする方法。

(もっと読む)

半導体装置およびその作製方法

【課題】基板上に設けられた半導体素子を複数積層させた場合であっても、積層した半導体素子が基板を通して電気的に接続可能となる半導体装置およびその作製方法を提供することを目的とする。

【解決手段】基板の一方の面に選択的に凹部または基板の一方の面から他方の面に貫通する開口部を形成し、基板の一方の面および凹部または開口部を覆うようにトランジスタを有する素子群を形成し、基板を他方の面から薄膜化することによって、凹部または開口部に形成された素子群を露出させることを特徴としている。基板を薄膜化する手段としては、基板の他方の面から研削処理、研磨処理、化学処理によるエッチング等を行うことによって基板を部分的に除去することによって行うことができる。

(もっと読む)

電解加工装置および電解加工方法

【課題】例えばダマシン法により基板上の配線を形成する場合に、基板にダメージを与えることなく、低い圧力で基板の表面を全面にわたって均一に平坦化することができる電解加工装置を提供する。

【解決手段】電解加工装置10は、表面に金属膜が形成されたウェハを保持しつつ、ウェハを回転させるウェハホルダ14と、ウェハに対して電解加工を行う電解加工ユニット16とを備えている。電解加工ユニット16は、回転可能な加工電極52と、加工電極52に取り付けられた研磨パッド53と、研磨パッド53をウェハに押圧する押圧機構72と、電解加工液をウェハと加工電極52との間に供給する液供給機構と、ウェハと加工電極52とを相対運動させる相対運動機構と、加工電極52がカソード、ウェハの金属膜がアノードとなるように、加工電極52とウェハの金属膜との間に電圧を印加する電源103とを備えている。

(もっと読む)

電解加工方法および基板処理方法

【課題】ダマシーン法による基板上の配線形成において、微細な凹凸を有する基板上の金属膜の表面を低い加工圧力で平坦化することができ、かつ金属膜をその全面に亘って均一な加工速度で加工することができる電解加工方法を提供する。

【解決手段】給電電極31と加工電極32とをテーブル12上に配置し、給電電極31と加工電極32の間に絶縁体36を配置し、金属膜6が給電電極31および加工電極32に対向するように基板Wを絶縁体36に接触させ、第1の電解液および第2の電解液を、絶縁体36により電気的に絶縁させた状態で給電電極31と基板Wとの間、および加工電極32と基板Wとの間にそれぞれ供給し、給電電極31と加工電極32との間に電圧を印加し、基板キャリアー11とテーブル12を相対運動させて基板W上の金属膜6の電解加工を行う。

(もっと読む)

電子部品実装構造体及びその製造方法

【課題】 貫通電極が設けられたシリコン基板(インターポーザ)に信頼性よく封止キャップを設けることができる電子部品実装構造体を提供する。

【解決手段】 両面側の配線層32,26が貫通電極16を介して相互接続された構造を有するシリコン回路基板1の上に、電子部品40が実装又は形成され、ガラスよりなるリング状の突起状接合部50bとそれによってキャビティ50aが構成された構造の封止キャップ50xの突起状接合部50bがシリコン回路基板1の接合部10bに陽極接合されている。これによって、電子部品40が封止キャップ50xのキャビティ50a内に気密封止されている。

(もっと読む)

半導体技術における微細ピッチの製造方法

【課題】従来よりも小さいピッチを有した半導体デバイスにおいて周期パターンの製造方法を提供する。

【解決手段】周期的構造を有するパターン層の細片様構造の側壁にスペーサ5が形成される。そして、該パターン層が除去され、該スペーサが、第2の側壁スペーサとなる別のスペーサ層7によって覆われる。上記スペーサとスペーサとの間は補充層8によって充填される。上記第1のスペーサ5と、第2のスペーサ7と、上記補充層の残留部分8とが周期的に連続している部分を残して、表面を平坦化する。横寸法は、1つ以上の残留層を除去することによってピッチの小さい周期パターンが形成されるように調節される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ダマシン法を用いて形成された銅配線の絶縁破壊耐性(信頼性)を向上する。

【解決手段】シリコン酸化膜39の配線溝40に埋め込むCu配線46a〜46eをCMPを用いた研磨で形成する。それから、CMP後の洗浄工程を経た後に、シリコン酸化膜39およびCu配線46a〜46eの表面を還元性プラズマ(アンモニアプラズマ)で処理する。その後、真空破壊することなく、連続的にキャップ膜(シリコン窒化膜47)を形成する。

(もっと読む)

半導体装置の形成方法およびその構造

【課題】エアギャップを形成する際にミスアライメントビアがエアギャップを貫通するのを極力低減すること。

【解決手段】ダミーフィーチャ(48a,48b)が、層間誘電体層(36)内に形成される。一実施形態では、非ギャップ充填誘電体層(72)がダミーフィーチャ上に形成され、ダミーフィーチャ間、またはダミーフィーチャと導電領域(44)間に空隙(74)を形成する。一実施形態では、パッシベーション膜(32および54)が無電解めっきによって形成され、下層にある導電性領域(44,48a,48b,および30)をエアギャップ(74)が貫通するのを保護する。さらに、パッシベーション膜は、下層にある導電性領域に覆い被さって、それにより、導電性領域に隣接するダミーフィーチャを画定する。パッシベーション膜は、追加のパターニング工程なしに形成することができ、ミスアライメントビアがエアギャップを貫通するのを極力低減する。

(もっと読む)

貫通ウェーハ相互接続

貫通ウェーハ相互接続および同相互接続を製造する方法が開示される。本方法は、導電ウェーハの材料を除去することによって、パターン形成したトレンチを形成するために導電ウェーハから出発する。パターン形成したトレンチは、深さがウェーハの前面から裏面に達し、全体的に導電ウェーハを内部分と外部分とに分割する環状開口部を有し、それによって導電ウェーハの内部分は、外部分から絶縁されて貫通ウェーハ導体としての役目をする。誘電材料が、パターン形成したトレンチの中へ形成または追加され、貫通ウェーハ導体を機械的に支持しおよび電気絶縁する。多導体を、アレイとして形成することもできる。  (もっと読む)

(もっと読む)

半導体装置、積層半導体装置およびそれらの製造方法

【課題】高抵抗化や接触不良の低減が可能になるように改良された半導体装置を提供することを主要な目的とする。

【解決手段】配線層106を持つ半導体装置150a、150b、150cにおいて、その表面から裏面に達する貫通孔110が存在し、貫通孔110の内壁には、各配線層106の側壁の一部が露出している。貫通孔110の内部には導電材料112が存在し、該貫通孔110内で、各配線層106の側壁の一部と、導電材料112が電気的に接続されている。この発明によれば、半導体装置150a、150b、150cを積層する際の、積層段数増加による貫通孔形成用マスク数の増加無く形成する事ができ、同一設計寸法の貫通孔110で全ての半導体装置を形成できる為、半導体装置面積の縮小もできる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法の薄型化・貫通電極形成工程において、主面から内部に向けて非貫通電極が形成された半導体基板の主面に対向する裏面の研磨により、非貫通電極を構成する導電材料が裏面に露出するのを精度良く検知し、導電材料の露出不良、研磨し過ぎなどを防止する。

【解決手段】 主面5からその内部に向けて非貫通電極7が形成される半導体基板2と、異方性導電フィルム3と、導電性支持体4とを貼り合わせた研磨構造体1を作製し、研磨面6の研磨により非貫通電極7を構成する導電材料が研磨面6表面に露出すると電流が流れるように電圧を印加し、半導体基板2の厚み方向における電気抵抗値の変化により導電材料の露出を検知する。

(もっと読む)

半導体装置とその製造方法

【課題】 配線に対する膜剥がれや腐食等の不具合が発生せず、高密度で高速動作が可能な半導体装置とその製造方法を提供する。

【解決手段】 第1の配線パターン3の表面にSRO膜9Aを形成し、この配線パターン3を埋めるようにSRO膜9Aの表面全体に比誘電率が低いFSG膜5Aを形成する。FSG膜5Aの表面全体にSRO膜9Bを形成し、更にこのSRO膜9Bの表面全体にFSG膜5Bを形成し、このFSG膜5Bの表面を平坦化する。FSG膜5Bの表面にほぼ一定の膜厚でSRO膜9Cを形成し、このSRO膜9C上に配線パターン7を形成する。配線パターン3,7間は、必要に応じて金属製のヴィアプラグ8で接続される。SRO膜は弗化水素を捕獲する性質があるので、ヴィアプラグ等の形成時の熱処理でFSG膜から発生する弗化水素をトラップし、配線パターンへの影響を無くすことができる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体ウェハの一面側にメッキにより形成されたメッキ膜を形成するとともに、半導体ウェハをその他面側から薄肉化するようにした半導体装置の製造方法において、ウェハの反りを実用レベルまで低減する。

【解決手段】 半導体ウェハ100の表面100a側にメッキ膜13を形成した後、半導体ウェハ100をその他面100b側から薄肉化して所望の厚さにするようにした製造方法において、半導体ウェハ100を薄肉化する工程では、半導体ウェハ100の他面100b側を研削して、半導体ウェハ100の反りが1.3mm以下となるように半導体ウェハ100を所望の厚さよりも厚い状態にとどめた後、研削された半導体ウェハ100の他面100b側をウェットエッチングにより除去し、半導体ウェハ100を所望の厚さとする。

(もっと読む)

半導体装置

【課題】貫通電極を備えた半導体チップを積層した3次元半導体装置において、貫通電極と半導体基板間の容量が大きく、高速データ転送ができないという問題と、貫通電極を形成する導電膜の埋め込み時間が長く、導電膜質が不均一という問題がある。

【解決手段】貫通電極を、内部貫通電極12、リング状半導体11a、外周貫通電極14とで構成する。内部貫通電極12は、等間隔のスペースで柱状半導体を配置することで、薄い膜厚の導電膜により形成することができる。さらにリング状半導体11aと外周貫通電極14とをフローティング状態とすることで、内部貫通電極12と半導体基板11の間に生じる容量が小さくなる。容量が小さくなることで高速データ転送が可能な、生産しやすい構造を有する貫通電極が得られる。

(もっと読む)

基板中の電気的接続

本発明は、導電性又は半導電性の基板の第1(上側)表面と第2(下側)表面との間に電気的接続を作る方法に関する。本発明は、第1表面にトレンチを作成、前記トレンチによって規定される前記基板の一部分を完全に分離する絶縁性囲いの設置を含む。本発明は、また、マイクロエレクトロニック及び/又はマイクロメカニック素子の製造用の出発基板として用いることができる製造物に関し、平坦な半導電性又は導電性基板を含み、第1表面及び第2表面、及び前記基板を貫通して伸びる少なくとも一つの電気的接続部材を有する。電気的接続部材は、絶縁性材料からなる限定された層によって平坦な基板からなる周辺材料から絶縁されており、基板と同じ材料を含んでいる、すなわち、ウエハ材料から作られている。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 下面を研削されたシリコン基板の下面および側面にクラックが発生しにくいようにする。

【解決手段】 シリコン基板1の下面側を適宜に研削し、次いで第1のダイシングストリート21に沿って、シリコン基板1の下面側から封止膜10の途中までハーフカットし、溝12を形成する。この場合、シリコン基板1の下面および周側面に微細で鋭角な凸凹(シリコンの結晶破壊層)が形成される。次に、ウェットエッチングにより、シリコン基板1の下面および周側面を段差1〜5μmの粗面仕上げとする。次に、溝12内を含むシリコン基板1の下面にエポキシ系樹脂などからなる保護膜13を形成する。この場合、シリコン基板1の下面および周側面は段差1〜5μmの粗面となっているので、この粗面は保護膜13によって確実に覆われ、シリコン基板の下面および側面にクラックが発生しにくいようにすることができる。

(もっと読む)

101 - 120 / 158

[ Back to top ]