Fターム[5F033QQ48]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | 化学的機械的研磨(CMP) (3,638)

Fターム[5F033QQ48]に分類される特許

201 - 220 / 3,638

半導体装置及びその製造方法

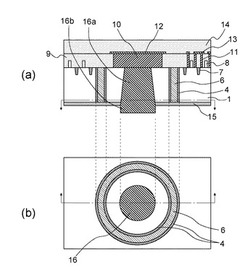

【課題】半導体基板を貫通する貫通電極の周囲に形成される環状の絶縁分離部において、絶縁分離部を構成する酸化膜の応力により絶縁分離部周囲の半導体基板が変形する。

【解決手段】絶縁分離部の基板側に深さ方向に圧縮応力を与える第1の膜4を形成し、第1の膜4上に深さ方向に引張応力を与える第2の膜6膜を形成し、その際、第1及び第2の膜の膜厚を圧縮応力と引張応力とがほぼ釣り合うように調整する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13内、ビア孔14内および層間絶縁膜12上に、チタン、ジルコニウムおよびマンガンのうちのいずれか、もしくはこれらの合金である金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、トレンチ溝13の底部および側壁とビア孔14の側壁に、タンタル、タングステンのいずれか、もしくはこれらの合金である金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置にダミーパタンを配線空隙に効率よく製造容易的に形成する。

【解決手段】多層配線構造の半導体装置において、狭い配線空隙(Area_S1)に、広い配線空隙(Area_S2)に形成されたダミーパタン(22,23)と異なる向きのダミーパタン(21)が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体積層体の製造方法

【課題】信頼性の高い半導体積層体を製造することのできる半導体積層体の製造方法を提供する。

【解決手段】貫通電極用溝2が形成されたウエハ1の貫通電極用溝2を有する面に、半導体加工用テープ4を介して支持体5を積層する工程(1)と、ウエハ1を半導体加工用テープ4と反対側の面から研削し、貫通電極用溝2を露出させる工程(2)と、露出した貫通電極用溝2に電極部6を形成する工程(3)と、ウエハ1の半導体加工用テープ4と反対側の面に封止樹脂層7を形成する工程(4A)と、封止樹脂層7を介してウエハ1にダイシング用テープ8を貼り合わせ、半導体加工用テープ4及び支持体5を剥離する工程(4B)と、ウエハ1を個片化して半導体チップを作製する工程(5)と、前記半導体チップを、封止樹脂層7を介して他の半導体チップ又は基板に積層する工程(6)とを有する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】耐圧確保に有利な構造を提供する。

【解決手段】実施形態の半導体記憶装置は、基板上で所定方向に平行に延伸した複数の素子分離領域と、隣接する素子分離領域に挟まれた素子領域上の第1絶縁膜と、素子領域上の所定方向に間隔を空けて形成され、第1絶縁膜の上に順に積層された電荷蓄積層、第2絶縁膜、及び制御ゲート電極をそれぞれ有する複数のワードラインと、その両側に1つずつ配置され所定方向の幅がワードラインより大きい選択トランジスタと、ワードライン及び選択トランジスタの上面を覆う層間絶縁膜と、ワードライン間に位置し上部を層間絶縁膜に覆われた第1空洞部と、選択トランジスタのワードラインとは反対側の側壁部に形成され上部が層間絶縁膜で覆われた第2空洞部を備える。実施形態の半導体記憶装置は、互いに隣接する選択トランジスタ間の基板表面に酸化膜が形成され、その下の所定方向に垂直方向の断面が凸型形状になっている。

(もっと読む)

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ダイシング面からチップ領域への水分の浸入を抑制しつつ、スクライブ領域とチップ領域とを配線により接続する。

【解決手段】半導体装置は、チップ領域16と、スクライブ領域15と、2重に配置された第1シールリング18及び第2シールリング17と、チップ領域16からスクライブ領域15まで延伸する配線60と、を有する。半導体装置は、2重に配置された第1シールリング18及び第2シールリング17のうちの一方のシールリングが配線60を通すためにシールしていない層を、他方のシールリングでシールする構造となっている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】基板上に設けられた層間絶縁膜40に開口部48を形成する工程と、開口部48の側面上および底面上、ならびに層間絶縁膜40上に第1金属材料からなる第1膜10を形成する工程と、第1膜10上であって、開口部48内および層間絶縁膜40上に、第1金属材料よりも電気陰性度が小さい第2金属材料からなる第2膜20を形成する工程と、第2膜20上に、第2金属材料よりも電気陰性度が小さい第3金属材料からなる第3膜30を形成する工程と、熱処理する工程と、開口部48外に位置する第1膜10および第2膜20、ならびに第3膜30を研磨によって除去する工程と、を備える。

(もっと読む)

成膜方法およびCu配線の形成方法

【課題】被処理基板を加熱してトレンチやホールの間口部のオーバーハングを抑制しつつ金属膜を成膜するとともに、成膜後に速やかに被処理基板の温度を低下させることができる成膜方法を提供すること。

【解決手段】載置台を低温に保持して、載置台上に被処理基板を吸着させずに載置する工程と、プラズマ生成ガスのプラズマを生成し、載置台に高周波バイアスを印加した状態で、被処理基板にプラズマ生成ガスのイオンを引きこんで被処理基板を予備加熱する工程と、ターゲットに電圧を印加して金属粒子を放出させ、プラズマ生成ガスのイオンとともにイオン化した金属イオンを被処理基板に引きこんで金属膜を形成する工程と、被処理基板を低温に保持された載置台に吸着させ、載置台と被処理基板との間に伝熱ガスを供給して被処理基板を冷却する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、被加工材にパターンを形成するためのマスクの選択比を向上させ、プロセスコストの低減、歩留りの向上を可能とする。

【解決手段】被加工材上に所定パターンの有機膜を形成し、所定パターンの有機膜中に金属元素を導入し、金属元素が導入された所定パターンの有機膜を用いて、被加工材をエッチング処理する。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した性能と高い生産性とを実現する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、メモリセルアレイ部と、第1平面内においてメモリセルアレイ部と並置されたコンタクト部と、を備えた不揮発性半導体記憶装置が提供される。メモリセルアレイ部は、積層体、半導体層、メモリ膜を含む。積層体は、第1平面に対して垂直な第1軸に沿って積層された複数の電極膜とそれらの間の電極間絶縁膜とを含む。半導体層は電極膜の側面に対向する。メモリ膜は電極膜と半導体層との間に設けられ電荷保持層を含む。コンタクト部は、コンタクト部絶縁層と複数のコンタクト電極とを含む。コンタクト部絶縁層は、コンタクト部絶縁膜と粒子とを含む。コンタクト電極はコンタクト部絶縁層を第1軸に沿って貫通する。コンタクト電極は電極膜に接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】積層ハードマスクを部分的に残存させつつ、配線層用のビアプラグのアスペクト比を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の配線層102を形成し、第1の配線層102上に、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を順に形成し、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を含むピラー状の構造体を形成する。第1の配線層102上に、構造体の上面及び側面を覆うように、第3及び第4の絶縁膜109,106を形成し、第4の絶縁膜106を、第2の絶縁膜105が露出するように、部分的に除去する。第1及び第2の絶縁膜内に、半導体素子材料に接続された第1のビアプラグ107を形成し、第3及び第4の絶縁膜内に、第1の配線層102に接続された第2のビアプラグ108を形成し、第1及び第2のビアプラグ上に第2の配線層111を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】結晶欠陥が可及的に少なく、従来よりも抵抗率の低い高質のグラフェンを備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板の上方に設けられた配線とを具備する。前記助触媒層のうち前記触媒層と接触している部分は、面心立方構造もしくは六方最密構造を有し、かつ、前記面心立方構造の(111)面もしくは前記六方最密構造の(002)面が前記半導体基板の表面と平行になるように配向しているか、または、前記助触媒層のうち前記触媒層と接触している部分は、アモルファス構造もしくは微結晶構造を有する。前記触媒層は、面心立方構造もしくは六方最密構造を有し、かつ、前記面心立方構造の(111)面もしくは前記六方最密構造の(002)面が前記半導体基板の表面と平行になるように配向する。

(もっと読む)

201 - 220 / 3,638

[ Back to top ]