Fターム[5F033QQ48]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | 化学的機械的研磨(CMP) (3,638)

Fターム[5F033QQ48]に分類される特許

41 - 60 / 3,638

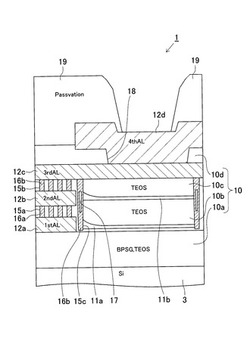

半導体装置及び半導体装置の製造方法

【課題】クラックの発生を抑制できるとともに、SOG膜の剥離を抑えることが可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体素子が形成された半導体基板3上に、SOG膜を含む層間絶縁膜10が形成されており、この層間絶縁膜10を介して、配線層12a〜12dが半導体素子と電気的に接続されている。さらに、一方面側がボンディング接続されるパッド部12d(第4配線層12d)と、層間絶縁膜10に配置されると共に配線層12a〜12cを接続するビアホール15a〜15cと、ビアホール15a〜15c内に埋め込まれる導電層16a、16bとを有している。そして、ビアホール15a〜15cは、パッド部12dよりも下方に設けられており、導電層16a、16bの少なくとも一部は、内部に空洞部17を有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビア層絶縁膜にビア用の孔を形成する工程において、シールリングのうちビア層絶縁膜に位置する部分に、導体を埋め込むための溝を形成しないで済むようにする。

【解決手段】ビア層絶縁膜40及び第2配線層絶縁膜50にはシール溝121が形成されている。また、エッチングストッパー層30には複数の孔31が形成されている。第2シール導体パターン120は、複数の孔31及びシール溝121に埋め込まれている。そして、エッチングストッパー層30は、シール溝121の底面に位置する部分が薄膜部32となっており、シール溝121が形成されていない部分と比較して薄くなっている。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】裏面照射型の固体撮像装置において、受光面と遮光膜との距離を小さくすることにより、光電変換部での受光特性の向上を図る。

【解決手段】光電変換部が配列形成された画素領域を有するセンサ基板と、センサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、画素領域における受光面上に設けられた遮光膜と、遮光膜を覆って設けられた保護絶縁膜と、画素領域の外側の周辺領域において、保護絶縁膜からセンサ基板にかけて埋め込まれ駆動回路に接続された複数の貫通ビアを備えた固体撮像装置。

(もっと読む)

半導体装置の製造方法

【課題】穴部の側壁を基板の表面に対して垂直に形成するとともに、高速にシリコン層をエッチングするプラズマエッチング方法を提供する。

【解決手段】レジスト層をマスクとしてシリコン層をプラズマエッチングする方法であって、前記プラズマエッチング工程が、所定の比率で混合した堆積性ガスおよびエッチング性ガスの混合ガスを処理容器内に導入し、該混合ガス雰囲気で前記被処理基板をプラズマエッチングする第1のエッチングステップと、前記処理容器内に前記堆積性ガスを導入し、前記第1のエッチングステップによりプラズマエッチングされた被処理基板を該堆積性ガスが主体の雰囲気で堆積処理する堆積ステップ、および、前記処理容器内に前記エッチング性ガスを導入し、前記堆積ステップにより堆積処理された被処理基板を該エッチング性ガスが主体の雰囲気でプラズマエッチングする第2のエッチングステップを、複数回繰り返す。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】配線幅が異なる第1及び第2の配線を有する配線パターンの上に形成された絶縁層を、十分に平坦化すること。

【解決手段】基板上に、第1の配線及び第1の配線よりも配線幅が小さい第2の配線を有する配線パターンを形成する配線形成工程S10と、配線パターンの上から、第1の絶縁層及び第2の絶縁層をこの順に形成する絶縁層形成工程S20と、第2の絶縁層の上に、配線パターンの反転パターンを有するレジストパターンを形成するレジスト形成工程S30と、第2の絶縁層の方が第1の絶縁層よりもエッチングされやすい条件で等方性エッチングするエッチング工程S40と、レジストパターンを除去するレジスト除去工程S50と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の形成方法

【課題】配線層間に絶縁物が堆積しない配線の形成方法を提供する。

【解決手段】半導体装置10は、第1絶縁体層14と、第1絶縁体層14上に間隔を空けて配置された複数の配線層18a、18bと、配線層18a、18bの側面上に形成された水素を吸蔵及び放出する水素吸蔵層19b、19c、19d、19eと、複数の配線層18a、18b上に、配線層間の溝20b上を跨ぐように形成された第2絶縁体層23と、を備えた配線を備える。

(もっと読む)

半導体装置の製造方法

【課題】スルーホールの底部における突起の形成を防止して、半導体装置の品質を安定させる手段を提供する。

【解決手段】配線層5と、該配線層上に形成された金属窒化膜8とを覆う層間絶縁膜9とを形成した半導体ウェハに、層間絶縁膜を貫通し金属窒化膜に達するスルーホール10を形成する工程を備えた半導体装置の製造方法において、スルーホールを形成する工程は、層間絶縁膜上に、レジストマスク18を形成する工程と、半導体ウェハを第1の温度とし、異方性エッチングにより層間絶縁膜をエッチングする第1のエッチング工程と、半導体ウェハを、第1の温度より高い第2の温度とし、レジストマスクをそのまま用いて、異方性エッチングにより金属窒化膜の上表面をエッチングする第2のエッチング工程と、レジストマスクを除去する工程と、を備え、第1のエッチング工程と、第2のエッチング工程で用いるエッチングガスとを同一とする。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】 エアギャップ形状を容易に制御することが可能な半導体装置の製造方法を提供する

【解決手段】 本発明では、半導体基板1上に所定の間隔でライン2とスペース3が交互に配置されたライン・アンド・スペース構造体を形成する工程と、前記ラインの上面及び前記スペースの上面を連続して覆う第1の絶縁膜5を形成する工程と、前記スペース上方の前記第1の絶縁膜の一部をエッチングし、開口部6を形成する工程と、前記第1の絶縁膜及び前記開口部を連続して覆う第2の絶縁膜7を形成し、前記スペースと前記開口部による中空部を形成する工程とを有していることを特徴とする半導体装置の製造方法が得られる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極と配線との接続部位の抵抗のバラつきを低減させて、配線信頼性を向上させる。

【解決手段】貫通電極用の穴部を設け、配線層に対してオーバエッチングを施す。穴部に銅を埋め込むことにより、銅からなる貫通電極を形成させて、アルミニウムからなる配線と接続させた後、熱処理により貫通電極と配線とが接続される接触領域Gを合金化させることで、貫通電極と配線との抵抗バラつきを低減させて、配線信頼性を向上させる。本技術は、半導体装置と、その製造に適用することができる。

(もっと読む)

半導体装置の製造方法

【課題】電気めっき装置のハードウェアトラブルを低減しながら、銅めっき膜の均一性を保つ。

【解決手段】自動分析器14は、電極16,17間に印加されている電圧を検出し、その電圧値が設定電圧範囲内であるか否かを判断する。検出した電圧値が、設定電圧範囲の下限値よりも低い場合、自動分析器14は、検出した電圧値に基づいて、基本液の不足量を算出し、バルブ11を制御して不足分の基本液を補充した後、めっき液タンク6内のめっき液が規定量を保つようにバルブ13の動作制御を行い、めっき液を廃液する。また、検出した電圧値が設定電圧範囲の上限値よりも高い場合、検出した電圧値に基づいて基本液の超過量を算出し、バルブ12を制御して基本液の濃度が規定範囲内となるように純水をめっき液タンク6に補充してめっき液を薄めた後、バルブ13を制御して規定量を保つようめっき液を廃液する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーション耐性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】 基板上に絶縁膜を形成する工程と、前記絶縁膜をエッチングして配線溝を形成する工程と、前記配線溝内に銅膜を形成し、銅配線を形成する工程と、前記銅配線及び前記絶縁膜の表面を平坦化する工程と、平坦化された前記銅配線及び絶縁膜上に金属膜を形成する工程と、酸素を含んだ雰囲気中で加熱を行うことにより前記銅配線上の前記金属膜と前記銅配線とを選択的に反応させて合金膜を形成するとともに前記絶縁膜上の前記金属膜を酸化して絶縁性の膜に変化させる工程と、前記合金膜及び前記絶縁性の膜上にブロック膜を形成する工程とを備えた半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の反りを抑制し、且つ、その反りの経時変化を抑制する。

【解決手段】半導体装置は、基板と、基板上に形成された多層配線層と、を有し、多層配線層は、配線と、配線を覆う層間絶縁膜と、をそれぞれ有する複数層の配線層を有する。少なくとも何れか1つの層間絶縁膜(例えば、層間絶縁膜27、30)は、第1絶縁膜41と第2絶縁膜42とを有する。第1絶縁膜41は、基板を第1方向(例えば下に凸)に反らせる応力を基板に与える。第2絶縁膜42は、第1絶縁膜41よりも表層側に形成され、第1絶縁膜41よりも吸湿性が低く、基板を第1方向に対する反対方向(例えば上に凸)に反らせる応力を基板に与える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

41 - 60 / 3,638

[ Back to top ]