Fターム[5F033QQ76]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱酸化 (553)

Fターム[5F033QQ76]の下位に属するFターム

選択酸化 (17)

Fターム[5F033QQ76]に分類される特許

201 - 220 / 536

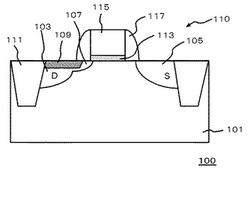

半導体装置およびその製造方法

【課題】非対称トランジスタの接合リークを抑制する。

【解決手段】半導体装置100は、シリコン基板101の上部に設けられたゲート電極115と、ゲート電極115の異なる側方においてシリコン基板101に設けられた第一不純物拡散領域103および第二不純物拡散領域105とを有するMOSFET110を含む。MOSFET110は、第一不純物拡散領域103の上部にエクステンション領域107を有するとともに第二不純物拡散領域105の上部にエクステンション領域107を有さず、第一不純物拡散領域103上に第一シリサイド層109を有するとともに、ゲート電極115側端部の近傍において第二不純物拡散領域105上にシリサイド層を有しない。

(もっと読む)

ポリシラザン溶解用処理液、およびこれを用いた半導体装置の製造方法

【課題】安定したプロセス処理が可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、ポリシラザンを溶剤に溶解してなる塗布液を供給する工程、前記半導体基板を回転させて、前記ポリシラザンを含む塗布膜を形成する工程、前記半導体基板の裏面に、リンス液を供給してバックリンスを施し、裏面を洗浄する工程、前記バックリンス後の前記半導体基板を乾燥して前記リンス液を除去する工程、および、前記半導体基板を熱処理して前記塗布膜から前記溶剤を除去し、シリコン酸化物を含む絶縁膜を得る工程を具備する方法である。前記溶剤および前記リンス液は、少なくとも一部にテルペン類を含み、酸価0.036mgKOH/g未満であることを特徴とする。

(もっと読む)

多孔質構造体の製造方法

【課題】陽極酸化処理に用いる薬液により、半導体基板と保護膜との剥離を抑制する多孔質構造体の製造方法を提供する。

【解決手段】拡散層12が形成された半導体基板10に酸化膜14を形成する工程と、酸化膜14の所定の位置に複数の接続孔を設け、該接続孔に配線22を形成した後、配線22で挟まれた領域に拡散層12の表面が露出するような開口部24を設ける工程と、開口部24の外周縁部に溝26を形成し、溝26を埋め込むように半導体基板10の拡散層12が形成された面の全面に保護層28を堆積する工程と、開口部24の外周縁部に保護層28が残存するように開口部24の保護層28を除去し、拡散層12を露出する工程と、開口部24に残存した保護層28を保護膜32として、露出した拡散層12を陽極酸化処理する工程と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板に発生する応力を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体素子が形成される素子領域を有する基板と、素子領域の隣接部分の基板に形成されるビアホールと、ビアホール内に絶縁層を介して設けられる導通部と、基板と絶縁層との間に設けられる緩衝層とを備え、緩衝層は、基板の熱膨張係数と緩衝層の熱膨張係数との差が、基板の熱膨張係数と絶縁層の熱膨張係数との差より小さい材料から形成される。

(もっと読む)

電子装置及びその製造方法

【課題】絶縁膜とCuを含む配線との間に介在する下地膜であって、特に酸素のバリア性が高い下地膜を含む電子装置を提供する。

【解決手段】電子装置は、凹部の形成された絶縁膜と、凹部内に形成され、Cuを含む配線層と、絶縁膜と前記配線層との間に形成され、Ta及びMnを含む下地膜とを有する。

(もっと読む)

表示装置用パネル、液晶表示装置、配線形成方法

【要 約】

【課題】剥離しない上部配線膜を形成する。

【解決手段】

下部配線膜11とコンタクトする部分や、SiN層12の表面に、インクジェット法によってIn微粒子が分散された第一の印刷液を塗布し、焼成して酸化Inから成る無機接着膜13を形成し、無機接着膜13の表面にAg微粒子が分散された第二の印刷液を塗布し、焼成して上部配線膜14を形成する。無機接着膜13は、下部配線膜11表面のMoN層23及びガラス基板10上のSiN層12と、上部配線膜14と接着性が高いので、上部配線膜14が剥離しない。

(もっと読む)

半導体装置の製造方法

【目的】膜切れの無い均一なシード膜を形成する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S102)と、絶縁膜に開口部を形成する工程(S104)と、開口部内に光触媒膜を形成する工程(S110)と、Cuを含有する溶液に光触媒膜を浸漬させた状態で光触媒膜に紫外線を照射する工程(S112)と、開口部内に電解めっき法によりCuを埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置の製造方法及び半導体装置

【課題】基板の表面における液切れを促進し、液溜まりを少なくできるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】ウエーハWの表面であって、横方向に向かってそれぞれ延びる複数本の第1スクライブラインSL1と、縦方向に向かってそれぞれ延びる複数本の第2スクライブラインSL2とにより囲まれた領域にチップを形成する際に、第1スクライブラインSL1上に対して断面視で凹んだ溝部3を第2スクライブラインSL2上に形成する工程、を含む。ディップ式の装置を用いたウェット処理工程において、ウエーハWを引き上げる際に、ウエーハW表面に付着している液体は溝部3に流れ込み、溝部3を通って下方に流れるので、ウエーハW表面から液体を速やかに取り除くことができる。

(もっと読む)

半導体装置の製造方法

【課題】ダイシング後にパッドの表面に接続される金属物の密着性を改善することができ

る半導体装置の製造方法を提供する。

【解決手段】半導体装置1の製造方法において、半導体基板10の上方の層間絶縁膜36

上に金属パッド40を形成する工程と、酸素含有雰囲気内において熱処理を行い、金属パ

ッド40の表面にアルミニウム又はアルミニウム合金を有する金属酸化膜41を形成する

工程と、半導体基板10を分割してチップを形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極間にエアギャップを制御良く形成する。

【解決手段】本発明の半導体装置の製造方法では、半導体基板2上のゲート絶縁膜3上に浮遊ゲート電極用の多結晶シリコン層4を形成するときに、多結晶シリコン層4の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、この多結晶シリコン層4上に形成したゲート間絶縁膜5上に制御ゲート電極用の多結晶シリコン層9を形成するときに、多結晶シリコン層9の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、複数のゲート電極の側面が露出した状態で熱酸化処理を行なった後、エッチングすることにより、多結晶シリコン層4、9の各側面に凹部11、12を形成し、複数のゲート電極間に絶縁膜7を埋め込み、埋め込まれた絶縁膜7の中にエアギャップ8を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタを追加しても高集積化を図ることができる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、高耐圧領域にMIMキャパシタ及び高耐圧系トランジスタを有し、シリコン基板1に形成され、ゲート電極6及びソース・ドレイン拡散層5を囲むように形成された第1導電型のシールド用拡散層5aと、ゲート電極上に形成された層間絶縁膜9と、層間絶縁膜に形成され、シールド用拡散層上に位置し且つゲート電極を囲むように配置されたホール10aと、ホール内に埋め込まれたWプラグ11aと、Wプラグ及び層間絶縁膜の上に形成されたシールド用配線12aと、シールド用配線上に形成されたキャパシタ絶縁膜13及びキャパシタ上部電極14と、を具備し、MIMキャパシタは、シールド用配線12aをキャパシタ下部電極とすることを特徴とする。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、絶縁膜のホール内に形成される導電性プラグ等の導電性材料のコンタクト抵抗が基板面内でばらつくのを防止すること。

【解決手段】シリコン基板30の上方に第1の層間絶縁膜45を形成する工程と、第1の層間絶縁膜45の上方に強誘電体キャパシタQを形成する工程と、強誘電体キャパシタQの上方に、水素バリア絶縁膜55、57、62と第2の層間絶縁膜58とを有する積層膜を形成する工程と、エッチングにより積層膜にホール58b、58cを形成する工程と、ホール58b、58c内に金属配線(導電性材料)69を埋め込む工程とを有し、ホール58b、58cを形成する工程において、水素バリア絶縁膜55、57、62のエッチングを、第2の層間絶縁膜58のエッチングとは異なるエッチング手法で行う半導体装置の製造方法による。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、簡便な手法で半導体基板の端面と裏面側の周縁部とをクリーニングすること。

【解決手段】シリコン基板50の縁部を保持する工程と、シリコン基板50の裏面Aの周縁部Rにブラシ12を摺接させることにより、シリコン基板50の裏面Aに付着している堆積物を除去する工程とを有し、上記の堆積物を除去する工程において、ブラシ12の一部をシリコン基板50の裏面Aからはみ出させる半導体装置の製造方法による。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、エッチング生成物を直接観察することなくその有無を判断すること。

【解決手段】シリコン基板1の上方に、第1の導電膜19、強誘電体膜20、及び第2の導電膜21を形成する工程と、第2の導電膜21をパターニングして上部電極21aにする工程と、強誘電体膜20をパターニングしてキャパシタ誘電体膜20aにする工程と、レジストパターン30をマスクにして、該レジストパターン30の側面を後退させながら、第1の導電膜19をエッチングし、下部電極19aを形成する工程と、上部電極20aの上面のうち、レジストパターン30の後退を反映して他の領域よりも高位となった段差面21xの幅を測定する工程と、段差面21xの幅C1に基づいて、キャパシタ誘電体膜20aの側面に付着したエッチング生成物の有無を判断する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置およびその製造方法

【課題】デバイスの動作不良や消費電力の増大を抑制できる、金属シリサイド層を有する半導体装置を提供する。

【解決手段】この半導体装置は、シリコンを含み主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された不純物拡散層IDL1,IDL2と、不純物拡散層IDL2上に形成された金属シリサイドMSと、金属シリサイドMS上に順に積層されたシリコン窒化膜SNF、第一の層間絶縁膜IIF1とを備える。半導体装置には、シリコン窒化膜SNF、第一の層間絶縁膜IIF1を貫通して金属シリサイドMSの表面に至るコンタクトホールCHが形成されている。コンタクトホールCHの直下に位置する金属シリサイドMSの厚みは、コンタクトホールCHの周囲に位置する金属シリサイドMSの厚みよりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】MISトランジスタを備える半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面s1上のうち、nMIS領域RnにnMIS用ゲート電極GEnを形成し、pMIS領域RpにpMIS用ゲート電極GEpを形成し、それらの側方下部に、それぞれ、n型ソース・ドレイン領域sdnおよびp型ソース・ドレイン領域sdpを形成する。続いて、シリコン基板1の主面s1と両ゲート電極GEn,GEpとを覆うようにして、引張応力を持つ第1応力膜N1aを形成する。その後、pMIS領域Rpの第1応力膜N1aにイオン注入300を施すことで応力を緩和させる。その後、熱処理を施すことで両ゲート電極GEn,GEpを結晶化してから、第1応力膜N1aを除去する。両ゲート電極GEn,GEpを結晶化する工程では、第1応力膜N1aの引張応力をnMIS用ゲート電極GEnに記憶させる。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜中の水分による配線メタルの腐食を防止することができ、配線の信頼性向上をはる。

【解決手段】埋め込み配線を有する半導体装置であって、一部に配線用溝113が形成された配線間絶縁膜111,112と、配線間絶縁膜111,112の配線用溝113内に埋め込み形成され、且つ配線用溝113の側壁面との間にギャップを有する金属配線層115と、配線層115の側壁面と上面を覆うように形成された耐水性バリア層118とを備えた。

(もっと読む)

コンタクト構造物の形成方法、及びこれを利用した半導体装置の製造方法

【課題】コンタクト構造物の形成方法及びこれを利用した半導体装置の製造方法を提供する。

【解決手段】コンタクト領域103を有する対象体100上に絶縁層106を形成した後、絶縁層106をエッチングしてコンタクト領域103を露出させる開口を形成する。露出されたコンタクト領域103上にシリコン及び酸素を含む物質膜を形成した後、シリコン及び酸素を含む物質膜上に金属膜を形成する。シリコン及び酸素を含有する物質膜と金属膜を反応させて、少なくともコンタクト領域103上に金属酸化物シリサイド膜121を形成した後、金属酸化物シリサイド膜121上の開口を埋める導電膜を形成する。コンタクト領域とコンタクトとの間に金属、シリコン、及び酸素が三成分系を成す金属酸化物シリサイド膜を均一に形成することができるため、改善された熱安定性及び電気的特性を有する。

(もっと読む)

半導体装置

【課題】電荷を蓄積させる量を容易に調整可能であり、信号遅延回路において信号遅延量を所望に調整可能にする。

【解決手段】セレクタ回路300が、第1半導体部100の電位および第2半導体部200の電位を調整し、第1半導体部100と信号配線10との間と、第2半導体部200と信号配線10との間との少なくとも一方において電位差を生じさせる。これにより、第1半導体部100と信号配線10との間と、第2半導体部200と信号配線10との間との少なくとも一方を、静電容量素子として機能させる。

(もっと読む)

201 - 220 / 536

[ Back to top ]