Fターム[5F033QQ76]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱酸化 (553)

Fターム[5F033QQ76]の下位に属するFターム

選択酸化 (17)

Fターム[5F033QQ76]に分類される特許

121 - 140 / 536

半導体装置の製造方法

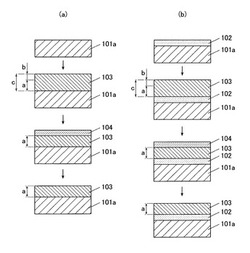

【課題】半導体装置の製造において、シリコン窒化膜の含有水素量を低減してメモリ動作の長期信頼性が確保された製造方法を提供する。

【解決手段】半導体装置の製造方法は、表面にシリコン窒化膜103が形成されたシリコン基板101aを収容した処理室内の圧力を大気圧よりも低くした状態で処理室内に酸素含有ガスと水素含有ガスとを供給して、シリコン窒化膜103の一部を酸化する工程と、シリコン窒化膜103の酸化した部分104を除去する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上にトランジスタ34を形成する工程と、半導体基板上及びトランジスタ上に複数の部分膜36a、38a、40a、42を積層することにより、複数の部分膜を有する第1の絶縁層44を形成する工程と、第1の絶縁層上に、第1の絶縁層とエッチング特性が異なる第2の絶縁層46を形成する工程と、第1の絶縁層をエッチングストッパとして、第2の絶縁層をエッチングすることにより、第2の絶縁層にコンタクトホールを形成する工程と、コンタクトホール内に露出する第1の絶縁層をエッチングする工程とを有し、第1の絶縁層を形成する工程では、複数の部分膜のうちの最上層の部分膜以外の部分膜に対して膜を収縮させるキュア処理を行い、複数の部分膜のうちの最上層の部分膜に対してキュア処理を行わない。

(もっと読む)

半導体装置、電子部品、半導体装置の製造方法

【課題】貫通電極の電気特性を効率よく検査する。

【解決手段】本発明の半導体装置2の製造方法は、シリコン基板20に半導体素子を含んだ電気回路を形成する工程と、シリコン基板20を貫通して設けられ、電気回路と電気的に接続される第1貫通電極22を形成する工程と、シリコン基板20を貫通して設けられ、シリコン基板20の表面20aで第1貫通電極22と短絡する第2貫通電極23を形成する工程と、シリコン基板20の裏面20bにおいて、第1貫通電極22と第2貫通電極23との間の電気特性を検査する工程と、を有する。

(もっと読む)

貫通電極付き半導体デバイスの製造方法

【課題】既にデバイスや配線が形成されている半導体基板に対し、効率良く貫通電極を形成する貫通電極付き半導体デバイスの製造方法を提供する。

【解決手段】半導体基板11の主面に第1のシリコン酸化膜12を形成し、主面Aからもう一方の主面側の第1のシリコン酸化膜12に達する細孔13を形成し、細孔13の孔壁に第2のシリコン酸化膜14を形成し、第1のシリコン酸化膜12上に第1の金属薄膜15および第2の金属薄膜16を形成し、細孔13の端部における第1のシリコン酸化膜12を除去し、細孔13内に導電性物質を充填し貫通電極17を形成する貫通電極付き半導体基板の製造方法。細孔13を、DRIE法で形成する。導電性物質を、溶融金属吸引法または印刷法により細孔13内に充填する。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の一端は、導通部106の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部106は、結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

高周波デバイスおよびその製造方法

【課題】基板に開口を有する高周波デバイスを精度よく位置合わせすることが可能な高周波デバイスおよびその製造方法を提供する。

【解決手段】基板11に貫通電極下部14D、開口16および突起17を設ける。基板11の表面に、絶縁膜12、誘電体層13、絶縁膜12と誘電体層13とを貫通する貫通電極上部14Aおよびスイッチング素子15を形成する。基板11には、開口16および突起17を同時に形成したのち、基板11を貫通すると共に貫通電極上部14Aと接する貫通電極下部14Dを形成する。開口16および突起17を同時に形成することにより、インターポーザ基板などの実装基板に精度よく位置合わせすることが可能な高周波デバイス1を、工程数を増やすことなく得ることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】配線構造におけるクリティカルディメンションの制御性を向上させる。

【解決手段】配線構造の製造方法が提供される。本発明の一態様によれば、絶縁層内に溝またはビアが形成される際、別のビアおよび/または溝の側壁面が金属酸化層で覆われている。金属酸化層は、側壁面の侵食を防止するおよび/または抑制することができる。その結果、方法は、ビアおよび溝のクリティカルディメンションの制御性を向上させることができる。

(もっと読む)

超高品質シリコン含有化合物層の形成方法

【課題】ALDがCVDに比べて優れたコンフォーミティ(coformality)、成膜速度及び均一性を備えた気相堆積方法を提供する。

【解決手段】シリコンナイトライド層を含む、超高品質シリコン含有化合物層を形成するため、複数の順次的なステップ140が、反応チャンバー中で実施される。好ましい実施態様において、シリコン前駆物質としてトリシランを用いて、シリコン層が基板上に堆積100される。シリコン前駆物質は、反応チャンバーから除去される110。その後、シリコンナイトライド層が、シリコン層を窒化すること120によって形成される。窒素反応物質は、反応チャンバーから除去される110。これらのステップ100、110、120及び130を繰り返すことによって、所望の厚さのシリコンナイトライド層が形成される。

(もっと読む)

半導体装置

【課題】高周波デバイスを形成する複数の素子を一つのチップに形成できる技術を提供する。

【解決手段】基板1上にて抵抗素子および容量素子の下部電極を同一の多結晶シリコン膜から形成し、前記多結晶シリコン膜とは異なる同一の多結晶シリコン膜およびWSi膜からパワーMISFETのゲート電極、容量素子の上部電極、nチャネル型MISFETのゲート電極およびpチャネル型MISFETのゲート電極を形成し、領域MIMにおいては基板1上に堆積された酸化シリコン膜30上に形成された配線を下部電極とし酸化シリコン膜34上に形成された配線を上部電極とする容量素子MIMCを形成し、酸化シリコン膜34上に堆積された酸化シリコン膜37上に堆積された同一のアルミニウム合金膜を用い領域INDにて配線39Aからなるスパイラルコイルを形成し、領域PADでは配線39Bからなるボンディングパッドを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】自己整合的にバリア膜を形成する配線構造の信頼性を向上できるようにする。

【解決手段】半導体基板の上に酸素及び炭素を含む層間絶縁膜11を形成し、該層間絶縁膜11に溝部13を形成し、溝部13の底面上及び側壁上に所定の第1の金属元素及び第2の金属元素を含む補助膜14を形成し、熱処理を行い、銅を主成分とする配線本体層19を、溝部13の内部を埋め込むように形成する。熱処理を行うことにより、補助膜14中の第1の金属元素を補助膜14と対向する層間絶縁膜11に拡散させ、溝部13の底面及び側壁における層間絶縁膜11の上において、第1の金属元素と層間絶縁膜11の酸素元素との化合物を主成分とする第1のバリア膜15を形成させた後、補助膜14中の第2の金属元素が補助膜14と対向する層間絶縁膜11に拡散させ、第2の金属元素と層間絶縁膜11の炭素元素との化合物を主成分とする第2のバリア膜17を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

半導体装置

【課題】電極部と貫通電極層の間の抵抗値ばらつきに依存しない信頼性に優れた半導体装置を提供する。

【解決手段】半導体基板表面2aの第1絶縁膜8の中に、外部接続端子を有する電極部18が形成され、基板をビアホール10が貫通し、ビアホール側壁10a及び基板裏面の第2絶縁膜12とビアホール底面の第1絶縁膜とに貫通電極層11が形成され、電極部と貫通電極層との間にシリサイド層9を接続形成し、ビアホール中心軸を含む平面で切断された断面において、シリサイド層の幅A≦ビアホール底部の幅Bである。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧動作のトランジスタ群と高耐圧(高電圧動作)のトランジスタ群とを同一半導体基板に形成して、高耐圧のトランジスタ群のゲート電極の低抵抗化を可能にする。

【解決手段】半導体基板11に、第1トランジスタ群と、第1トランジスタ群の動作電圧よりも低い動作電圧の第2トランジスタ群とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介して形成された第1ゲート電極15と、この第1ゲート電極15上に形成されたシリサイド層40とを有し、第2トランジスタ群は、半導体基板11上の絶縁膜(ライナー膜36、第1層間絶縁膜38)に形成したゲート形成溝42に第2ゲート絶縁膜43を介して形成された第2ゲート電極47、48を有し、第1トランジスタ群の第1ゲート電極15上のシリサイド層40を被覆する保護膜41が形成されていることを特徴とする。

(もっと読む)

MOS型半導体装置

【目的】耐放射線特性の改善と高耐圧化が図れるMOS型半導体装置を提供する。

【解決手段】LOCOS膜18上に窒化膜18を形成し、窒化膜14上にPBSG膜10を形成する。窒化膜14の屈折率を2.0〜2.1とし、膜厚を0.1μm〜0.5μmとすることで半絶縁性薄膜にする。γ線でLOCOS膜18内に発生した電子―正孔対のうち移動度が小さい正孔31を窒化膜14を通してソース電極12に逃がし、LOCOS膜18にできる正の固定電荷33の蓄積量を抑制する。このように3層構造とすることで耐放射線特性の改善と高耐圧化が図れる。

(もっと読む)

半導体装置

【課題】外部から侵入する水分に起因した再配線どうしのショートが防止された半導体装置を提供する。

【解決手段】本発明の半導体装置10は、半導体基板12と、半導体基板12上に形成された第1樹脂層30と、第1樹脂層30の上面に形成されてパッド部44を構成する再配線48と、この再配線48および第1樹脂層30の上面を被覆する第2樹脂層32とを備えている。そして、パッド部44は、第2樹脂層の開口部13から露出する露出領域44Aと、第2樹脂層32により被覆される被覆領域44Bとから成り、この被覆領域44Bの幅(L1)を10μm以上としている。

(もっと読む)

配線構造の製造方法、及び配線構造

【課題】製造コストが低い配線構造の製造方法、及び配線構造を提供する。

【解決手段】本発明に係る配線構造の製造方法は、基板10を準備する基板準備工程と、基板10上に半導体層を形成する半導体層形成工程と、半導体層上にドーパントを含むドーパント含有半導体層を形成するドーパント含有半導体層形成工程と、ドーパント含有半導体層の表面を、水分子を含ませた酸化性ガス雰囲気中で加熱することにより、ドーパント含有半導体層の表面に酸化層を形成する酸化層形成工程と、酸化層上に合金層を形成する合金層形成工程と、合金層上に配線層を形成する配線層形成工程とを備える。

(もっと読む)

基板を含む半導体ウェハの一部分内にビアを形成するための方法および基板を含む半導体ウェハの一部分内に形成されるビア構造体

【課題】 貫通ビアを形成するための方法および装置を提供する。

【解決手段】 たとえば、基板を含む半導体ウェハの一部分内にビアを形成するための方法である。この方法は、基板の第1の部分が基板の第2の部分から分離されるように第1の部分を取り囲むトレンチを形成するステップと、第1の部分内で基板を貫通する穴を形成するステップと、穴の内部に第1の金属を形成するステップとを含む。トレンチは基板を貫通して延びる。第1の金属は基板の表面から基板の裏面に延びる。ビアは穴と第1の金属とを含む。

(もっと読む)

半導体装置の製造方法

【課題】個片化時に切断部分が欠けてしまうことを防止できる半導体装置の製造方法を提供する。

【解決手段】複数の素子領域と複数の素子領域を区画する区画領域とを具える上面(第1面)と、上面(第1面)の反対側の裏面(第2面)とを有する半導体ウエハ101Aを準備する工程と、上面(第1面)の各素子領域上に、上層配線102をそれぞれ形成する工程と、裏面(第2面)側から半導体ウエハ101Aを例えばDeep−RIEなどによりエッチングすることで、上層配線102を露出する貫通孔A2を形成すると共に、上面(第1面)の区画領域に対応する裏面(第2面)の領域に半導体ウエハ101Aを貫通する溝B22を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に素子と貫通電極とが形成された半導体装置の製造方法において、貫通電極からの銅による素子の汚染を防止できる方法を提供する。

【解決手段】半導体基板10と、それに形成された素子ZDと、半導体基板10を貫通するスルーホールTHと、半導体基板10の両面側及びスルーホールTHの内面に形成されて、素子ZDを被覆する絶縁層12とを備えた構造体を用意する工程と、スルーホールTH内に貫通電極20を形成する工程と、貫通電極20を被覆する第1バリア金属パターン層30を形成する工程と、絶縁層12に、素子ZDの接続部に到達するコンタクトホールCHを形成する工程と、コンタクトホールCH内の素子ZDの接続部の自然酸化膜を除去する工程と、第1バリア金属パターン層30に接続されると共に、コンタクトホールCHを通して素子ZDに接続される配線層40,40aを形成する工程とを含む。

(もっと読む)

表示装置用Al合金膜、表示装置および該表示装置の製造方法、ならびにAl合金スパッタリングターゲット

【課題】表示装置(LCD)におけるパネルのTAB部引き出し電極の断線を防止することができ、かつ、バリアメタル層を介在させずにAl合金膜を透明画素電極と直接接続することのできるAl合金膜を提供する。

【解決手段】表示装置に用いられるAl合金膜であって、NiおよびCoよりなる群から選択される少なくとも1種の元素(X元素)を0.1〜2.0原子%含み、長径0.01μm超であってNi量とCo量の合計が10原子%以上である化合物が、100μm2あたり3個超析出していると共に、Al結晶粒内の固溶Ni量と固溶Co量の合計が0.1〜0.5原子%であり、かつ、Al合金膜の硬度が1.5GPa以上3.0GPa以下であるところに特徴を有する表示装置用Al合金膜。

(もっと読む)

121 - 140 / 536

[ Back to top ]