Fターム[5F033QQ76]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱酸化 (553)

Fターム[5F033QQ76]の下位に属するFターム

選択酸化 (17)

Fターム[5F033QQ76]に分類される特許

141 - 160 / 536

表示装置及び表示装置製造方法

【課題】表示装置の薄膜トランジスタ基板において、窒化ケイ素膜上への銅の微細配線を、より簡易に行う。

【解決手段】微細配線がされたTFT基板は、無アルカリガラスからなるガラス基板101と、インジウム錫酸化物からなる透明導電膜102と、アルミニウムを4原子%含有し銅を主成分とする合金からなる第一の導電層103及び109と、99.99%純度の純銅からなる銅配線である第二の導電層104及び110と、窒化ケイ素からなるゲート絶縁膜106と、非晶質ケイ素からなる半導体層107と、n+型非晶質ケイ素からなるコンタクト層108と、透明導電膜102と第一の導電層103との界面の金属酸化物層105と、を備える。

(もっと読む)

撮像装置

【課題】性能が良好に確保される撮像装置を提供する。

【解決手段】光を検出する検出部と、前記検出部と電気的に接続された第1の配線と、が設けられたセンサ基板と、前記検出部と反対側において前記前記センサ基板の主面に接し、第2の配線が設けられた支持基板と、を備え、前記センサ基板と前記支持基板との間に介在する接続部であって、前記センサ基板と前記支持基板とが接する接合面と連通し、前記センサ基板及び前記支持基板の少なくともいずれかの主面が後退することにより前記接合面に向かって拡開した内壁面を有し、前記第1の配線と前記第2の配線とを接続する接続体を内包する接続部が設けられたことを特徴とする撮像装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上とホール内に形成したカーボンナノチューブを絶縁膜に損傷を与えることなく絶縁膜上から除去すること。

【解決手段】配線15a上方に絶縁膜17、18を形成し、絶縁膜17、18をパターニングして配線15aに達するホール17aを形成し、ホール17a内と絶縁膜17、18上面にカーボンナノチューブ22を形成し、カーボンナノチューブ22の層の上に第2絶縁膜23を形成し、第2絶縁膜23をエッチングすることによりカーボンナノチューブ22を露出するとともに、カーボンナノチューブ22の層の凹部に第2絶縁膜23を残し、カーボンナノチューブ22をエッチングしてカーボンナノチューブ22の上端の位置を揃え、さらにカーボンナノチューブ22上の第2絶縁膜23をエッチングし、カーボンナノチューブ22をエッチングして絶縁膜17上面から除去するとともにホール17a内に残す工程を含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜の厚さが異なるトランジスタを有する半導体装置の製造歩留まりを向上させる。

【解決手段】シリコン基板1上に高耐圧絶縁膜IH1を形成した後、高耐圧絶縁膜IH1の表面を削って膜厚を薄くし、高耐圧絶縁膜IH1と隣接するようにして中耐圧絶縁膜IM1を形成する。高耐圧絶縁膜IH1は、熱酸化法によって、シリコン基板1の主面より内側から外側に至るようにして形成し、中耐圧絶縁膜IM1は高耐圧絶縁膜IH1より薄くなるようにして形成する。高耐圧絶縁膜IH1は高耐圧MISトランジスタのゲート絶縁膜として、中耐圧絶縁膜IM1は中耐圧MISトランジスタのゲート絶縁膜として形成する。

(もっと読む)

半導体装置の製造方法、半導体装置、および半導体製造装置

【課題】アルミニウム系配線上にヒロックの無い半導体装置を提供する。

【解決手段】アルミニウム系配線形成後に大気巻き込みステップを有する水素シンター処理を施すことでアルミニウム系配線の表面に11nm以上のアルミナ膜を形成することでヒロックの発生を抑制する。また、半導体製造装置は巻き込む大気の供給口を設ける構成とした。

(もっと読む)

半導体装置及びその製造方法、並びに表示装置

【課題】高融点バリアメタル層を形成すること無く、Si膜又はSiを主成分とする膜と良好なコンタクト特性を実現するAl合金膜を提供する。

【解決手段】半導体デバイス(TFT)は、チャネル部11を形成する様にSi半導体膜7上に配設された被酸化のオーミック低抵抗Si膜8と、オーミック低抵抗Si膜8と直接に接続し、且つ、接続界面近傍に、少なくともNi原子、N原子及びO原子を含むアルミニウム合金膜から成る、ソース電極9及びドレイン電極10とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗な電極部を有し、且つパターニング工程数の削減可能な半導体装置及びその製造方法を提供する。

【解決手段】拡散層が形成された半導体基板の上に第1の金属層を形成する工程と、前記第1の金属層の上に開口部を有する絶縁層を形成する工程と、前記絶縁層の開口部において、前記第1の金属層の上に第2の金属層を形成する工程と、前記絶縁層を除去する工程と、前記第2の金属層の露出面に前記第2の金属層よりもイオン化傾向の小さい金属を含む第3の金属層を被覆する工程と、前記第3の金属層をマスクとして前記第1の金属層を除去することにより、前記第1の金属層と前記第2の金属層と前記第3の金属層とを有する電極配線を形成する工程と、を備えたことを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】シード膜の酸化を抑制して、電気的信頼性の低下を抑制することができる半導体装置の製造方法を提供する。

【解決手段】本発明の一の態様によれば、表面に凹部1aを有する基板100の少なくとも凹部1aの内面1b上に、シード膜5を形成する工程と、シード膜5上に、シード膜5の構成材料より酸化されやすい材料からなる保護膜6を形成する工程と、保護膜6に熱処理を施す工程と、熱処理が施された保護膜6の少なくとも一部を除去し、シード膜5の少なくとも一部を露出させる工程と、少なくとも一部が露出したシード膜5に電流を供給して、シード膜5上に凹部1aに埋め込まれるように電解めっきによりめっき膜7を形成する工程と、凹部1aに埋め込まれた部分以外のめっき膜7を除去する工程とを具備することを特徴とする、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】リソグラフィの露光解像限界未満の寸法を有するパターンを形成するための工程数を削減し、また、歩留まりを向上させる半導体装置の製造方法を提供する。

【解決手段】被加工材上に第1のレジスト材からなる第1のレジストパターンを形成する工程と、前記第1のレジスト材が感光するエネルギー線を前記第1のレジストパターンに照射する工程と、前記エネルギー線を照射後に前記第1のレジストパターンのベーク処理を行う工程と、前記被加工材上に前記第1のレジストパターンを覆うように被覆膜を形成する工程と、前記ベーク処理後に前記被覆膜上に第2のレジスト材からなる第2のレジストパターンを形成する工程と、を含む半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の結晶欠陥発生を抑制することができる半導体装置の製造方法を提供する。

【解決手段】ウエハ上にSTI用のトレンチを形成し、そのトレンチに絶縁膜を埋め込む。次に、ウエハ表面に酸素を導入する。酸素導入は、酸素100%雰囲気下で、1100℃、60秒間、ウエハ表面にRTO(Rapid Thermal Oxidation)を行う。その後、高温アニールを行う。SRAM製造プロセスにおいて、転位が発生するおそれのある高温アニール工程とソース/ドレイン部のイオン注入工程の前に酸素導入を行うため、ウエハの結晶強度を高めることができ、アニール工程やイオン注入工程によって発生する転位を抑えることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】幅の狭い溝状領域への層間絶縁膜の形成にポリシラザンを用いた場合のシリコン酸化膜への改質が良好に行われる半導体装置及びその製造方法を提供する。

【解決手段】上面及び側面をキャップ絶縁膜107及びサイドウォール絶縁膜108で覆われた複数のビット線106間に形成された溝状領域109と、N(窒素)よりもO(酸素)を多く含み溝状領域109の内表面を連続的に覆うSiON膜10と、SiON膜10を介して溝状領域109内に埋め込まれ、ポリシラザンを改質することによって形成されたシリコン酸化膜11とを備える。

(もっと読む)

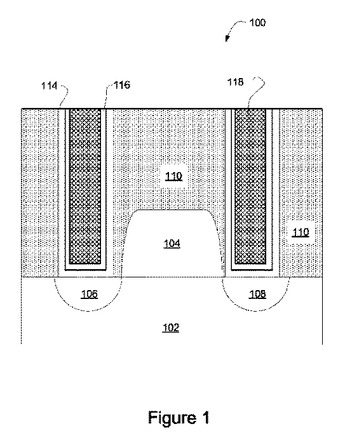

スカロップ状側壁を有するシリコン貫通ビア

【課題】 スカロップ状側壁を有するシリコン貫通ビアを提供する。

【解決手段】 基板、前記基板を覆う、1つ以上の誘電体層、及び前記基板を穿通して延伸し、スカロップ状の表面の側壁を有し、前記側壁に沿ったスカロップは約0.01μmより大きい深さを有するシリコン貫通ビア(TSV)を含む半導体デバイス。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】低抵抗の導電部を備える、信頼性の高い半導体装置を提供する。

【解決手段】ビアホール36a内及び配線溝36b内に、バリア層37を介して、CnMnを含有する第1導電層38、及びCuを主成分とする第2導電層39を形成し、清浄化後、低温酸化を行い、第1,第2導電層38,39表面にCu酸化物層40を形成する。その後、キャップ層の形成を行い、その状態で高温条件の熱処理を行うことで、第1,第2導電層38,39内のMnをCu酸化物層40に拡散させ、キャップ層との界面に、Cu酸化物層40にMnが含有された化合物層を形成する。これにより、第1,第2導電層38,39内のMnを減少させることが可能になり、さらに、キャップ層の密着性を向上させることが可能になる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、半導体装置の製造方法等に関し、ハードマスクを用いることなくエッチング加工が可能となる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ゲート絶縁膜及び素子分離膜2の上にゲート電極3を形成する工程と、第1の層間絶縁膜4を形成する工程と、第1のAl合金膜からなるAl合金配線5を形成する工程と、第2の層間絶縁膜6を形成する工程と、第2のAl合金膜7aを形成する。次いで、第2のAl合金膜7a上にレジストパターン8aを形成する工程と、レジストパターン8aにフロロカーボン系ガスを用いたプラズマ処理を行うことにより、レジストパターンの表面に硬化層8bを形成する工程と、硬化層8bが表面に形成されたレジストパターンをマスクとして異方性エッチングを行うことにより第2のAl合金膜7aを加工する工程と、を具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面照射型のCMOSイメージセンサにおいて、アライメントマークを微細に形成できるようにする。

【解決手段】たとえば、単位セルが形成されるSiエピタキシャル層10に、そのSiエピタキシャル層10を貫通するコンタクト孔21bを形成する。そして、その内壁を酸化させて、膜厚がほぼ均一で薄い絶縁膜21cを形成する。この絶縁膜21cを介して、コンタクト孔21b内に低抵抗ポリシリコンを埋め込んでコンタクト層21aを形成することにより、アライメントマークを兼用する裏面取り出し電極21を形成する構成となっている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】溝の交差部分の中央部に窪みが形成されることを抑制でき、かつ半導体装置の歩留まりが低下することを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、基板100に第1の溝110及び第1の溝110と交差する第2の溝120を形成する工程と、基板100に対して成膜処理を行うことにより、第1の溝110内及び第2の溝120内に膜200を埋め込む工程と、基板100上に位置する膜200を除去する工程とを備える。そして第1の溝110及び第2の溝120を形成する工程において、第1の溝110と第2の溝120の交差部分130に、平面視において交差部分130の角の一つから交差部分130の中央に向けて延伸する凸部140を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】エアギャップ部を有し、かつ、高い機械的強度を有する半導体装置およびその製造方法を提供する。

【解決手段】酸素を含有する層間絶縁膜IL1の複数の溝部の側壁を被覆するバリア金属層ALが形成される。複数の溝部を充填するように配線金属層PCが形成される。層間絶縁膜IL1の酸素を熱拡散させることによってバリア金属層ALの少なくとも一部を酸化することで、酸化物バリア層BL1が形成される。配線金属層のうち複数の溝部の外側の部分を除去することによって、第1および第2の配線間領域IW1,IW2と第1〜第3の配線WR1〜WR3とが形成される。第1の配線間領域IW1を覆い、かつ第2の配線間領域IW2上に開口部OPを有するライナー膜LN1が形成される。開口部OPを介したエッチングが行なわれる。

(もっと読む)

多層マスクの除去方法および半導体装置の製造方法

【課題】シリコン含有膜を有する多層マスクを、シリコン化合物を含む残渣を残存させることなく、容易に確実に除去できる多層マスクの除去方法および半導体素子の製造方法を提供する。

【解決手段】シリコンを含有しない第1膜13と、シリコン含有膜からなる第2膜14と、レジスト層からなる第3膜15とを順に形成してなる多層膜の第3膜15をパターニングし、パターニングされた第3膜15を有する多層膜に不具合がない場合には、第3膜15をマスクとして、ドライエッチングにより第2膜14をパターニングし、多層膜に不具合がある場合には、多層膜に不具合のない場合におけるドライエッチングよりも、第1膜13のエッチング速度と第2膜14のエッチング速度との差が大きいドライエッチングにより第2膜14を除去する多層マスクの除去方法とする。

(もっと読む)

141 - 160 / 536

[ Back to top ]