Fターム[5F033QQ76]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱酸化 (553)

Fターム[5F033QQ76]の下位に属するFターム

選択酸化 (17)

Fターム[5F033QQ76]に分類される特許

161 - 180 / 536

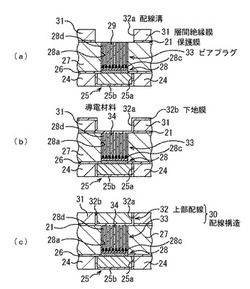

配線構造及びその形成方法、並びに半導体装置

【課題】炭素元素からなる線状構造体を有する接続部の更なる低抵抗化を実現して、更なる接続部の微細化を可能とする。

【解決手段】ビア孔28a内を充填し、配線溝32aの内壁面を覆うように、例えば超臨界CVD法により、ビア孔28a内におけるCNT28d間の空隙及びCNT28dの中空内を導電材料34で埋め込み、ビアプラグ33と、ビアプラグ33上で配線溝32aの内壁面を覆う下地膜32bとを同時形成する。

(もっと読む)

ギャップ充填信頼性を改良し及び容量を減少させるためのデュアル金属インターコネクト

【課題】 ギャップ充填信頼性を改良し及び容量を減少させるためのデュアル金属インターコネクトを提供する。

【解決手段】 本発明のインターコネクト形成方法は;パターン化された金属層の上に誘電層を堆積し、前記誘電層をエッチングしてトレンチ及び下置金属表面を露出するために開口部を形成し、前記前処理された開口部に、及び前記下置金属表面に直接隣接した高融点インターコネクトを形成し、前記トレンチと前記高融点インターコネクト上にバリア層とシード層を堆積し、及び前記シード層上に低抵抗金属を形成することを含む、方法である。  (もっと読む)

(もっと読む)

ボンドパッド下の溝を特徴とするRF装置及び方法

共通する基板(45)上のアクティブデバイス領域46及びボンドパッド(BP)領域60を有する電子素子44、44’、44”において、電子素子(44、44’、44”)をより高い電力あるいは動作周波数、またはその両者にスケール化するように、BP(35)とその相互接続部(41)の寄生インピーダンスを減少するために、BP(35)の下にある誘電体領域を有する。通常(例えば、酸化のみ)の誘電体領域36’による機械的応力は、性能、製造歩留、パッド対装置の近接及び占有面積において不利な点を及ぼす可能がある。埋め込まれた、あるいは近くに配置された、もしくはその両者である誘電性材料78、78’、78”より低い熱膨張係数の、電気的に分離された介在物65、65’、65”を有する複合材料製の誘電体領域62、62’、62”を備えることによって、不利な点を回避できる。シリコン基板(45)において、ポリシリコンあるいは非晶質シリコンは、介在物(65、65’、65”)に適しており、酸化シリコンは誘電体材料(78、78’、78”) に適している。介在物(65、65’、65”)は、誘電体材料(78、78’、78”)によって分離され、その内部に封入される刀身のような形状を有することは望ましい。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

貫通電極配線の製造方法

【課題】複雑な工程を用いることなく、コストの増加や破損の発生などを抑制した状態で、より均一な深さの孔部を形成することで貫通電極配線が形成できるようにする。

【解決手段】酸化シリコン層104をマスクとしたRIEにより、シリコン基板101を選択的にエッチングすることで、シリコン基板101の一方の面(埋め込み酸化層102との界面)に到達する貫通孔106を形成する。貫通孔106の形成のためのエッチング処理(REI)においては、シリコン基板101の深さ方向に、シリコン基板101と埋め込み酸化層102との界面までしかエッチングが進行しない。この結果、シリコン基板101の板厚が均一であれば、貫通孔106の深さも均一に形成されるようになる。

(もっと読む)

酸化膜の作成方法及び半導体装置の製造方法

【課題】低温の酸化処理により酸化膜を形成する。

【解決手段】酸化膜の作成方法は、主鎖にSi−N結合を有する高分子化合物を含む第1の膜16と主鎖にSi−O結合を有する高分子化合物を含む第2の膜15とを積層する工程と、前記第1の膜16及び前記第2の膜15を水蒸気又は水性の雰囲気中で加熱処理し、前記第1の膜16及び前記第2の膜15を酸化膜18に変化させる工程と、を具備する。

(もっと読む)

電子デバイスの製造方法及び設定装置

【課題】電子デバイスの更なる微細化及び高集積化が進んでも、リソグラフィー及びエッチングにより被加工対象の極めて高い寸法精度を達成し、信頼性の高い電子デバイスを実現する。

【解決手段】被加工対象上に形成されたレジスト膜を加工してレジストパターンを形成する工程と、レジストパターンをマスクとして、所定のエッチング条件で被加工対象をエッチングする工程とを実行する際に、形成されたレジストパターンの寸法及び形状(膜厚及びテーパ角度)を測定し、測定されたレジストパターンの寸法及び形状に基づいて前記エッチング条件を調整する。

(もっと読む)

シリコン貫通電極基板の製造方法及びシリコン貫通電極基板

【課題】表面実装の際の処理に対して十分な強度を有する貫通電極を備えた貫通電極基板を簡単に製造することができる貫通電極基板の製造方法及び貫通電極基板を提供すること。

【解決手段】本発明のシリコン貫通電極基板の製造方法は、シリコン基板1にその厚さ方向に貫通した穴部2を形成して、前記厚さ方向に連続した梁1bで支持された貫通電極部1aを残存させる工程と、前記梁1bを熱酸化して前記穴部2を絶縁層3で埋めることにより、シリコンで構成され、前記厚さ方向に貫通した貫通電極4を形成する工程と、を具備することを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】素子特性を劣化させることなく、貫通電極を有する3次元構造の半導体装置を実現することのできる技術を提供する。

【解決手段】半導体基板1Sの主裏面間を貫通する貫通電極8と、その貫通電極8を分離する貫通分離部10とが同一位置に設けられており、半導体基板1Sに、貫通分離部形成用の絶縁トレンチ部を形成した後、活性領域に半導体素子(MIS・FET(Q))を形成し、さらにその後、貫通電極形成用の導通トレンチ部を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】貫通電極を有する3次元構造の半導体装置の製造歩留まりを向上させることのできる技術を提供する。

【解決手段】ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間で、第1バンプ電極50が形成されていない領域に、スペーサ49と第2バンプ電極50aとを積層した支持部を形成することによって、ウエハW3のたわみを防いで、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間隔をウエハ面内で均一に保つ。これにより、ウエハW2の主面上の表面保護膜48とウエハW3の裏面との間の接着剤51の未充填箇所の生成を防ぐ。

(もっと読む)

電気的固体装置、電気光学装置、および電気的固体装置の製造方法

【課題】アルミニウム系の配線材料として用いた場合でも、十分な耐ヒロック性に備えるとともに、ドライエッチングを適用でき、さらに、レジストマスクを剥離する際に用いる剥離液によって、配線がエッチングされることのない電気的固体装置、電気光学装置、および電気的固体装置の製造方法を提供すること。

【解決手段】電気光学装置100において、素子基板10上に走査線3aなどの配線を形成するにあたって、ネオジウムを2atm%未満含有するアルミニウム合金膜を用いるとともに、走査線3aの上面および側面を酸化して表面保護膜31aを形成する。このため、走査線3aは、耐ヒロック性が高いとともに、表面保護膜31a、31eによってアルカリ性の剥離液から保護される。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置に振幅の大きい信号が供給された場合においても正常に動作し、且つ信頼性の高い半導体装置を提供する。

【解決手段】半導体装置は、交流電圧を生成するアンテナ101と、交流電圧を整流し、内部電圧Vinを生成する整流回路102と、第1の保護回路107と、第2の保護回路108と、を有する。第1の保護回路107は、第1のダイオード201と、第2のダイオード202と、を有し、第2の保護回路は、容量素子203と、トランジスタ204と、を有する。第1の保護回路は、アンテナ101で生成される交流電圧の絶対値がある値よりも大きい場合に、その余剰分をカットし、第2の保護回路108は、整流回路102で生成された内部電圧Vinが大きい場合に機能し、共振周波数をずらすことにより、半導体装置に入力される信号を減少させることができる。

(もっと読む)

貫通電極基板の製造方法

【課題】導通部におけるボイドの発生を抑えた貫通電極基板の製造方法を提供する。

【解決手段】基板101に表裏を貫通する貫通孔102を形成し、次に基板101の表面および貫通孔102の内壁に絶縁膜103を形成した後、閉塞部材を貫通孔102の少なくとも一方を塞ぐように配置し、前記閉塞部材を配置した側の基板101上にシード層を形成し、前記閉塞部材を除去し、前記シード層に給電する電解めっき法により、貫通孔102内に導電材料を充填して導通部105を形成する。

(もっと読む)

薄膜トランジスター用配線膜形成用スパッタリングターゲット

【課題】密着性に優れた薄膜トランジスターのゲート電極、ソース電極およびドレイン電極などの配線膜および配線下地膜を形成するためのスパッタリングターゲットを提供する。

【解決手段】Mg:0.1〜5原子%、Ca:0.1〜10原子%を含有し、必要に応じて、MnおよびAlのうちの1種または2種の合計:0.1〜10原子%を含有し、さらに必要に応じてP:0.001〜0.1原子%を含有し、残部がCuおよび不可避不純物からなる組成を有する薄膜トランジスター用配線膜を形成するためのスパッタリングターゲット。

(もっと読む)

銅配線、銅配線の形成方法および半導体装置

【課題】銅配線本体の開放表面に形成されるマンガンを含むバリア層に最適な内部構成を持たせて、そのバリア機能を充分に発揮させることができる半導体素子の製造方法を提供する。

【解決手段】銅配線1は、電気絶縁層3に銅からなる配線本体8を備える。配線本体の外周81は、電気絶縁層に対向している第1の外周8aと電気絶縁層との間に形成された第1のバリア層7aと、配線本体の外周のうち電気絶縁層に対向していない第2の外周8bに接して形成された第2のバリア層7bとを備える。第1および第2のバリア層はそれぞれマンガンを含む酸化物層からなるとともに、各バリア層内の厚さ方向でマンガンの原子濃度が極大となる位置を有する。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電流損失を低減した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の金属材料は、結晶粒径が29μm以上の結晶粒を含む。また、導通部106の金属材料は、面積重み付けした平均結晶粒径が13μm以上である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】隣接したメモリセル間の干渉を抑制できるようにする。

【解決手段】素子分離絶縁膜4の空洞部の形成領域Rが、浮遊ゲート電極FGaと、浮遊ゲート電極FGc、FGdの直下方に位置する活性領域Saとの間に対向した領域内に設けられるため、当該浮遊ゲート電極FGaと素子分離領域Sbを挟んで対向する活性領域Saとの間の結合容量を低減できる。

(もっと読む)

半導体装置

【課題】ワード線の抵抗の低減及びワード線間容量の低減が可能な半導体装置を提供する。

【解決手段】ワード線3A及び3B方向に延在し、隣接する2つのセル列(L4n+1とL4n+2、L4n+3とL4n+4)を1本のワード線3A,3Bで接続することを特徴とする半導体装置50を採用する。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18上に、SiおよびOを含む絶縁材料からなる犠牲層41が積層される。犠牲層41の積層後、熱処理が行われる。第2絶縁層6および犠牲層41にSiおよびOが含まれるので、熱処理が行われると、第2絶縁層6と合金膜18との界面および合金膜18と犠牲層41との界面において、Si、OおよびMnが結合し、それぞれMnSiOからなる第2バリア膜13および反応生成膜42が形成される。合金膜18に含まれるMnが反応生成膜42の形成に使用されることにより、第2バリア膜13の形成後、その第2バリア膜13の形成に寄与せずに合金膜18に残留するMnの量が減少する。そのため、合金膜18上に積層されるCu層20に拡散するMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

半導体装置

【課題】半導体装置の製造歩留まりを向上できる。

【解決手段】本発明の例に関わる半導体装置は、ウェハ1内に設けられる第1及び第2半導体チップエリア21,22と、第1及び第2半導体チップエリア21,22内の各々に設けられ、トランジスタが形成される第1素子領域51,52と、第1及び第2半導体チップ51,52間に設けられるダイシングエリア3Aと、ダイシングエリア3A内に設けられ、アライメントマークが形成されるアライメント領域35と、第1素子領域51,52とアライメント領域35との間に設けられ、ウェハ1表面に対して垂直方向に突出した凸部91,92を有する凸部形成領域71,72とを具備し、凸部91,92の上端は、ウェハ1表面より高い位置にあり、トランジスタのゲート電極12上端よりも低い位置にある。

(もっと読む)

161 - 180 / 536

[ Back to top ]