Fターム[5F033QQ76]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱酸化 (553)

Fターム[5F033QQ76]の下位に属するFターム

選択酸化 (17)

Fターム[5F033QQ76]に分類される特許

81 - 100 / 536

半導体デバイス

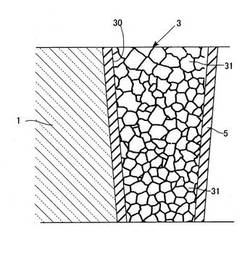

【課題】ストレスによる半導体回路の特性変動・劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体3は、半導体回路に隣接して半導体層1の厚み方向に設けられ、少なくとも一つは、半導体層1と対面する領域に、等軸晶領域を有するか、または、凝固点と融解点との温度差が50℃以上である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

耐透明導電膜ピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記透明導電膜の結晶最大粒径が200nm以下である薄膜トランジスタ基板。

(もっと読む)

プラズマ処理方法及び半導体装置の製造方法

【課題】サイドエッチングによるパターン細りを抑制しつつ、ドライ処理によってパターン側壁に堆積した金属を含む堆積物を効率良く除去することのできるプラズマ処理方法及び半導体装置の製造方法を提供する。

【解決手段】基板に形成された金属層をプラズマエッチングする工程を経て積層構造中に金属層を有するパターンを形成した後、金属層を構成する金属を含みパターンの側壁部に堆積した堆積物を除去するプラズマ処理方法であって、金属層の側壁部に当該金属の酸化物又は塩化物を形成する保護層形成工程と、フッ素原子を含むガスのプラズマを作用させて堆積物を除去する堆積物除去工程と、保護層形成工程及び堆積物除去工程の後、水素を含むプラズマを作用させて金属の酸化物又は塩化物を還元する還元工程とを具備している。

(もっと読む)

導電部形成方法、導電部及び発光装置

【課題】導電部の欠損を防止すること。

【解決手段】Al含有膜2からなるゲートラインLgやコンタクト部42などの導電部を形成する際に、下層保護導電膜/Al含有膜/上層保護導電膜の導体膜を成膜した後、その導体膜に改質処理として酸化処理を施して、上層保護導電膜3で覆われずにピンホールPから露出してしまったAl含有膜2部分に酸化保護領域4を形成することによって、Al含有膜2がレジストの剥離液などに晒されて消失してしまうことを防ぎ、導電部の欠損を防止した。

(もっと読む)

半導体装置の製造方法

【課題】高さのばらつきが低減された埋め込みビット線を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板内にビット線とワード線を有する半導体装置の製造方法において、半導体基板をエッチングして第1の方向に延在する第1の溝を形成することによって、複数の第1の半導体ピラーを形成する工程と、第1の半導体ピラーの側面の一部に拡散層を形成する工程と、隣接する前記第1の半導体ピラー間の前記第1の溝に、拡散層に接続するビット線を形成する工程と、第1の半導体ピラーと前記ビット線を覆う第1の絶縁膜を形成する工程と、第1の半導体ピラーの少なくとも一部が露出するように前記第1の絶縁膜に、第1の方向に直交する第2の方向に延在する第2の溝を形成する工程と、露出した第1の半導体ピラー上にエピタキシャル層を成長させて第2の半導体ピラーを形成する工程と、を有することを特徴とする。

(もっと読む)

成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成することが可能な成膜方法を提供する。

【解決手段】絶縁層1が表面に形成された被処理体Wに対して成膜処理を施す成膜方法において、第1の金属よりなる第1の薄膜60を形成する第1の薄膜形成工程と、前記第1の薄膜を酸化して酸化膜60Aを形成する酸化工程と、前記酸化膜上に第2の金属を含む第2の薄膜62を形成する第2の薄膜形成工程とを有する。これにより、比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】Cdsubの低減を通じて、出力容量Cossの低減に寄与する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板と半導体基板上に絶縁膜を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域内に、第2導電型の半導体層からなるウェルを形成するとともに、ウェル内および第1導電型の活性領域内に、第1導電型の半導体層からなるソース・ドレイン領域を形成した横型MOSFETにおいて、活性領域のうち、ドレイン領域にコンタクトするように形成されるドレインパッド形成領域9p下の少なくとも一部は、SOI基板の絶縁膜に到達するように形成された絶縁性領域11で構成される。

(もっと読む)

半導体装置の製造方法

【課題】信頼性が損なわれるのを防止しつつ、電気的特性の良好な半導体装置を提供する。

【解決手段】半導体基板10上に、化学気相堆積法により、シリコンと酸素と炭素とを含む絶縁膜42を形成する工程と、絶縁膜を形成する工程の後、350℃以下の温度で加熱しながら絶縁膜に対して紫外線キュアを行う工程と、紫外線キュアを行う工程の後、絶縁膜に対してヘリウムプラズマ処理を行う工程とを有している。

(もっと読む)

配線構造物及びその製造方法

【課題】短時間で、配線母体の内部に、種々のトポロジーの貫通配線や連結配線を埋め込むことが可能な配線構造物を提供する。

【解決手段】配線母体11と、配線母体11の内部に設けられた複数の穴部の内部にそれぞれ配置された、配線子連続体(Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1n)からなる複数の貫通配線部とを備える。複数の配線子連続体のそれぞれをなす複数の配線子Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1nのそれぞれは、コア部と、コア部を被覆し、コア部より融点の低い導電体からなるシェル部Qi,shell,Qi+1,shellを有する。複数の配線子は、それぞれのシェル部を互いに溶融することにより金属学的に接合される。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの特性を劣化させることなくポリシリコン抵抗素子を製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板30の抵抗素子形成領域に抵抗素子となるポリシリコン膜35aを形成するとともに、トランジスタ形成領域にポリシリコンゲート35b及び高濃度不純物領域40を形成する。その後、全面に絶縁膜41を形成した後、トランジスタ形成領域をフォトレジスト膜42で覆い、ポリシリコン膜35aに導電性不純物をイオン注入する。次いで、フォトレジスト膜42をアッシングにより除去する。このとき、トランジスタは絶縁膜41に覆われているため、アッシングによるダメージが回避される。また、抵抗素子領域に導入された導電性不純物が大気中のO及びHと反応して酸が発生しても、ポリシリコンゲート及び高濃度不純物領域40が酸により溶解することが回避される。

(もっと読む)

半導体素子、及びその形成方法

【課題】 信頼性が向上する半導体素子、及びその形成方法を提供する。

【解決手段】 半導体素子の形成方法は、半導体基板100の上にゲート電極120及びゲート電極120の両側にスペーサー110を形成する段階、ゲート電極120の上にキャッピングパターン170を形成する段階、ゲート電極120の間にメタルコンタクト195を形成する段階を含み、キャッピングパターン170の幅はゲート電極120の幅より大きく形成される。これにより、形成された半導体素子は、メタルコンタクト195とゲート電極120との間での電気的な短絡を效果的に防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

半導体装置の製造方法

【課題】特性のばらつきを抑制することができる半導体装置の製造方法を提供する。

【解決手段】基板1の上方に絶縁膜4を形成し、絶縁膜4に、絶縁膜4下に位置する導電領域3dを露出する開口部6を形成し、導電領域3d上及び開口部6の側面上に、Tiを含有するグルー膜17を形成する。また、グルー膜17の表面に存在する自然酸化膜を除去して、グルー膜17の表面を露出し、グルー膜17の表面を一定の条件下で酸化し、酸化が行われたグルー膜17上に、Wを含有する導電膜を形成する。なお、酸化を、グルー膜17の表面が露出した状態で開始する。

(もっと読む)

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】吸湿性の高い絶縁膜を使用してもコンタクト又は配線の劣化を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板10上に第1の絶縁膜15を形成する工程(a)と、第1の絶縁膜15にホール24を形成する工程(b)と、ホール24の側壁上に、第1の絶縁膜15よりも水分を通しにくい第2の絶縁膜17を形成する工程(c)と、工程(c)の後、ホール24に導電体30を埋め込むことにより、プラグ19を形成する工程(d)とを備えている。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】バリアメタル層を有する半導体装置を製造するに際し、パーティクルの発生を抑制可能な製造方法、及びこの製造方法を用いる半導体装置の製造装置を提供する。

【解決手段】

2つの金属層の間に金属化合物層が挟まれてなるバリアメタル層を有する半導体装置を製造するに際し、チタン及びタンタルのいずれか一方の金属元素から構成されるターゲットを希ガスの雰囲気でスパッタして、複数の金属層を下地配線上に積層する過程において最下層となる第1金属層に酸化処理を施す。次いで、最下層となる第1金属層の表面に第1金属酸化物層を形成した後に、層間において構成元素が異なるように、一つ以上の金属層を含む下地の表面に対して酸化処理、窒化処理、及び酸窒化処理のいずれかの処理を施す。こうした処理より第2金属化合物層を形成する。上記金属化合物層は、金属酸化物層の他、金属窒化物層や金属酸窒化物層であってもよい。

(もっと読む)

81 - 100 / 536

[ Back to top ]