Fターム[5F033QQ91]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 清浄化 (1,803)

Fターム[5F033QQ91]の下位に属するFターム

コンタクトホール部の清浄化 (522)

除去対象 (877)

Fターム[5F033QQ91]に分類される特許

61 - 80 / 404

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】高さ方向に隣接するメモリセル間でワード線またはビット線を共有する構造の不揮発性記憶装置において、この不揮発性記憶装置に設けられるコンタクトを形成するための工程数を従来に比して削減することができる不揮発性記憶装置を提供する。

【解決手段】ビット線BLのいずれかに接続される複数のビット線コンタクトBCと、ワード線WLに接続される複数のワード線コンタクトWCと、を備え、ビット線コンタクトBCとワード線コンタクトWCは、複数のメモリ層の形成位置に対応するコンタクト層を貫通して形成される複数のコンタクト部81〜83と、高さ方向に隣接するコンタクト部81〜83間を接続する接続配線部41−1,41−2と、を有し、接続配線部41−1,41−2は、ビット線コンタクトBCとワード線コンタクトWCとで同じ高さのコンタクト層に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】保護膜の亀裂や膜剥がれを防止する。

【解決手段】化合物半導体基板1上に少なくとも一層からなる下層配線2を形成し、化合物半導体基板1上に有機材料からなる層間膜3を堆積し、層間膜3上に金からなる上層配線5を形成し、層間膜3中に下層配線2と上層配線5とを接続するヴィア4を形成し、上層配線5の表面および層間膜3の表面の上にシリコン窒化膜からなる密着性向上用膜6を形成し、密着性向上用膜6上にシリコン酸化膜からなる熱膨張抑制膜7を形成し、熱膨張抑制膜7上にシリコン窒化膜からなる保護膜8を形成する。

(もっと読む)

半導体装置の製造方法

【課題】欠陥を内在する炭化珪素半導体を用いても、大面積半導体装置の高歩留りを安定して実現可能な半導体装置の製造方法を提供する。

【解決手段】炭化珪素半導体基板上に炭化珪素半導体層をエピタキシャル成長する工程と、炭化珪素半導体層表面を研磨する工程と、研磨する工程の後に、炭化珪素半導体層に不純物をイオン注入する工程と、不純物を活性化するための熱処理をする工程と、熱処理をする工程の後に、炭化珪素半導体層表面に第1の熱酸化膜を形成する工程と、第1の熱酸化膜を化学的に除去する工程と、炭化珪素半導体層上に電極層を形成する工程と、を有することを特徴とする半導体装置の製造方法。

(もっと読む)

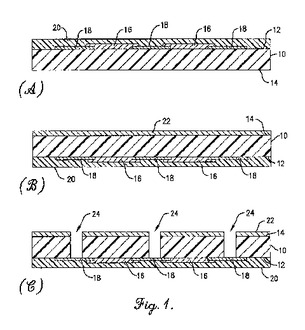

背面処理中に前面側電気回路を保護するための耐傷性コーティング

マイクロエレクトロニクスメカニカルおよび半導体デバイス特徴の前面側を保護する、耐傷性コーティングを、その使用方法とともに提供する。上記コーティングは、非感光性で、除去可能であり、高い処理温度に耐える。また、これらのコーティングは、デバイス設計において、別個のエッチング停止層を不要とする。上記コーティングは、溶媒系に溶解または分散した成分を含有する組成物から形成される。上記成分は、スチレンアクリロニトリル共重合体および芳香族スルホンポリマーからなる群から選択される。  (もっと読む)

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、半導体層と例えばソース電極やドレイン電極を構成するAl系膜とを安定して直接接続させることが可能であるとともに、ウェットプロセスで用いる電解質液中で、半導体層とAl系膜との間でガルバニック腐食が生じにくく、Al系膜の剥離を抑制することのできる配線構造を提供する。

【解決手段】基板1の上に、基板1側から順に、薄膜トランジスタの半導体層4と、半導体層4と直接接続するAl合金膜6と、を備えた配線構造であって、半導体層4は酸化物半導体からなり、Al合金膜6は、Niおよび/またはCoを含む。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】主にアルミニウム系通常配線を有するLSIの製造工程BEOLプロセスでは、配線の信頼性に関して、EM耐性およびSM耐性の向上が特に重要である。アルミニウム系配線に関する不良の中でも、配線メタル膜の膨張や欠けの発生は、EM耐性およびSM耐性を大きく劣化させる要因となる。

【解決手段】本願発明は、層間絶縁膜を成膜するプラズマCVDチャンバのウエハ・ステージ上に於いて、アルミニウム系配線メタル膜のパターニングの後であって層間絶縁膜の成膜前に、ウエハのデバイス面に対して、不活性ガスを主要な成分の一つとして含む雰囲気下、アルミニウム系配線メタル膜および層間絶縁膜の成膜温度よりも高いウエハ温度において、プラズマ・アニール処理を実行することにより、配線メタル層の側壁部の付着物が完全に除去され、膨張不良の原因が取り除かれ、更に、不動態化の進行、ストレス開放等により、欠け不良を抑制するものである。

(もっと読む)

半導体装置

【課題】レジストパターンの解像不良を引き起こす反応阻害物質を確実に除去することが可能なダマシン構造の半導体装置及びその製造方法の提供。

【解決手段】基板上に、少なくとも第1層間絶縁膜6及び低誘電率膜からなる第2層間絶縁膜4を有し、第2層間絶縁膜上に形成した第1レジストパターン1aを用いてビアホール9を形成し、アミン成分を含有する有機剥離液で有機剥離処理を行った後、続いて第2層間絶縁膜上に第2レジストパターン1bを形成する工程を含む半導体装置の製造方法であって、ウェット処理後、第2レジストパターン下層の第2反射防止膜2bを塗布する前に、アニール処理、プラズマ処理、UV処理又は有機溶媒処理の少なくとも一の処理を行い、露光時にレジスト中で発生する酸の触媒作用を阻害するアミン成分を除去して第2レジストパターン1bの解像度の劣化を防止する。

(もっと読む)

半導体装置の製造方法

【課題】ダマシン法を使用して配線を形成する半導体装置の製造技術において、信頼性の高い配線を形成する技術を提供する。

【解決手段】ハードマスク膜HM1上にハードマスク膜HM2が形成され、このハードマスク膜HM2上に有機樹脂膜ORFが形成された状態で、レジストCMPを実施する。これにより、ハードマスク膜HM2上に形成されている有機樹脂膜ORFが除去されるとともに、ハードマスク膜HM2の膜厚が膜減りする。その後、膜減りしたハードマスク膜HM2を除去し、露出したハードマスク膜HM1をマスクにしてトレンチを加工する。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細な電極ピッチで形成された半導体基板が互いに接続された構造を有する半導体装置の信頼性を向上させる手段を提供する。

【解決手段】半導体装置は、第1の多層配線構造111を備えた第1の半導体基板110と、第2の多層配線構造121を備えた第2の半導体基板120とを有し、第1の半導体基板は第1の多層配線構造を構成する電極層の一部からなる第1の接合用電極層112を有し、第2の半導体基板は第2の多層配線構造を構成する電極層の一部からなる第2の接合用電極層122を有し、第1の接合用電極層は第1のディッシング部113を備え、第2の接合用電極層は第2のディッシング部123を備え、第1のディッシング部と第2のディッシング部との間に接合部材130が配置され、接合部材を介して第1の接合用電極層と第2の接合用電極層が接合される。

(もっと読む)

半導体装置の製造方法

【課題】配線表面の酸化膜を除去する際の低誘電率絶縁膜の変質を抑える半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上のSiOC膜11表面に配線12を形成する工程と、配線12が表面に形成されたSiOC膜11を希ガス、又は希ガスとN2ガスの混合ガスを含むプラズマに曝してSiOC膜11表面に緻密層14を形成する工程と、緻密層14が形成された後に、配線12の表面に形成された酸化膜13を除去する工程と、酸化膜13が除去された配線12、及び緻密層14上に絶縁膜としての拡散防止膜15を形成する工程と、を含み、酸化膜13を除去する工程から拡散防止膜15を形成する工程までが、大気に暴露されることなく行われる。

(もっと読む)

半導体デバイスの製造方法

【課題】薄型化されたウェハにめっき処理をする際にウェハ裏面への金属析出やウェハの反り及び損傷を抑制すると共に、ウェハのめっき処理効率が良好な半導体デバイスの製造方法を提供する。

【解決手段】ウェハを薄型化する工程1、薄型化された前記ウェハの裏面をダイシングテープでリングフレーム内にマウントする工程2、及び、前記リングフレーム内にマウントされた前記ウェハの表面にめっき処理を行う工程3を備えた半導体デバイスの製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の表面に対するダメージを防ぎ、配線膜厚を均一に制御することにより、配線間ショート及び信頼性劣化を防止できるようにする。

【解決手段】半導体基板101の上に絶縁膜102を形成し、絶縁膜102の内部にイオン注入法によりイオン注入層103を形成し、絶縁膜102に少なくともイオン注入層103に達する深さの配線溝104を形成し、配線溝104に導電膜107Aを形成し、絶縁膜102及び導電膜107Aにおけるイオン注入層103よりも上に形成されている領域を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部からの水分がパッド上の開口部に浸入した場合でも、開口部の側面に露出している窒化チタン膜が酸化チタン膜に変化することを抑制することができ、半導体装置の信頼性を向上できる技術を提供する。また、パッドの表面保護膜にクラックが発生することを抑制し、半導体装置の信頼性を向上できる技術を提供する。

【解決手段】開口部OP2の径を開口部OP1の径よりも小さくし、かつ、開口部OP2を開口部OP1に内包されるように形成する。これにより、開口部OP1の側面に露出する反射防止膜ARの側面を、開口部OP2を形成している表面保護膜PAS2で覆うことができる。この結果、反射防止膜ARの側面を露出することなく、パッドPDを形成することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】第2絶縁層にビアとなる接続孔を形成するときにビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。エッチングストッパー膜200は、第1絶縁層120上、エアギャップ128上、及び配線162上に形成されている。第2絶縁層220はエッチングストッパー膜200上に形成されている。ビア262は第2絶縁層220に埋め込まれており、配線162に接続している。そしてエッチングストッパー膜200は、エアギャップ128上に位置する部分202が、配線162上に位置する部分より厚い。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

61 - 80 / 404

[ Back to top ]