Fターム[5F033QQ91]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 清浄化 (1,803)

Fターム[5F033QQ91]の下位に属するFターム

コンタクトホール部の清浄化 (522)

除去対象 (877)

Fターム[5F033QQ91]に分類される特許

21 - 40 / 404

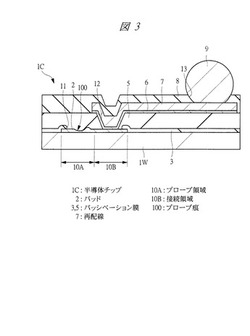

半導体装置

【課題】半導体装置の小型化、特に、狭ピッチ化に対する技術を提供する。

【解決手段】半導体チップ1C上に設けられたパッド2と、プローブ領域10Aおよび接続領域10Bのパッド2上に開口部11を有し、半導体チップ1C上に設けられたパッシベーション膜3と、接続領域10Bのパッド2上に開口部12を有し、パッド2上およびパッシベーション膜3上に設けられたパッシベーション膜5と、パッド2と電気的に接続され、接続領域10B上およびパッシベーション膜5上に設けられた再配線7とを備える。接続領域10Bより半導体チップ1Cの外周部側に設けられたプローブ領域10Aのパッド2にプローブ痕100が存在し、接続領域10Bから半導体チップ1Cの中央部側に延びて再配線7が存在している。

(もっと読む)

半導体装置の製造方法

【課題】ドライエッチングによりアルミニウム材料を金属配線とする加工では、加工中に生成されるホトレジストの反応性生成物が固着することから、取り扱いに手間やコストが掛かる高価な専用の剥離液を用いる必要があった。また、この剥離液は、金属配線にダメージを与えるため、金属配線の品質を低下させていた。

【解決手段】塩素ガス又は塩素を含む反応ガスを用いるドライエッチング工程である金属配線形成工程と、ホトレジストを剥離するホトレジスト剥離工程とを有し、このホトレジスト剥離工程は、酸素と水素を含むフッ化炭素との混合ガスを用いフルアッシングする金属配線露出工程と、純水により洗浄する洗浄工程と、酸素を用いるプラズマでアッシングと、の3つの工程からなる。これにより、専用の剥離液による処理が不要になるため、低コストで品質の高い金属配線を形成できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の強度低下を抑制する。

【解決手段】(a)表面3a、表面3aに形成された複数のチップ領域10c、チップ領域10c間に形成されたダイシング領域、および表面3aとは反対側の裏面を有するウエハ(半導体ウエハ)10の表面3aを支持部材15に固定する。(b)ウエハ10が支持部材15に固定された状態で、ウエハ10の裏面を研削し、裏面3bを露出させる。(c)ウエハ10が支持部材15に固定された状態で、ウエハ10をチップ領域10c毎に分割する。(d)チップ領域10cの側面3cをエッチングし、(c)工程により側面3cに形成された破砕層を除去し、複数の半導体チップをする工程を有する。また、(e)(d)工程の後、分割された複数のチップ領域10cを支持部材15から剥離させて、複数の半導体チップを取得する。

(もっと読む)

半導体基板への有機膜パターンの直接描画プロセスにおける前処理方法

【課題】直接描画法によりレジストの膜パターンやパッシベーション用などの有機膜パターンを形成する際に発生し易い描画性や密着性の問題を防ぐことのできる半導体基板への有機膜パターンの直接描画プロセスにおける前処理方法を提供すること。

【解決手段】相互に異なる材料で構成された複数のパターン膜2、3、4で覆われた半導体基板1表面上に、前記複数のパターン膜2、3、4上に跨って積層される有機膜パターン5を直接描画法により形成する際に、前処理として前記半導体基板1表面を、プラズマ生成ガスとして酸素と窒素を用いてアッシングし、続いて水素と窒素をプラズマ生成ガスとして用いてクリーニング処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】制御性よく空洞部を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】ダミーゲート電極22上にオフセットスペーサ材料層を形成し、オフセットスペーサ材料層に異方性エッチングを行い、ダミーゲート電極22の側壁下部にオフセットスペーサ24を形成する。そして、サイドウォール15の形成後、ダミーゲート電極22とオフセットスペーサ24とを除去し、高誘電率材料からなるゲート絶縁膜13とメタルゲート電極14とを異方性の高い堆積方法を用いて形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】SOD法によって形成するシリコン酸化膜に、ボイドが発生することを抑制する。

【解決手段】基板、基板表面に形成された溝状領域G、及び溝状領域Gに埋設されたシリコン酸化膜8を有する半導体装置の製造方法であって、溝状領域Gを含む基板の表面を覆うライナー膜6を形成するライナー膜形成工程と、ライナー膜6の表面を水洗する水洗工程と、水洗後の残留水分を除去する水分除去工程と、基板表面にポリシラザン溶液をスピンコートにより塗布する塗布工程と、アニールによりポリシラザン溶液をシリコン酸化膜8に改質する改質工程とを備える。

(もっと読む)

半導体装置

【課題】半導体チップ内の銅配線が一部消失することを防ぐ。

【解決手段】上層プラグ一本当たりの下層の配線の面積が10000μm2以上になるような大面積の多層配線を有する半導体装置において、前記多層配線が半導体基板1Sの主面においてn型拡散層NSを介してpウエルPWに接続される構造を形成せず、前記多層配線をp型拡散層PSを介してpウエルPWに接続する構造、前記多層配線をp型拡散層PSを介してn型拡散層NSに接続する構造、前記多層配線をn型拡散層NSを介してnウエルに接続する構造、または半導体基板1S上に形成されたMISFETのゲート電極に接続する構造を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の電気的な接続信頼性を向上させる。

【解決手段】(a)半導体基板の主面上に、主導体膜(下地膜)7Aおよび主導体膜7A上のストッパ絶縁膜(被測定膜)6sを積層する工程、(b)ストッパ絶縁膜6sに開口部8を形成する工程、を含んでいる。また、(c)開口部8に電子ビーム(励起線)EBを照射して、特性X線を放出させる工程、および(d)特性X線を検出し、特性X線の検出結果に基いて開口部8の底部8Bにおけるストッパ絶縁膜6sの有無または膜厚を判定する工程、を含んでいる。また、(d)工程では、特性X線に含まれる複数の元素成分の比率により、ストッパ絶縁膜6sの有無または膜厚を判定する。

(もっと読む)

電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3層構造とすることで課題を解決する。本発明は、アルミニウム原子のチャネル形成領域への拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、その第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、配線又は電極を3層構造としてITOと接合させる。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線は、配線溝を有する絶縁膜13と、前記配線溝内の両側面の前記絶縁膜上に形成された第1触媒膜15と、前記配線溝内の両側面の前記第1触媒膜上に形成され、両側面に対して垂直方向に積層された複数のグラフェンシートで構成された第1グラフェン層16と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間の容量低減を実現するとともに、ミスアライメント・ビアを対策する。

【解決手段】配線上及び配線間のスペース領域に絶縁膜74を形成し、隣接配線間隔が狭い配線の上面を露出するスルーホールの周辺領域の絶縁膜74をリザーバーとして残して、周辺領域以外の絶縁膜74を除去し、絶縁膜74が除去された配線間のスペース領域に空隙を残しつつ、配線上に絶縁膜77を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置の製造システム

【課題】ダマシン配線構造を有する半導体装置において、CMP法によるCu配線への処理により発生するCu配線の腐食(コロージョン)の発生を防止し、配線抵抗の上昇を抑制し、信頼性の担保された半導体装置の製造方法および半導体装置の製造システムを提供する。

【解決手段】ダマシン配線構造を有する半導体装置の製造方法であって、基板上の層間絶縁膜に形成される配線パターン溝にバリアメタル膜およびCu膜が形成された状態で、ケミカルメカニカルポリッシングによって配線パターン溝以外に堆積したCuを除去する工程と、配線パターン溝以外に堆積したバリアメタルをケミカルメカニカルポリッシングによって除去する工程と、前記バリアメタルを除去する工程後、除電する工程と、基板上に残るスラリーおよび残渣物を洗浄する工程と、を有する半導体装置の製造方法が提供される。

(もっと読む)

導電材埋め込み方法及び半導体装置の製造方法

【課題】 従来の方法と比較して、短時間で凹部の全体に導電材を埋め込むことができる技術を提供する。

【解決手段】 本願に係る導電材の埋め込み方法は、半導体装置の製造過程において表面に形成される凹部22に導電材を埋め込む方法に関する。この方法は、凹部22の少なくとも底面に露出する下地層10の表面に不純物24aを定着させる不純物定着工程と、不純物24aが定着した下地層10を利用して導電材をVLS成長させて、凹部の全体に導電材を埋め込むVLS成長工程とを有する。この方法では、VLS成長によって凹部22に導電材を埋め込むため、短時間で導電材を埋め込むことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

配線構造及び配線構造の形成方法

【課題】配線の洗浄液への溶解を低減する配線構造の形成方法を提供する。

【解決手段】絶縁層13に犠牲配線溝21及び主配線溝31を形成し、犠牲配線溝21及び主配線溝31内にバリア層16を形成し、バリア層16が形成された犠牲配線溝21及び主配線溝31内に導電層17を埋め込んだ後に、絶縁層13上の導電層17の部分を研磨する工程と、犠牲配線溝21及び主配線溝31内の露出したバリア層16及び導電層17の表面を洗浄する工程と、を備え、研磨する工程の後における絶縁層13の平面視において、犠牲配線溝21内のバリア層16の部分の面積と導電層17の部分の面積との比S1が、主配線溝31内のバリア層16の部分の面積と導電層17の部分の面積との比S2よりも大きくなる。

(もっと読む)

銅配線半導体用洗浄剤

【課題】 研磨剤由来の砥粒の除去性、絶縁膜上の金属残渣と有機残渣の除去性に優れ、かつ銅配線の耐腐食性に優れる銅配線半導体用洗浄剤を提供することを目的とする。

【解決手段】 銅または銅合金配線を形成する半導体製造工程中の化学的機械的研磨の後に続く工程において使用される洗浄剤であって、アミン(A)、グアニジンの塩またはグアニジン誘導体の塩(B)、および水を必須成分とし、使用時のpHが8.0〜13.0であることを特徴とする銅配線半導体用洗浄剤を用いる。

(もっと読む)

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

半導体装置及びその製造方法

【課題】実装基板に信頼性よく実装できる多層構造の再配線を備えた半導体装置を提供する。

【解決手段】バンプ電極18を備えた半導体基板10aと、半導体基板10aの上に形成され、バンプ電極18の横方向に配置された第1絶縁層20と、第1絶縁層20の上に形成され、バンプ電極18に接続された第1配線層30と、第1配線層30の上に形成された第2絶縁層22と、第2絶縁層22に形成され、第1配線層30に到達するビアホールVHと、第2絶縁層22の上に形成され、ビアホールVHに形成されたビア導体40を介して第1配線層30に接続される第2配線層32と、第2配線層32に接続された外部接続端子34とを含み、第2絶縁層22の弾性率は第1絶縁層20の弾性率より低く設定されている。

(もっと読む)

21 - 40 / 404

[ Back to top ]