Fターム[5F033QQ91]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 清浄化 (1,803)

Fターム[5F033QQ91]の下位に属するFターム

コンタクトホール部の清浄化 (522)

除去対象 (877)

Fターム[5F033QQ91]に分類される特許

161 - 180 / 404

半導体装置およびその製造方法

【課題】加速度センサや角速度センサのようにバルクマイクロマシニング技術により形成したMEMSセンサとLSI回路からなる半導体装置の小型化や薄型化と、高感度化を両立しつつ、MEMSセンサとLSI回路からなる半導体装置の実装構造を簡易化する。

【解決手段】SOI基板のシリコン層102上にMISFETや配線を有する集積回路を形成し、SOI基板の基板層100を加工して、構造体125を含むMEMSセンサを形成している。すなわち、SOI基板の両面を使用して、1つのSOI基板に集積回路とMEMSセンサを搭載する。そして、集積回路とMEMSセンサとは、SOI基板の内部に設けられている貫通電極121によって電気的に接続されている。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造ライン

【課題】 欠陥を修復する際に、正常に形成されるべき配線へダメージを与えてしまう。

【解決手段】 絶縁膜と、複数の配線を有する配線層と、が交互に積層された多層配線構造を有する半導体装置の製造方法において、配線層のうちの1層を第1の絶縁膜上に形成する工程と、第1の絶縁膜上に形成された配線層の欠陥を検出する工程と、検出工程の結果に基づいて、検出された欠陥に集束イオンビームを照射するか否かを選択する工程とを有する。そして、選択工程において集束イオンビームを照射すると選択された場合には、欠陥に集束イオンビームを照射した後、第1の絶縁膜上に形成された配線層上に第2の絶縁膜を形成する工程を有する。また、選択工程において集束イオンビームを照射しないと選択された場合には、欠陥に集束イオンビームを照射せずに第1の絶縁膜上に形成された配線層上に第2の絶縁膜を形成する工程を有する。

(もっと読む)

半導体素子の製造方法

【課題】 本発明は、トンネル酸化膜の形成時に酸化膜に窒素を蓄積させた後、後続で酸素を注入するための工程を行ってSi−N結合をSi−O−N結合に変更することにより、窒素プロファイル(N profile)の変化による特性劣化の防止、電気的ストレスの緩和及び酸素密度の増加などを通じてサイクリング(cycling)及び電荷保存(retention)特性などの素子特性を向上させることができる半導体素子の製造方法を提供するものである。

【解決手段】 半導体基板上に第1の絶縁膜を形成する段階と、前記半導体基板と前記第1の絶縁膜の界面に窒素を蓄積させて第2の絶縁膜を形成する段階と、前記第2の絶縁膜に酸素を注入して第3の絶縁膜に変更させる段階とを含む構成としたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】表面がTiN膜であるバリアメタルが露出した部分の耐湿性を向上すると共に、パッシベーション膜を一層としても、クラックに起因する不良を無くし、また、アルミニウム合金中のSiノジュールの成長に起因する不良増加を抑えることのできる積層金属電極配線を有する半導体装置およびその製造方法を提供すること。

【解決手段】半導体基板上に所要の配線パターンで形成される金属電極配線膜として、下地のバリアメタル膜とその上に積層されるアルミニウムまたはアルミニウム合金膜2を有し、さらに、前記アルミニウムまたはアルミニウム合金膜2上に被覆される有機系パッシベーション膜7を備える半導体装置において、前記バリアメタル膜が、チタン膜3、10で挟まれた窒化チタン膜4からなる三層の積層膜を有する半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】ドライエッチングによるアルミニウム配線形成後、反応生成物を除去することにより、エレクトロマイグレーション、ストレスマイグレーションの少ない、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】基板11上に、絶縁膜12を介してアルミニウム膜17を形成する。アルミニウム膜をマスク材18を用いてドライエッチングし、アルミニウム配線15を形成する。マスク材を除去した後、アルミニウム配線の少なくとも側壁に形成された反応生成物19にArをイオン注入し、反応生成物に欠陥を発生させる。ウェットエッチングによりアルミニウム配線の表層をエッチングし、反応生成物を浮き上がらせて剥離する。

(もっと読む)

BCN系の絶縁膜及びその製造方法並びに半導体装置およびその製造方法

【課題】安定した低誘電率と高い硬度(ヤング率)を有するBCN膜が形成できる半導体装置の製造方法が提供する。

【解決手段】従来のBCl3ガスに代わる、腐食性のない有機アミノボロン系ガスを用いてBCN膜を成膜する。その例として、トリスジメチルアミノボロンを用いて、プラズマCVDにより成膜を行うことで、 比誘電率が2.5以下で弾性率(ヤング率)が8GPa以上であるBCN系の低い誘電率を持つ絶縁体材料膜を得る。

(もっと読む)

半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法

本明細書には概して半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法が記載されている。  (もっと読む)

(もっと読む)

成膜装置の排気系構造、成膜装置、および排ガスの処理方法

【課題】トラップ機構の回収物の処理を安全かつ迅速に行うことができる成膜装置の排気系構造を提供すること。

【解決手段】成膜装置の排気系構造は、処理容器11内の排ガスを排出する排気管51と、排気管51の処理容器11の近傍に設けられた自動圧力制御器52と、排気管51の自動圧力制御器52の下流側に設けられた真空ポンプ54と、排気管51の自動圧力制御器52の下流側位置に酸化剤を供給する酸化剤供給部57と、排気管51の酸化剤供給位置の下流側に設けられ、排ガス中の有機金属原料ガス成分および副生成物が前記酸化剤と反応して生成された生成物を回収するトラップ機構53と、排気管51のトラップ機構53の下流側に設けられた除害装置55とを具備する。

(もっと読む)

半導体デバイス用基板の洗浄剤及びそれを用いた洗浄方法

【課題】銅配線を備えた半導体デバイス製造工程における平坦化研磨工程後の洗浄工程に用いられる洗浄剤であって、銅配線の腐蝕や酸化、それに起因する平坦化された基板上配線の表面荒れの発生が抑制され、且つ、半導体デバイス表面の不純物を有効に除去し得る洗浄剤及びそれを用いた洗浄方法を提供する。

【解決手段】表面に銅配線が施された半導体デバイスの製造工程における化学的機械的研磨工程の後に用いられる洗浄剤であって、(A)ポリカルボン酸と、(B)アルデヒド構造を有する化合物と、を含有し、pHが0.5〜5であることを特徴とする洗浄剤である。

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法であって、基板が少なくとも銅含有表面層を含む方法を提供する。

【解決手段】この方法は、第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

半導体装置及びその製造方法

【課題】低コストでメタルキャップ膜が形成された半導体装置及びその製造方法を提供する。

【解決手段】絶縁膜1bに配線溝及び配線孔を形成し、バリアメタル2bを成膜した後、銅層3bを配線溝及び配線孔に埋め込むように形成する。次に、CMP法により表面を平坦化して銅配線層を形成する。この際、CMP用のスラリーに異種金属を有する水溶性金属化合物を添加してCMPを行う。次に、不活性ガス又は還元性ガス雰囲気中で熱処理を行うことにより、銅配線層の表面に、異種金属が添加された銅層9bを形成する。その後、異種金属が添加された銅層9bを覆うようにバリア絶縁膜5bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】層間絶縁膜のCMP時にクラックが発生することを抑制するとともに、クラックが発生しても、クラックによる影響を排除できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上全面を覆うようにオゾンTEOS膜7を形成した後、オゾンTEOS膜7上にプラズマTEOS膜8を形成する。その後、プラズマTEOS膜8の素子形成領域FRと素子非形成領域NFRとの間での高低差を低減するようにCMPを施す。次に、プラズマTEOS膜8を所定の厚さ全面的にエッチングして平坦化する。

(もっと読む)

低誘電率の誘電性材料の表面調整

誘電性領域および導電性領域を含む、パターン化半導体基板表面を提供することと、両親媒性表面調整剤を誘電性領域に塗布し、誘電性領域を調整することと、を含む、パターン化半導体基板を調整する方法が提示される。いくつかの実施形態では、誘電性領域を調整することは、誘電性領域のぬれ角を調整することを含む。いくつかの実施形態では、ぬれ角を調整することは、誘電性領域の表面を親水性にすることを含む。いくつかの実施形態では、方法は、水溶液をパターン化半導体基板表面に塗布することをさらに含む。いくつかの実施形態では、導電性領域は、水溶液によって、選択的に増強される。いくつかの実施形態では、方法は、低誘電率材料から形成される誘電性領域を提供することをさらに含む。いくつかの実施形態では、両親媒性表面調整剤を塗布することは、低誘電率領域の後続プロセスとの相互作用を調整する。  (もっと読む)

(もっと読む)

シード印刷及びめっきによるコンタクト金属及び相互接続金属の印刷

シリサイド形成金属を含むインクを用いて、コンタクト形成方法、そのコンタクト及び局所相互接続を含むダイオード及び/又はトランジスタ等の電気デバイスとその形成方法に関する。コンタクト形成方法は、露出したシリコン表面上にシリサイド形成金属インクを堆積させるステップと、インクを乾燥させ、シリサイド形成金属前駆体を形成するステップと、シリサイド形成金属前駆体及びシリコン表面を加熱して、金属スイサイドコンタクトを形成するステップとを含む。任意選択的に、露出したシリコン表面に隣接する誘電体層上に、金属前駆体インクを選択的に堆積させて、金属含有相互接続を形成できる。更に、1つ又は複数のバルク導電性金属を、残りの金属前駆体インク及び/又は誘電体層上に堆積させてもよい。かかる印刷したコンタクト及び/又は局所相互接続を用いて、ダイオード及びトランジスタ等を作製できる。 (もっと読む)

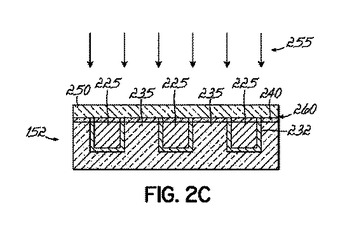

金属絶縁体金属キャパシタの製造方法

【課題】半導体素子において、特に、金属絶縁体金属(MIM:metal−insulator−metal)キャパシタを製造する方法を提供する。

【解決手段】MIMキャパシタを持つ金属膜において、エッチング時に発生するブリッジによるエラーを熱処理により解決し、かつ、MIM構造の電極形成のためのエッチング時に発生する異常現象により後続の下部電極(Bottom Electrode)エッチング工程に誘発されるエラーを防止する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板上に形成された絶縁膜の加工部の表面の平坦化を行なう半導体装置の製造方法を提供する。

【解決手段】半導体基板上に形成された絶縁膜24に所定の加工を施し、前記絶縁膜24の加工部の表面28aに、少なくともSi含有化合物を含む原料を反応させた1次反応物を供給し、その1次反応物について脱水縮合を行なうことにより、加工部の表面28aにシリコン酸化膜30を形成する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の製造方法に関し、界面活性剤を含んだ洗浄液による洗浄後の低誘電率膜のk値の変動を回復する。

【解決手段】 基板上にk値が3.0以下の低誘電率膜1を成膜したのち、低誘電率膜1に凹部を形成し、次いで、凹部及び低誘電率膜1上に導電体膜を堆積したのち、低誘電率膜1が露出するまで導電体膜を研磨し、次いで、低誘電率膜1の表面を界面活性剤3を含む洗浄剤で洗浄したのち、低誘電率膜1の表面に残存する界面活性剤3を、界面活性剤3が表面に残存した状態における低誘電率膜1の比誘電率の増大分を60%以下に低減できる界面活性剤除去方法で除去する。

(もっと読む)

CMP後のウェーハを洗浄するための熱的方法

【解決手段】化学機械研磨後に半導体ウェーハを洗浄するための方法を提供する。方法の一例では、ウェーハに酸化環境における熱処理を施し、その後、還元環境における熱処理を施す。酸化環境における熱処理では、残留物を除去すると共に、露出した銅を酸化して酸化銅層を形成する。還元環境における熱処理では、その後、酸化銅を元素銅へ還元する。これにより、露出した銅は清浄となり、無電解メッキ等、更なる処理のための状態となる。 (もっと読む)

半導体装置及び半導体装置内に空洞を形成する方法(核化防止層を使用する選択的なピンチ・オフを有する空隙)

【課題】配線用の導電体相互間のクロストークを減少した半導体装置を提供する。

【解決手段】半導体装置内に空洞を形成する方法が開示される。本発明の方法は、半導体装置のILD層内の空洞の内面上に核化防止層を付着することを含む。この核化防止層は、後に付着される誘電体層が空洞内に付着することを防止する。誘電体層が空洞内に付着することを防止することにより、キャパシタンスが減少され、これにより、改善された半導体動作特性を実現する。

(もっと読む)

半導体装置及びその作製方法

【課題】ソース電極又はドレイン電極の膜厚のばらつき又は断線を防止した半導体装置を容易に作製する方法を提案する。

【解決手段】絶縁基板上に形成された半導体層と、半導体層上に形成された第1の絶縁層と、第1の絶縁層上に形成されたゲート電極と、ゲート電極上に形成された第2の絶縁層と、を有し、少なくとも第1の絶縁層、及び第2の絶縁層に形成された半導体層に達する開口部と、前記開口部において前記第2の絶縁層の側面に形成された段差と、を有する。

(もっと読む)

161 - 180 / 404

[ Back to top ]